Une référence de tension sans résistance à faible puissance à l'échelle nanométrique avec un PSRR élevé

Résumé

Dans cet article, une référence de tension sous-seuil sans résistance nano-watt avec un rapport de réjection d'alimentation à haute puissance (PSRR) est présentée. Un diviseur de tension MOS auto-polarisé est proposé pour fournir un courant de polarisation pour toute la référence de tension, qui est un courant à coefficient de température positif (TC) contenant des caractéristiques de tension de seuil. En injectant le courant généré dans un transistor avec une tension de seuil différente, une tension de seuil delta avec un TC négatif considérablement réduit est réalisée et compensée en température par un élément TC positif généré en même temps. Par conséquent, une référence de tension stable en température est obtenue dans la méthode compactée proposée avec une faible consommation d'énergie et un PSRR élevé. Les résultats de la vérification avec la technologie CMOS 65 nm démontrent que la tension d'alimentation minimale peut être aussi basse que 0,35 V avec 0,00182 mm 2 zone active. La tension de référence générée est de 148 mV, avec un TC de 28 ppm/°C pour la plage de température de − 30 à 80 °C. La sensibilité de la ligne est de 1,8 mV/V, et le PSRR sans aucun condensateur de filtrage à 100 Hz est de 53 dB avec une consommation électrique de 2,28 nW.

Introduction

La référence de tension est l'un des modules de base des systèmes électroniques, qui est largement utilisé dans l'électronique médicale, la gestion de l'alimentation, les capteurs environnementaux sans fil et les circuits de communication. Alors que la tension d'alimentation des systèmes électroniques continue de diminuer avec l'amélioration de la technologie, les exigences pour une référence de tension de faible puissance avec la technologie à l'échelle nanométrique augmentent de manière critique [1, 2].

Les références de tension conventionnelles sont basées sur un circuit de référence de bande interdite (BGR), qui est une somme pondérée de V BE et la tension thermique [3, 4]. Cependant, en raison du comportement de température non linéaire de V BE , il est essentiel d'utiliser des approches de compensation de courbure pour améliorer la précision de BGR [5, 6]. Un autre inconvénient de BGR est la consommation d'énergie. Le V BE est d'environ 0,7 V sans rétrécissement avec l'amélioration du processus, ce qui restreint absolument la tension d'alimentation. Cela rend les BGR inadaptés aux applications basse tension et à l'échelle nanométrique.

Afin d'obtenir un fonctionnement à faible consommation, des références de tension inférieures au seuil MOS uniquement sont progressivement adoptées [7,8,9,10]. Comme les transistors dans une région d'inversion faible ont des avantages inhérents dans les applications à faible puissance avec un courant assez faible, la consommation d'énergie des références de tension relative peut être efficacement réduite. En outre, étant donné que les caractéristiques du transistor à effet de champ métal-oxyde-semiconducteur (MOSFET) sont compatibles avec l'amélioration des processus, la référence de tension basée sur le MOSFET est plus adaptable aux technologies avancées. De plus, l'utilisation de résistances doit également être évitée dans les applications à faible puissance. Étant donné que le courant dans la référence de tension est généralement inversement proportionnel à la valeur de résistance, une faible dissipation de puissance signifie des résistances à haute résistance [10], qui peuvent induire un bruit important occupant une grande surface de puce.

Le taux de réjection de l'alimentation (PSRR) est un autre paramètre important de la référence de tension. Les solutions conventionnelles pour améliorer le PSRR se font au détriment de la surface de la puce et de la consommation d'énergie, telles que des amplificateurs supplémentaires [11], des transistors à canal long [12], des structures cascode et un étage de gain supplémentaire [13].

Afin de surmonter les problèmes mentionnés ci-dessus, une référence de tension sous-seuil sans résistance à base de nano-watt MOSFET avec un PSRR élevé est proposée dans ce mémoire, qui convient aux technologies de pointe, telles que les processus à l'échelle nanométrique. Un diviseur de tension MOSFET auto-polarisé pour l'amélioration du PSRR est adopté dans la référence de tension proposée, qui peut générer un courant à coefficient de température positif (TC) contenant des caractéristiques de tension de seuil. Le courant sert de courants de polarisation pour toute la référence de tension. En outre, la tension de seuil intégrée dans le courant de polarisation est reproduite en injectant un courant de polarisation dans le MOSFET avec différentes tensions de seuil dans le papier. Avec la méthode proposée, une tension de seuil delta (∆V TH ) avec un TC négatif fortement réduit est obtenu. En outre, un élément pondéré proportionnel à la température absolue (PTAT) est également obtenu, tandis qu'une somme pondérée de ∆V TH et la tension PTAT est réalisée en même temps. En raison de l'annulation mutuelle de TC de deux tensions de seuil différentes, la tension PTAT requise peut être considérablement réduite pour la compensation de température. Par cette méthode, une référence de tension sans résistance MOSFET uniquement est obtenue par une structure compactée à faible consommation d'énergie.

Méthode

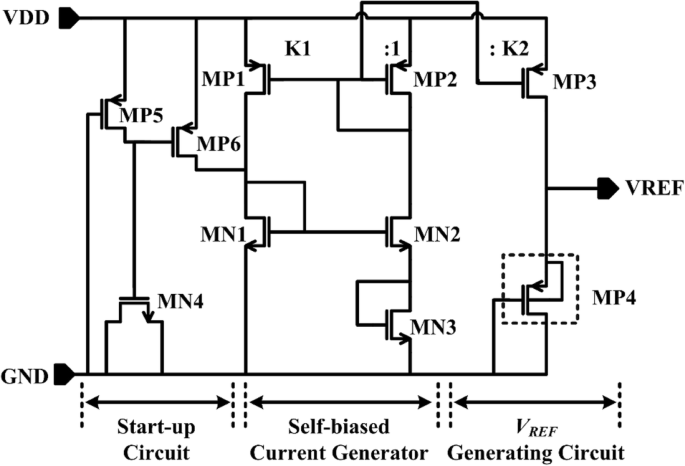

Comme le montre la figure 1, la référence de tension proposée est composée d'un circuit de démarrage, d'un générateur de courant auto-polarisé et d'un V REF circuit de génération. Tous les MOSFET à canal n sont des semi-conducteurs à oxyde métallique de type N à tension de seuil moyenne (mvt NMOS). MP4 est un transistor à haute tension de seuil de type P métal-oxyde-semi-conducteur (hvt PMOS), et les autres MOSFET à canal p sont un PMOS à tension de seuil moyenne (mvt PMOS). Tous les transistors illustrés à la figure 1 fonctionnent dans la région inférieure au seuil, à l'exception de ceux du circuit de démarrage.

Schéma de la référence de tension proposée

Circuit de démarrage

Le circuit de démarrage se compose de MP5, MP6 et MN4. Au début d'une étape de mise sous tension, le potentiel de grille de MP6 est bas et MP6 est activé. Le courant généré par MP6 fait monter le potentiel de grille de MN1 et MN2 et l'ensemble du circuit commence à fonctionner. En même temps, MP5 charge le condensateur de démarrage MN4. Avec la procédure de charge de MN4, le transistor MP6 est progressivement désactivé, ce qui éloigne le circuit de démarrage du noyau de la référence de tension proposée sans dissipation de puissance supplémentaire. Par cette méthode, la référence de tension proposée peut fonctionner dans un point de fonctionnement souhaité tout en évitant un point de dégénérescence.

Générateur de courant auto-biaisé

La partie médiane de la Fig. 1 est un générateur de courant auto-polarisé, qui est basé sur un diviseur de tension MOSFET uniquement. Le courant de polarisation avec TC positif pour l'ensemble de la référence de tension est généré dans cette partie, qui concerne la tension de seuil moyenne de NMOS. La caractéristique unique du courant de polarisation présenté est adoptée pour réaliser la référence de tension proposée de manière pratique, qui sera analysée dans la section "Méthode".

En ce qui concerne la caractéristique de courant de tension d'un transistor dans la région du sous-seuil, le courant de drain du transistor dans le sous-seuil devient presque indépendant de V DS avec V DS> 4V T , où V T = kT/q est la tension thermique, k est la constante de Boltzmann, q est la charge élémentaire, et T est la température absolue. Par conséquent, le courant peut être exprimé comme :

$$ {I}_{\mathrm{D}}={SI}_{\mathrm{SQ}}\exp \left(\frac{V_{\mathrm{GS}}-{V}_{\mathrm{ T}\mathrm{H}}}{mV_{\mathrm{T}}}\right) $$ (1)où S = W/L est le rapport hauteur/largeur, m est le facteur de pente sous le seuil, V TH est la tension de seuil, et I SQ représente le courant spécifique et est présenté par :

$$ {I}_{\mathrm{SQ}}=\mu {C}_{\mathrm{OX}}\left(m-1\right){V_T}^2 $$ (2)où μ est la mobilité du transporteur et C OX est la capacité d'oxyde par unité de surface.

Par conséquent, les courants à travers le diviseur de tension MOSFET uniquement, formé par MN1, MN2 et MN3, peuvent être exprimés comme suit :

$$ {I}_{\mathrm{D}\_\mathrm{MN}1}={S}_{\mathrm{MN}1}{I}_{\mathrm{SQN}}\exp \left( \frac{V_{\mathrm{GS}\_\mathrm{MN}1}-{V}_{\mathrm{T}\mathrm{HN}}}{mV_{\mathrm{T}}}\right) $$ (3) $$ {I}_{\mathrm{D}\_\mathrm{MN}2}={S}_{\mathrm{MN}2}{I}_{\mathrm{SQN}} \exp \left(\frac{V_{\mathrm{GS}\_\mathrm{MN}2}-{V}_{\mathrm{T}\mathrm{HN}}}{mV_{\mathrm{T} }}\right) $$ (4) $$ {I}_{\mathrm{D}\_\mathrm{MN}3}={S}_{\mathrm{MN}3}{I}_{\ mathrm{SQN}}\exp \left(\frac{V_{\mathrm{GS}\_\mathrm{MN}3}-{V}_{\mathrm{T}\mathrm{HN}}}{mV_{ \mathrm{T}}}\right) $$ (5)où je SQN est le courant spécifique de NMOS et V THN est la tension de seuil de NMOS.

Étant donné que les proportions de MN2 et MN3 sont les mêmes et I D_MN2 = I D_MN3 , V GS_MN2 = V GS_MN3 est garanti. Cela fait V GS_MN1 = 2V GS_MN2 . Par ailleurs, les transistors PMOS forment les miroirs de courant et définissent les rapports de courant K 1 = S MP1 /S MP2 et K 2 = S MP3 /S MP2 . La relation des courants de drain entre MN1 et MN2 peut être exprimée par :

$$ {I}_{\mathrm{D}\_\mathrm{MN}1}={K}_1{I}_{\mathrm{D}\_\mathrm{MN}2} $$ (6)Combiné avec les équations. (3)–(6), le V GS_MN2 et Je D_MN2 peut être donné par :

$$ {V}_{\mathrm{GS}\_\mathrm{MN}2}={mV}_{\mathrm{T}}\ln \left(\frac{K_1{S}_{\mathrm{ MN}2}}{S_{\mathrm{MN}1}}\right) $$ (7) $$ {I}_{\mathrm{D}\_\mathrm{MN}2}={S}_ {\mathrm{MN}2}{I}_{\mathrm{SQN}}\exp \left(\ln \frac{K_1{S}_{\mathrm{MN}2}}{S_{\mathrm{MN }1}}-\frac{V_{\mathrm{T}\mathrm{HN}}}{mV_{\mathrm{T}}}\right) $$ (8)Pour la commodité de l'analyse, l'Eq. (8) peut être abrégé en :

$$ {I}_{\mathrm{D}\_\mathrm{MN}2}={aT}^{2-{n}_1}\exp \left(b-\frac{V_{\mathrm{T }\mathrm{HN}}}{mV_{\mathrm{T}}}\right) $$ (9)où a = S MN2 μ n 0 C OX (m − 1)(k/q ) 2 et b = ln(K 1 S MN2 /S MN1 ) sont indépendants de la température, μ n 0 est un facteur indépendant de la température de la mobilité du porteur, et n 1 est le terme exposant de température absolue de la mobilité du porteur, qui est généralement d'environ 1,5.

Comme le montre l'éq. (9), tension de seuil V THN est complémentaire de la température absolue (CTAT), tandis que la tension thermique V T est proportionnel à la température absolue (PTAT). Lorsque la température augmente, V THN /(mV T ) réduira, de sorte que les caractéristiques de courant positives du courant de polarisation seront améliorées.

Par cette méthode, un courant de polarisation TC positif est obtenu par une structure MOSFET uniquement, qui porte les caractéristiques de la tension de seuil NMOS.

V REF Circuit de génération

Le V REF Le circuit de génération est illustré dans la partie droite de la figure 1, qui n'est formé que de deux transistors, MP3 et MP4. En raison de l'opération de région sous-seuil, I D_MP4 peut être écrit comme :

$$ {I}_{\mathrm{D}\_\mathrm{MP}4}={S}_{\mathrm{MN}4}{I}_{\mathrm{SQP}}\exp \left( \frac{\mid {V}_{\mathrm{GS}\_\mathrm{MP}4}\mid -\mid {V}_{\mathrm{T}\mathrm{HP}}\mid }{mV_ {\mathrm{T}}}\right) $$ (10)où je SQP est le courant spécifique de PMOS et V THP est le V TH de PMOS.

Depuis Je D_MP4 = K 2 Je D_MN2 , les caractéristiques de la tension de seuil NMOS, V THN , peut être transféré au nœud de sortie et être superposé avec les caractéristiques de la tension de seuil PMOS, V THP . À partir des équations. (8) et (10), V REF peut être écrit comme :

$$ {V}_{\mathrm{REF}}=\mid {V}_{\mathrm{T}\mathrm{HP}}\mid -{V}_{\mathrm{T}\mathrm{HN} }+{mV}_{\mathrm{T}}\ln \left(\frac{K_2{S}_{\mathrm{MN}2}{I}_{\mathrm{SQn}}}{S_{\ mathrm{MP}4}{I}_{\mathrm{SQP}}}\right)+{mV}_{\mathrm{T}}\ln \left(\frac{K_1{S}_{\mathrm{ MN}2}}{S_{\mathrm{MN}1}}\right) $$ (11)Comme le montrent les deux premiers éléments de l'équation. (11), une tension de seuil delta est réalisée. Depuis le V TH = V TH0 − βT , où V TH0 est la tension de seuil à 0 K et β est le TC de la tension de seuil, la tension de seuil delta générée est une tension complémentaire à la température absolue (CTAT) avec un TC fortement rétréci avec |βV THP |> βV THN . En outre, deux tensions PTAT supplémentaires sont simultanément réalisées et montrées dans les deux derniers éléments de l'Eq. (11), qui sont adoptés pour annuler le TC réduit de la tension de seuil delta. Par conséquent, une tension de référence compactée et stable en température est obtenue sans structure compliquée, qui est stable à |V THP0 | − V THN0 .

Sur la base de l'analyse précédente, une référence de tension MOSFET de faible puissance uniquement est réalisée dans cet article qui ne nécessite que trois branches dans le noyau. Avec les caractéristiques uniques d'une source de courant auto-polarisée, un PMOS connecté par diode est adopté pour obtenir une tension CTAT avec un TC rétréci, un générateur de tension PTAT et une sommation pondérée en même temps. De plus, la structure proposée n'est construite que par des MOSFET et la tension de référence générée est proportionnelle à la tension de seuil delta. Par conséquent, la référence de tension proposée est plus adaptée aux applications à faible consommation d'énergie avec la technologie nanométrique, qui peut être étendue à des technologies plus avancées.

PSRR de la référence de tension proposée

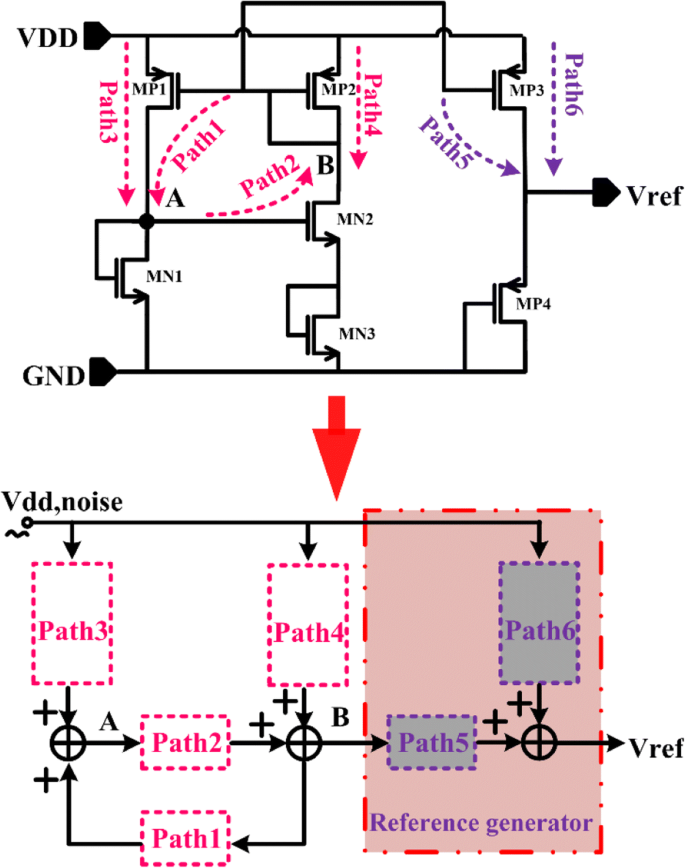

Afin d'illustrer les performances du PSRR, les chemins du bruit de la tension d'alimentation à V REF et les diagrammes fonctionnels équivalents correspondants sont illustrés à la Fig. 2.

Les chemins du bruit de la tension d'alimentation

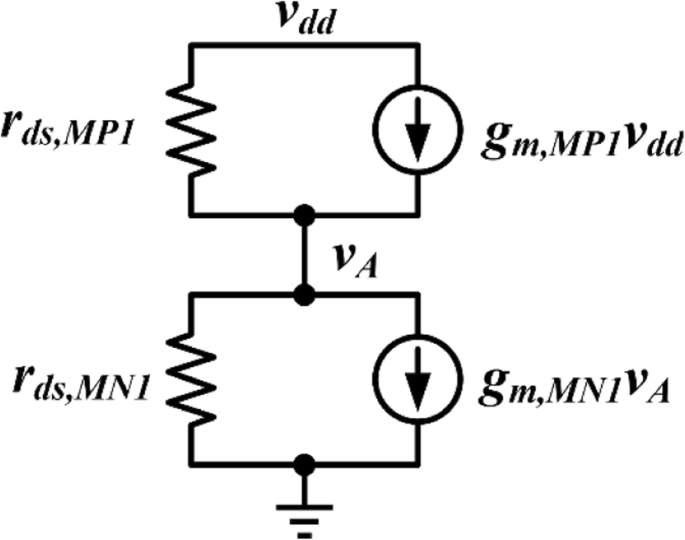

Sur la base de la figure 2, le modèle à petits signaux du chemin 3 est illustré à la figure 3, et l'équation suivante peut être obtenue :

$$ \frac{v_{\mathrm{dd}}-{v}_{\mathrm{A}}}{r_{\mathrm{ds},\mathrm{MP}1}}+{g}_{\ mathrm{m},\mathrm{MP}1}{v}_{\mathrm{dd}}=\frac{v_{\mathrm{A}}}{r_{\mathrm{ds},\mathrm{MN} 1}}+{g}_{\mathrm{m},\mathrm{MN}1}{v}_{\mathrm{A}} $$ (12)

Petit modèle de signal du chemin 3

De l'éq. (12), l'expression du bruit d'alimentation par le chemin 3 jusqu'au nœud A peut être donnée par :

$$ {Av}_{\mathrm{chemin}3}=\frac{v_{\mathrm{A}}}{v_{\mathrm{dd}}}=\frac{r_{\mathrm{ds},\ mathrm{MN}1}+{g}_{\mathrm{m},\mathrm{MP}1}{r}_{\mathrm{ds},\mathrm{MN}1}{r}_{\mathrm {ds},\mathrm{MP}1}}{r_{\mathrm{ds},\mathrm{MP}1}+{r}_{\mathrm{ds},\mathrm{MN}1}+{g }_{\mathrm{m},\mathrm{MN}1}{r}_{\mathrm{ds},\mathrm{MN}1}{r}_{\mathrm{ds},\mathrm{MP} 1}} $$ (13)La transconductance du transistor fonctionnant dans la région inférieure au seuil est g m = Je D /mV T . Par conséquent, la relation entre g m,MP1 et g m,MN1 avec le même courant peut être donné comme g m,MP1 = g m,MN1 . Ensuite, l'éq. (13) peut être simplifié ainsi :

$$ {Av}_{\mathrm{chemin}3}\environ 1 $$ (14)Le nœud B a également un effet sur le nœud A via le chemin 1, mais l'effet est opposé au chemin 3, qui peut être exprimé par :

$$ {Av}_{\mathrm{chemin}1}\environ -1 $$ (15)Pour V A = 2V GS,MN2 , le gain du chemin 2 est donné par :

$$ {Av}_{\mathrm{path}2}=-\frac{1}{2}{g}_{\mathrm{m},\mathrm{MN}2}\left(2{r}_ {\mathrm{ds},\mathrm{MN}2}\Big\Vert \frac{1}{g_{\mathrm{m},\mathrm{MP}2}}\right)\approx -\frac{1 }{2} $$ (16)L'effet de v jj sur le nœud B via le chemin 4 peut être écrit comme :

$$ {Av}_{\mathrm{chemin}4}=\frac{2{r}_{\mathrm{ds},\mathrm{MN}2}}{\left(1/{g}_{\ mathrm{m},\mathrm{MP}2}\right)+2{r}_{\mathrm{ds},\mathrm{MN}2}}=\frac{2{g}_{\mathrm{m },\mathrm{MP}2}{r}_{\mathrm{ds},\mathrm{MN}2}}{1+2{g}_{\mathrm{m},\mathrm{MP}2} {r}_{\mathrm{ds},\mathrm{MN}2}} $$ (17)Du nœud A au nœud B de la figure 2, deux équations supplémentaires peuvent être obtenues :

$$ {Av}_{\mathrm{chemin}4}{v}_{\mathrm{dd}}+{Av}_{\mathrm{chemin}2}{V}_{\mathrm{A}}={V}_{\mathrm{B}} $$ (18) $$ {Av}_{\mathrm{path}3}{v}_{\mathrm{dd}}+{Av}_{\mathrm{ chemin}1}{V}_{\mathrm{B}}={V}_{\mathrm{A}} $$ (19)D'après les équations (18) et (19), le bruit à V B peut être donné par :

$$ {V}_{\mathrm{B}}=\frac{2{g}_{\mathrm{m},\mathrm{MP}2}{r}_{\mathrm{ds},\mathrm{ MN}2}-1}{1+2{g}_{\mathrm{m},\mathrm{MP}2}{r}_{\mathrm{ds},\mathrm{MN}2}}{v }_{\mathrm{dd}}\approx {v}_{\mathrm{dd}} $$ (20)À l'aide de la source de courant auto-polarisée proposée, le nœud de sortie de la partie générateur de courant, B, peut suivre la variation de petit signal de la tension d'alimentation, ce qui est bénéfique pour l'amélioration du PSRR de l'ensemble de la référence de tension.

Avec une méthode similaire, les gains de bruit d'alimentation du chemin 5 et du chemin 6 peuvent être présentés par les équations. (21) et (22), respectivement :

$$ {Av}_{\mathrm{chemin}5}={g}_{\mathrm{m},\mathrm{MP}3}\left({r}_{\mathrm{ds},\mathrm{ MP}3}\Big\Vert \frac{1}{g_{\mathrm{m},\mathrm{MP}4}}\right) $$ (21) $$ {Av}_{\mathrm{path} 6}\environ 1 $$ (22)Tenant compte de la relation de connexion du chemin de bruit du générateur de référence illustré à la Fig. 2, l'effet du bruit d'alimentation à la tension de référence, V REF , peut être déterminé par le chemin 5 et le chemin 6 :

$$ {v}_{\mathrm{REF}}={Av}_{\mathrm{chemin}5}{V}_{\mathrm{B}}+{Av}_{\mathrm{chemin}6} {v}_{\mathrm{dd}}=\frac{1}{1+{g}_{\mathrm{m},\mathrm{MP}4}{r}_{\mathrm{ds},\ mathrm{MP}3}}{v}_{\mathrm{dd}}=\frac{1}{1+\frac{\exp \left({V}_{\mathrm{DS},\mathrm{MP }3}/{V}_{\mathrm{T}}\right)-1}{m}}{v}_{\mathrm{dd}} $$ (23)Pour V DS> 4V T , le terme exponentiel dans l'équation. (23) est très grand. Cela rend les performances PSRR considérablement améliorées avec V DS,MP3 en augmentant. Dans la conception proposée, le V minimum DS,MP3 est supérieur à 200 mV, ce qui signifie que le changement de la tension d'alimentation a peu d'effet sur le V REF . Ainsi, la structure proposée a une bonne performance PSRR.

Résultats et discussion

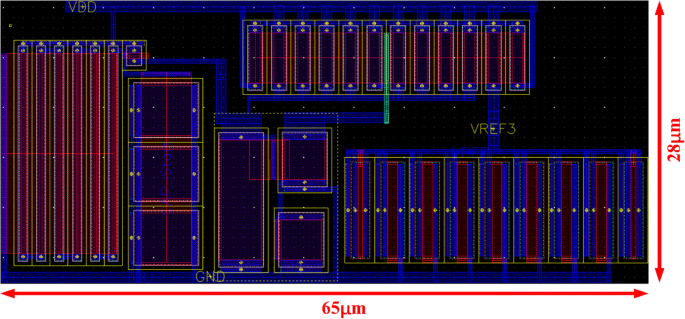

La référence de tension est implémentée dans un processus CMOS de 65 nm, dont la disposition est illustrée à la Fig. 4 occupant un 0,00182 mm 2 zone active.

Tracé du circuit proposé

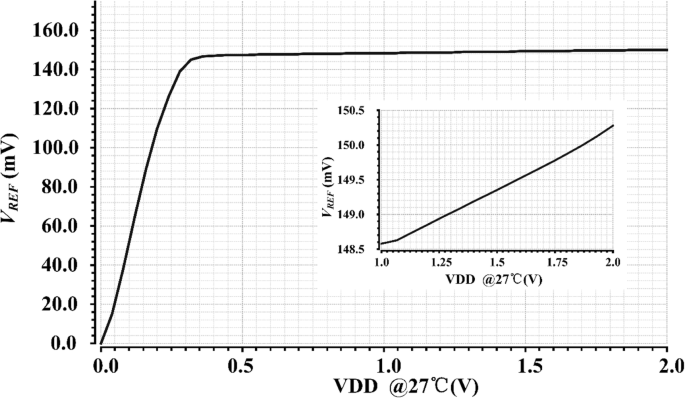

La figure 5 montre la régulation de ligne de la référence de tension proposée à 27 °C. Comme le montre la Fig. 5, la tension d'alimentation minimale peut être aussi faible que 350 mV, et la tension de référence générée, V REF , est d'environ 148 mV. La sensibilité de ligne (LS) est de 1,8 mV/V.

Forme d'onde de V REF par rapport à la tension d'alimentation

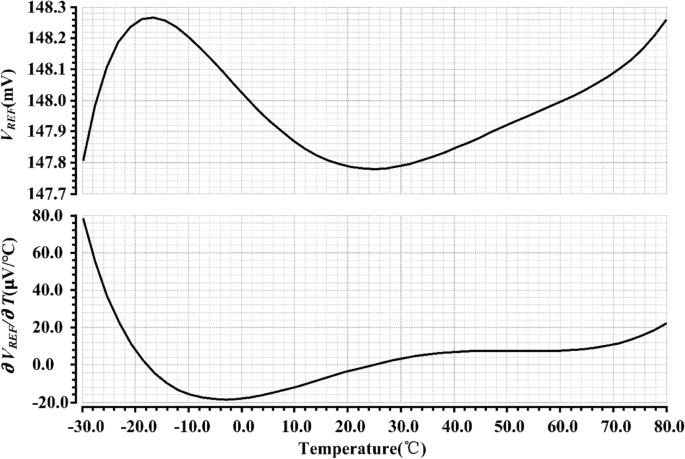

Les performances de température de V REF avec une tension d'alimentation de 350 mV est illustré à la Fig. 6. Le TC de V REF est de 28 ppm/°C de − 30 à 80 °C. V REF montre des caractéristiques de température positives en dessous de − 15 °C et au-dessus de 25 °C, tandis que des caractéristiques de température négatives dans la région de température moyenne.

Dépendance à la température de V REF

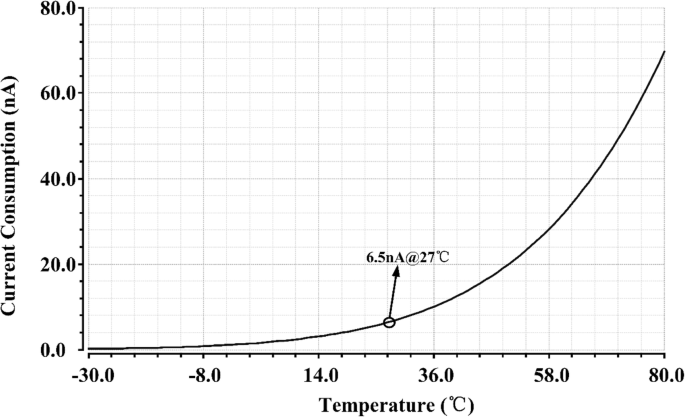

La figure 7 montre la consommation de courant en fonction de la température avec une tension d'alimentation de 350 mV. Le courant montre un TC positif. La consommation électrique à température ambiante est d'environ 2,28 nW.

Consommation actuelle en fonction de la température

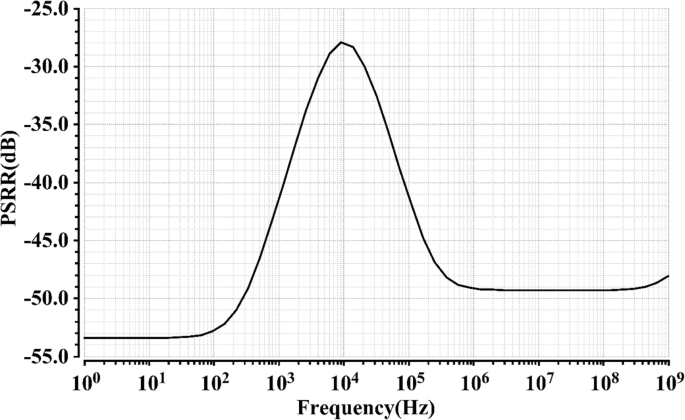

La figure 8 montre le résultat du PSRR à 27 °C avec une tension d'alimentation de 350 mV, où le PSRR sans aucun condensateur de filtre de sortie est supérieur à 53 dB jusqu'à 100 Hz. Comme mentionné ci-dessus, les performances du PSRR peuvent être encore améliorées avec une augmentation de la tension d'alimentation, ce qui signifie que le PSRR illustré à la Fig. 8 est le pire des cas de la référence de tension proposée.

PSRR de référence de tension proposée

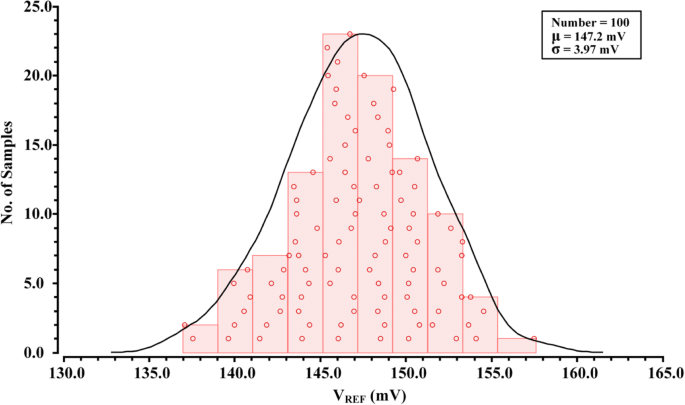

Les distributions de V non rogné REF à 27 °C avec 100 échantillons est illustré à la Fig. 9. La valeur moyenne et l'écart type du V REF est respectivement de 147 mV et 3,97 mV, ce qui donne un écart (σ/μ) de 2,7 %.

Distributions de V non rogné REF

Le tableau 1 résume les caractéristiques de la référence de tension proposée et la compare à certaines références de tension signalées précédemment.

Conclusion

Une référence de tension de faible puissance sans résistance avec un PSRR élevé est présentée dans cet article, qui convient aux applications à l'échelle nanométrique et peut être étendue à un processus plus avancé. À l'aide d'une source de courant auto-polarisée basée sur un diviseur de tension MOSFET, la tension CTAT requise, la tension PTAT et la sommation pondérée peuvent être réalisées simultanément dans une structure compactée. De plus, une tension de seuil delta est choisie comme tension CTAT, qui a un TC négatif considérablement réduit. Cela réduit également la valeur requise de la tension PTAT. Par conséquent, la tension d'alimentation et la consommation de courant peuvent être réduites. Toutes les pièces ne sont construites que par des MOSFET, ce qui a la priorité dans les applications hautement intégrées sensibles à la puissance, telles que SOC.

Abréviations

- BGR :

-

Référence de bande interdite

- CTAT :

-

Complémentaire à la température absolue

- hvt :

-

Tension de seuil élevée

- LS :

-

Sensibilité de ligne

- mvt :

-

Tension de seuil moyenne

- PSRR :

-

Taux de réjection de l'alimentation

- PTAT :

-

Proportionnel à la température absolue

- TC :

-

Coefficient de température

Nanomatériaux

- Ohmmètres haute tension

- Quelques exemples avec des circuits CA

- ST :régulateur à découpage avec de larges plages de tension

- Impression 3D haute vitesse avec AFPM

- Impression 3D haute vitesse avec AION500MK3

- Fabrication de fosses à l'échelle nanométrique avec un débit élevé sur une couche mince de polymère à l'aide de la lithographie dynamique à base de pointes AFM

- Convertisseur de polarisation avec biréfringence contrôlable basé sur une métasurface hybride entièrement diélectrique-graphène

- Résoudre les problèmes de panne d'alimentation haute tension

- Matériaux et conception de PCB pour haute tension