Débuts des puces d'IA neuromorphiques pour le renforcement des réseaux de neurones

Innatera, la startup néerlandaise qui fabrique des accélérateurs d'IA neuromorphique pour le renforcement des réseaux de neurones , a produit ses premières puces, évalué leurs performances et révélé les détails de leur architecture.

Innatera, la startup néerlandaise fabriquant des accélérateurs d'IA neuromorphiques pour les réseaux de neurones dopés, a produit ses premières puces, évalué leurs performances et révélé les détails de leur architecture.

La société a également annoncé que le co-fondateur de Cadence et Synopsys, Alberto Sangiovanni-Vincentelli, a rejoint la société en tant que président de son conseil d'administration. Le vétéran de l'industrie est actuellement professeur à l'Université de Californie à Berkeley.

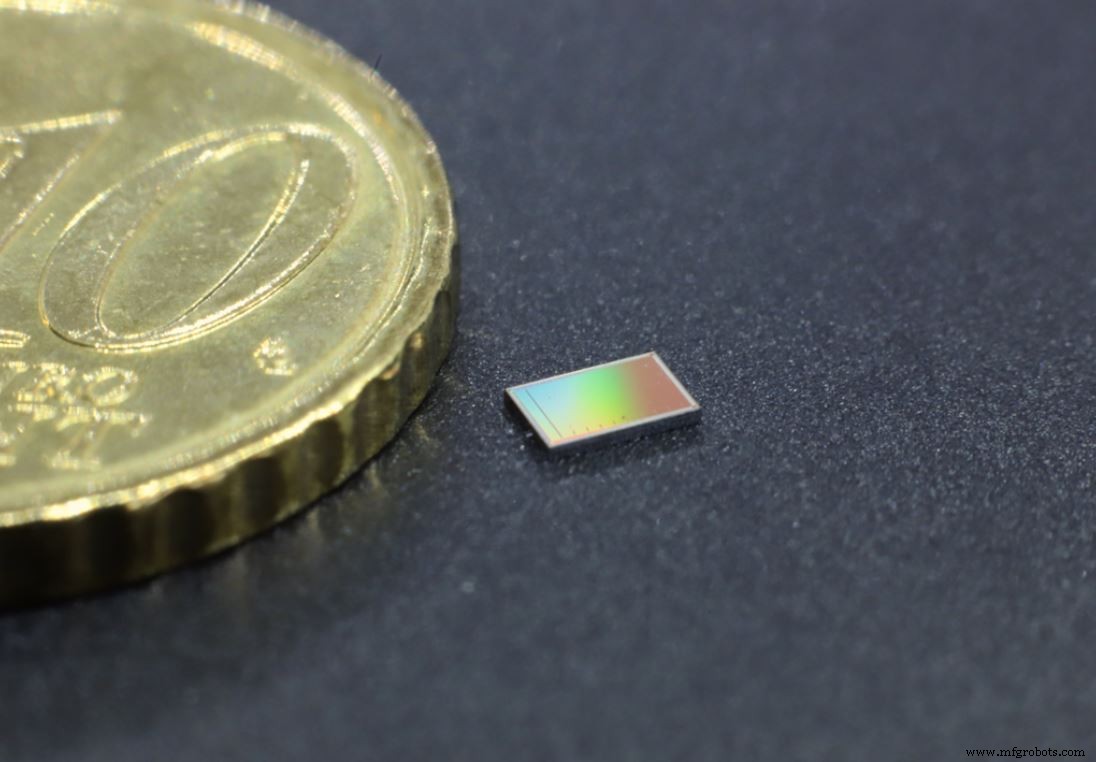

La puce d'Innatera est conçue pour accélérer différents SNN pour les applications audio, de santé et de radar (Image :Innatera)

La puce Innatera est conçue pour accélérer les réseaux de neurones à pointes (SNN), un type d'algorithme d'IA neuromorphique basé sur la biologie du cerveau qui utilise la synchronisation des pointes dans un signal électrique pour effectuer des tâches de reconnaissance de formes. Les SNN ont une structure complètement différente des algorithmes d'IA traditionnels et nécessitent donc un matériel dédié pour l'accélération, mais ils offrent généralement des avantages significatifs en termes de consommation d'énergie et de latence pour les applications de bord de capteur.

La plupart des autres entreprises travaillant sur des algorithmes et du matériel de réseau neuronal de pointe (par exemple, Prophesee) ciblent les images et les flux vidéo. Innatera a décidé de se concentrer sur l'audio (reconnaissance sonore et vocale), la santé (surveillance des signes vitaux) et le radar (pour les cas d'utilisation grand public/IoT tels que les capteurs de chute de personnes âgées qui préservent la confidentialité).

Marco Jacobs (Image :Innatera)

"Ces capteurs ont des données de séries temporelles, au lieu d'images qui sont très parallèles", a déclaré Marco Jacobs, vice-président du marketing et du développement commercial d'Innatera, dans une interview avec EE Times . « Notre baie est particulièrement efficace pour traiter les données de séries chronologiques… c'est un bon ajustement technologique. De plus, du point de vue du marché, nous voyons beaucoup d'applications intéressantes dans ce domaine et peu de solutions qui y répondent. »

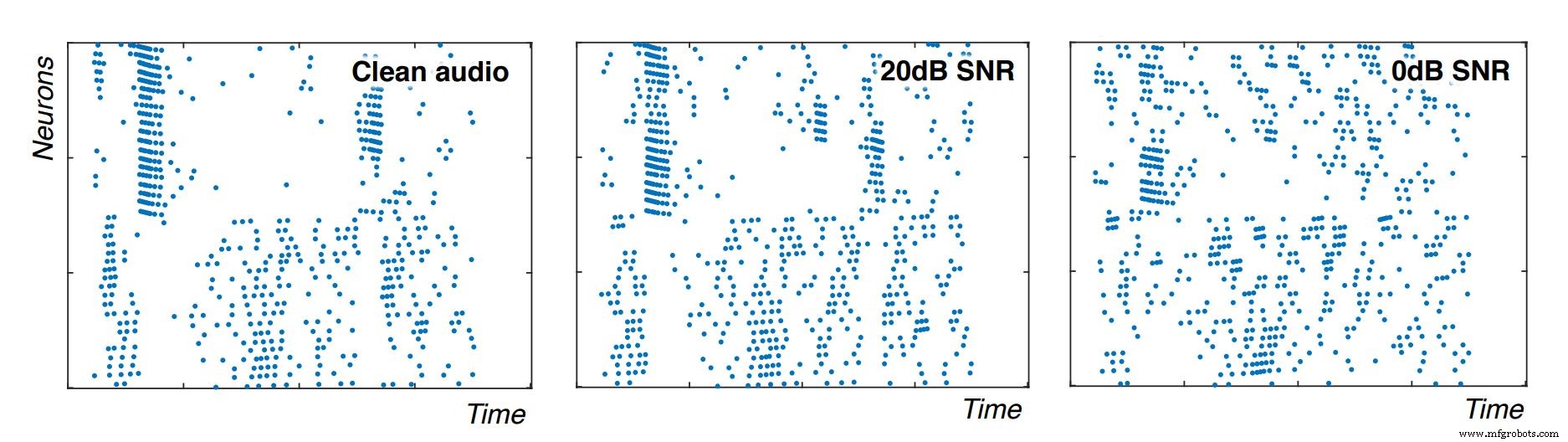

Une autre chose que ces trois applications ont en commun est que puisque le traitement est requis dans le nœud de capteur, l'enveloppe de puissance est très serrée. Dans les tests d'Innatera, chaque événement de pointe (chaque neurone déclenché en réponse aux données d'entrée) nécessitait moins d'un picoJoule d'énergie - en fait, moins de 200 femtoJoules en TSMC 28 nm, a confirmé Innatera. Cela approche la quantité d'énergie utilisée par les neurones biologiques et les synapses. Selon le PDG d'Innatera, Sumeet Kumar, une application typique de détection de mots-clés audio nécessitait moins de 500 pics d'événements par inférence, entraînant une "dissipation de puissance profonde inférieure au milliwatt". Dans ce cas, des grappes de neurones s'activant ensemble représentent différents phonèmes de la parole.

Les clusters de neurones activés (groupes de points ici) représentent la détection de phonèmes dans la parole. Comme les données d'entrée incorporent plus de bruit, les mêmes clusters sont pour la plupart présents, bien qu'ils soient plus difficiles à repérer (Image :Innatera)

Architecture de traitement

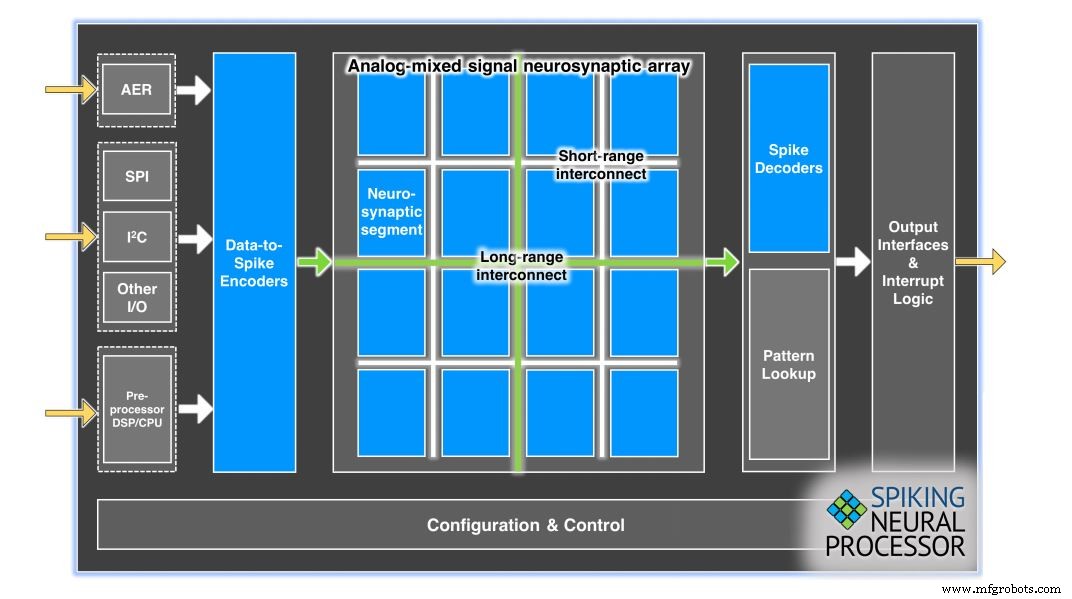

Le processeur neuronal à pics d'Innatera utilise un réseau parallèle de neurones et de synapses à pics pour accélérer les SNN en temps continu avec une dynamique temporelle à grain fin. L'appareil est un accélérateur de signaux analogiques/mixtes conçu pour tirer parti de la capacité de SNN à intégrer la notion de temps dans la façon dont les données sont traitées.

Le processeur neuronal à pointes d'Innatera comprend un réseau neuro-synaptique massivement parallèle et des encodeurs et décodeurs de pointes (Image :Innatera)

L'un des aspects clés des structures de calcul d'Innatera est sa programmabilité, qui est importante pour deux raisons.

Tout d'abord, programmer différents SNN sur la puce. Les neurones doivent être connectés de manière flexible :le cerveau utilise des topologies de réseaux neuronaux très complexes pour faire les choses efficacement, ce qui nécessite des connexions complexes entre les neurones, qui doivent être recréées dans du silicium.

Sumeet Kumar (Image :Innatera)

Deuxièmement, pour optimiser les performances. Plutôt que de représenter les informations sous forme de bits dans des mots, dans un SNN, les informations sont représentées sous forme de pointes chronométrées avec précision. Le timing des pics doit être manipulé à un niveau très fin pour extraire des informations sur les données. Les neurones et les connexions entre eux (les synapses) doivent donc présenter des comportements de synchronisation complexes. Ces comportements peuvent être ajustés via le SDK d'Innatera pour optimiser les performances.

Innatera décrit sa puce comme un signal mixte analogique ou « analogique à assistance numérique ». Les neurones et les synapses sont implémentés dans du silicium analogique pour maintenir une consommation d'énergie ultra-faible. L'électronique analogique permet également des réseaux à temps continu (l'électronique numérique nécessiterait une discrétisation). Ceci est important pour les SNN, car leur nature signifie qu'ils ont intrinsèquement une notion du temps et doivent être capables de conserver des états particuliers sur une période de temps.

"Cela est beaucoup plus facile dans le domaine analogique - vous n'avez pas à déplacer la complexité de la conservation de l'état dans la topologie du réseau", a déclaré Kumar. «Nos éléments de calcul conservent naturellement ces informations d'état. C'est la raison pour laquelle nous faisons des choses dans le domaine analogique. »

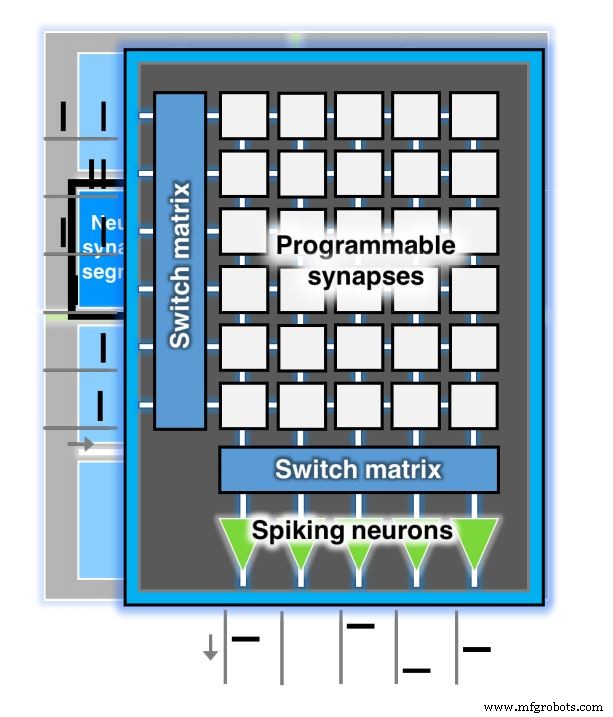

Un segment de calcul dans la matrice d'Innatera, où les neurones sont conçus pour être soigneusement appariés. Les synapses programmables sont arrangées dans une structure de barre transversale à plusieurs niveaux. (Les lignes/traits noirs représentent ici les pics d'entrée et de sortie) (Image :Innatera)

Des incohérences mineures dans la fabrication entre les éléments de calcul sur la puce et entre les différentes puces peuvent être un problème pour la mise en œuvre précise des réseaux de neurones dans le domaine analogique. La solution d'Innatera consiste à regrouper les neurones en ce qu'il appelle des segments, qui sont soigneusement conçus pour correspondre aux longueurs de chemin et au nombre de neurones.

La conception du segment "nous permet essentiellement d'utiliser le meilleur des circuits analogiques tout en minimisant ces non-idéalités que vous auriez généralement dans un circuit analogique", a déclaré Kumar. "Tout cela a été essentiellement fait pour s'assurer que les neurones à l'intérieur d'un segment présentent un comportement déterministe et qu'ils fonctionnent d'une manière similaire à leurs voisins immédiats."

Des incohérences entre différentes puces peuvent causer des problèmes lorsque le même réseau formé est déployé sur des appareils sur le terrain. Innatera contourne ce problème avec un logiciel.

"L'inadéquation et la variabilité sont traitées en profondeur dans le SDK", a déclaré Kumar. "Si vous êtes un utilisateur expérimenté, nous pouvons vous en exposer une partie, mais un programmeur typique n'a pas besoin de s'en soucier."

Spécifique à l'application

Innatera, une entreprise dérivée de l'Université de technologie de Delft, travaillait déjà avec des clients commerciaux sur ses algorithmes SNN avant de passer au matériel et de lever un tour de table de 5 millions d'euros (environ 6 millions de dollars) vers la fin de 2020.

"Nous travaillons avec un certain nombre de clients depuis le moment où nous avons réellement créé l'entreprise, et ces engagements sont toujours en cours - ils ont mûri de manière très significative", a déclaré Kumar. "Nous espérons être en mesure de montrer plus de démonstrations avec certains de ces clients dans la dernière partie de cette année."

Kumar a déclaré que la société maintient son objectif en tant que société de solutions informatiques, c'est-à-dire qu'elle fournira des solutions clé en main qui incluent à la fois du matériel et des algorithmes SNN spécifiques aux applications.

La première puce d'Innatera est adaptée aux applications audio, santé et radar. La feuille de route de l'entreprise pourrait inclure des puces optimisées supplémentaires pour chacune des applications.

"Nous avons conçu l'appareil de manière à pouvoir accélérer une grande variété de réseaux de neurones à pics", a déclaré Kumar. « [Notre puce] peut implémenter ces réseaux dans tous les domaines d'application. Mais au fur et à mesure que nous approfondissons les domaines, il peut être nécessaire d'optimiser la conception du matériel, et c'est quelque chose que nous examinerons à l'avenir. À l'heure actuelle, le matériel n'est pas trop spécialisé pour une classe d'applications spécifique ou un style de réseaux de neurones à pics, l'objectif est de prendre en charge une variété d'entre eux généralement à l'intérieur de l'architecture. »

Des échantillons de la puce initiale sont en passe d'être disponibles avant la fin de 2021.

>> Cet article a été initialement publié sur notre site frère, EE Fois.

Contenus associés :

- La puce IA cible les appareils de périphérie à faible consommation

- La chaîne d'outils et la carte de capteur améliorent l'écosystème des puces d'IA

- Les nouveaux modules d'accélération de l'IA améliorent les performances de pointe

- L'IA à la limite :que rechercher en 2021

- Comment mettre en œuvre l'IA des objets (AIoT) sur les MCU

Pour plus d'informations sur Embedded, abonnez-vous à la newsletter hebdomadaire d'Embedded.

Embarqué

- Co-simulation pour les conceptions basées sur Zynq

- Renesas :puces automobiles adoptées par Nissan pour sa nouvelle Skyline ProPILOT 2.0

- CEVA :processeur IA de deuxième génération pour les charges de travail des réseaux de neurones profonds

- Présentation des arguments en faveur des puces neuromorphiques pour l'IA informatique

- La puce radar de faible puissance utilise des réseaux de neurones à pointes

- Lanner :passerelle périphérique compatible LTE certifiée pour l'IoT et le SD-WAN sur les réseaux cellulaires

- IBM chez SPIE :sept avancées pour les puces au-delà de 7 nm

- NPE fait ses débuts aux États-Unis pour Campetella Robotic Center

- La 3G est morte :quel avenir pour les concepteurs de produits ?