Déterminisme de phase de mise sous tension :synthétiseur PLL et étalonnage au niveau du système

Dans la première partie de cette série d'articles, nous avons exploré comment obtenir des phases (déterministes) connues pour tous les canaux dans les puces intégrées avec plusieurs blocs de traitement du signal numérique (DSP), des convertisseurs numérique-analogique à large bande (DAC) et analogiques à large bande. -convertisseurs numériques (CAN). Nous avons commencé avec un schéma fonctionnel de système de haut niveau utilisant une structure arborescente d'horloges de sous-tableau et avons décrit une méthode de synchronisation multipuce. Dans cette deuxième partie, nous explorerons les ajustements de phase du synthétiseur PLL, l'évolutivité vers plusieurs sous-réseaux et les algorithmes d'étalonnage au niveau du système.

Ajustements de phase du synthétiseur PLL

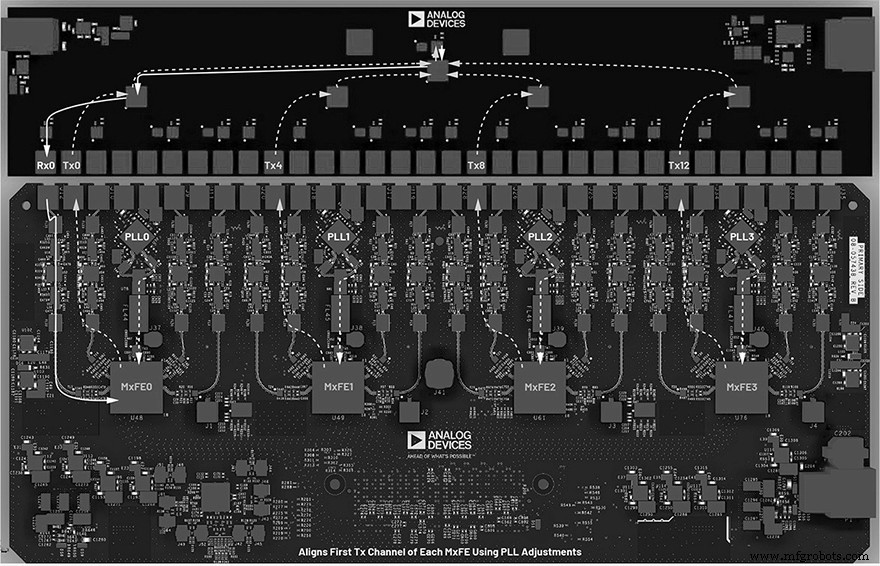

Les circuits intégrés de synthétiseur PLL choisis ont été sélectionnés pour permettre des ajustements de phase d'horloge d'échantillonnage relatifs injectés dans chaque circuit intégré de numériseur. La dérive thermique, et la dérive de phase PLL qui en résulte entre l'horloge d'échantillonnage et le SYSREF de chaque CI, est compensée en créant un mécanisme de rétroaction qui garantit que le premier canal de transmission de chaque CI de numériseur est aligné en phase sur le premier canal de transmission du premier CI de numériseur. Pour réaliser cette boucle de rétroaction, le premier canal de transmission de chaque circuit intégré émet un signal qui se différencie des autres canaux de transmission, comme le montre la figure 1. Ces quatre signaux sont combinés et envoyés dans un récepteur commun, qui pour ce système est étiqueté Rx0 .

cliquez pour l'image en taille réelle

Figure 1. Une fonction de réglage de phase du synthétiseur PLL permet d'aligner le premier canal de transmission de chaque circuit intégré de numériseur sur le sous-réseau. (Source :Appareils analogiques)

Des données de réception simultanées sont obtenues pour tous les canaux de réception, ce qui permet ensuite aux utilisateurs d'appliquer des techniques de corrélation croisée et de déterminer les décalages de phase complexes entre ces quatre canaux de transmission, TxOffset . Les circuits intégrés du synthétiseur PLL contiennent en leur sein un oscillateur commandé en tension (VCO) qui fonctionne à une fréquence ƒ VCO_PLL .

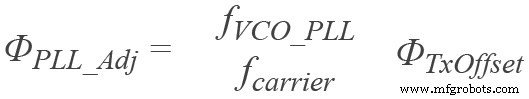

Les déphasages mesurés ΦTxOffset sont alors liés au réglage de phase PLL requis ΦPLL_Adj et la fréquence RF ƒ transporteur tel que :

En utilisant cette formule, les phases du synthétiseur PLL peuvent être ajustées d'une nouvelle quantité connue pour établir une ligne de base de transmission commune entre tous les circuits intégrés de numériseur pour tous les cycles d'alimentation, comme illustré à la figure 2. Les cercles ouverts pour chaque canal illustré à la figure 2 correspondent aux premier cycle d'alimentation, tandis que tous les autres points pleins correspondent aux cycles d'alimentation suivants. Comme on peut le voir sur cette figure, les décalages de phase d'émission calibrés pour les premier (et deuxième) canalisateurs de tous les circuits intégrés de numériseur sont alignés en phase. Le deuxième canaliseur de chaque circuit intégré de numériseur est également aligné dans ce cas, car deux canaux sont utilisés pour chaque DAC du système.

L'ajout de cette étape d'ajustement de phase du synthétiseur PLL avant les routines MCS discutées dans la section précédente crée ainsi une phase déterministe sur tous les gradients thermiques induits au sein du système en forçant le système à la même relation de phase horloge d'échantillon-SYSREF, qui se manifeste comme une transmission ligne de base d'alignement sur tous les circuits intégrés de numériseur.

cliquez pour l'image en taille réelle

Figure 2. En ajustant la phase PLL, l'utilisateur peut aligner le premier canal de transmission de tous les circuits intégrés de numériseur. (Source :Appareils analogiques)

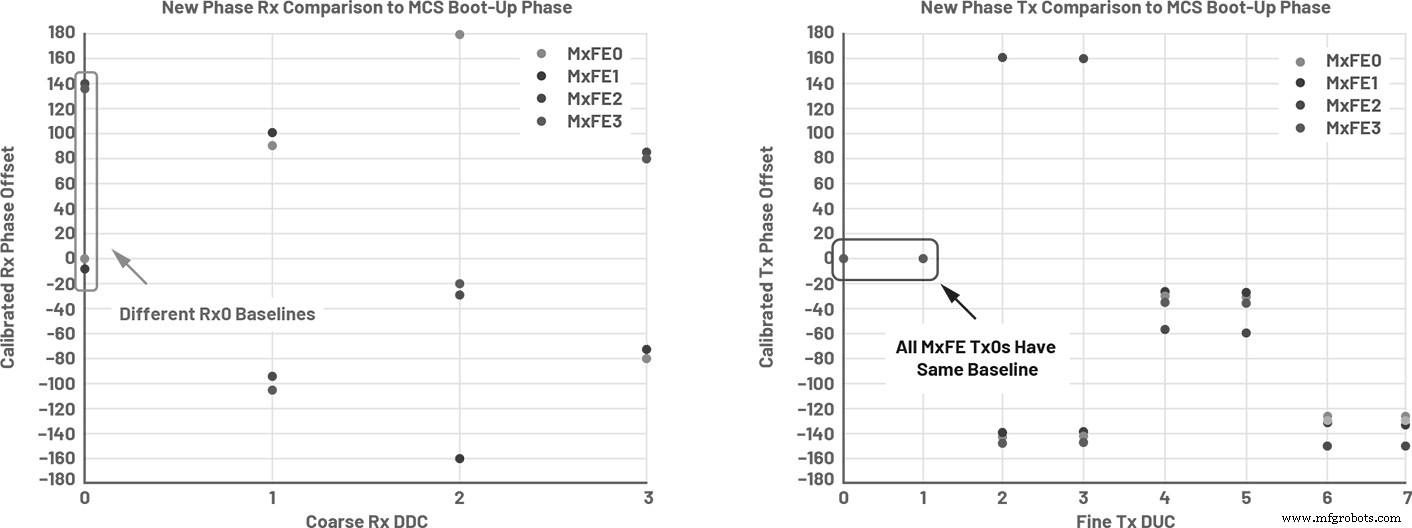

La figure 3 montre qu'un gradient thermique induit peut être détecté via l'unité de mesure de température (TMU) sur chaque puce de synthétiseur PLL. Comme on peut le voir sur la trace bleue en bas à gauche de la figure 3, des températures très variables à travers la plate-forme ont été intentionnellement induites en appliquant différents flux d'air de ventilateur au système. Cependant, l'utilisation de l'ajustement de phase PLL pour chaque circuit intégré démontre que quel que soit le flux d'air appliqué à la carte, les décalages de phase NCO étalonnés pour chaque canal de réception et de transmission sont déterministes lorsque l'on force le premier canaliseur de transmission de chaque circuit intégré de numériseur à être aligné sur chacun. autre. Ceci est révélé en observant le groupe serré de la même couleur de points sur les deux premiers tracés de la figure 3 malgré les différents gradients thermiques appliqués à la carte au cours de différents cycles d'alimentation.

cliquez pour l'image en taille réelle

Figure 3. La fonction MCS utilisée conjointement avec la fonction d'ajustement de phase PLL démontre le déterminisme de phase de mise sous tension pour tous les canaux de réception et de transmission, quel que soit le gradient thermique induit sur la plate-forme. (Source :Appareils analogiques)

Les registres IC du numériseur interrogés sont représentés en bas à droite de la figure 3, qui montrent la relation de phase SYSREF-LEMC mesurée après application du décalage de phase du synthétiseur PLL. Notez à partir des traces orange sur le graphique en bas à gauche que les ajustements de phase du synthétiseur PLL compensent entièrement toutes les phases SYSREF non nulles mesurées résultant d'un gradient thermique induit différent.

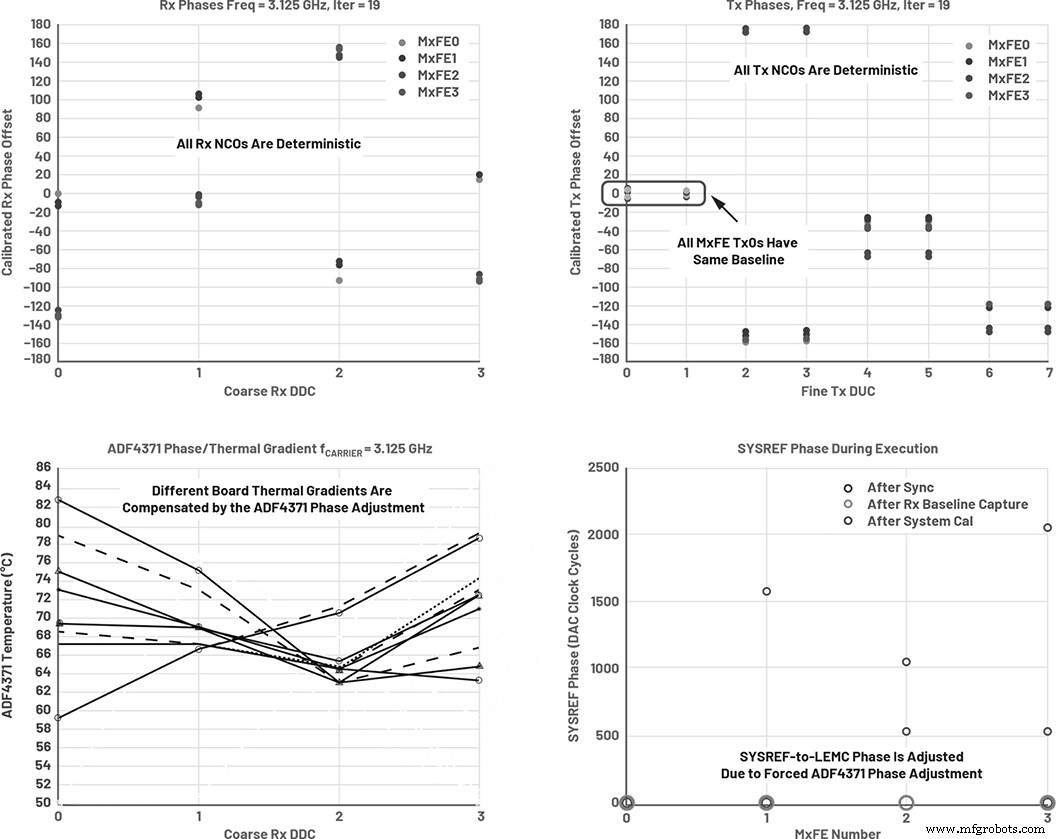

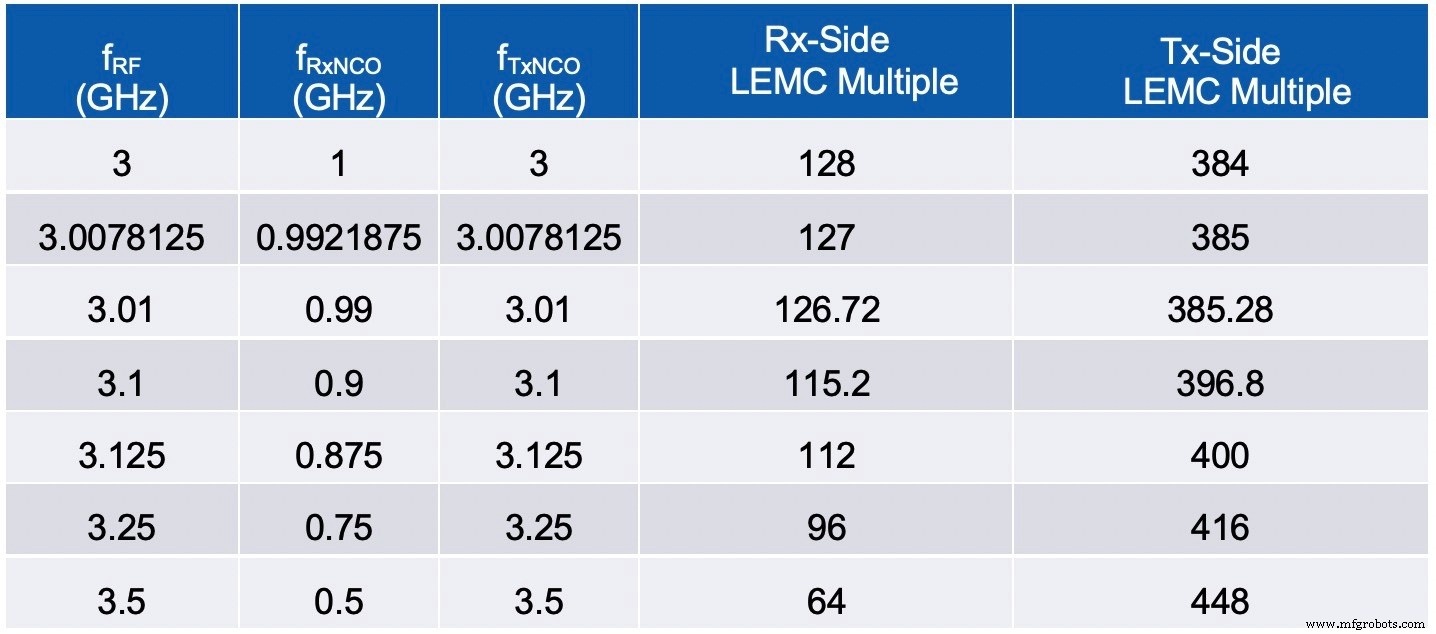

De nombreuses fréquences ont été mesurées, qui démontrent toutes une phase de réception et d'émission déterministe. Les fréquences spécifiques choisies pour cet article sont illustrées à la figure 4 et ont été choisies de telle sorte que le MCS soit démontré sur de nombreux gradients thermiques induits lors de l'utilisation de multiples non entiers de l'horloge de référence ou du LEMC.

Figure 4. Les fréquences RF utilisées dans cet article sont choisies pour démontrer les fonctions MCS sur une large gamme de sources d'horloge, y compris des multiples non entiers de l'horloge de référence et LEMC. (Source :Appareils analogiques)

Évolutivité vers plusieurs sous-matrices

Les données présentées dans cet article sont principalement axées sur les performances du MCS au niveau du sous-tableau, mais il est également nécessaire de s'assurer que ces fonctionnalités de synchronisation sont réalisables au niveau du tableau plus large et sur plusieurs sous-tableaux. Pour atteindre ce niveau de synchronisation plus élevé, un arbre d'horloge au niveau du tableau est nécessaire pour garantir que les demandes SYSREF adressées à chaque sous-tableau illustré à la figure 1 de la partie 1 arrivent de manière synchrone au circuit intégré de tampon d'horloge de chaque sous-tableau. Ensuite, étant donné ce critère, chaque sous-matrice peut émettre les SYSREF et les horloges BBP requises comme décrit précédemment de telle sorte que ces signaux arrivent aux circuits intégrés de numériseur de sous-matrice et au BBP dans le même cycle d'horloge d'échantillonnage à travers la plus grande matrice. Cet arbre d'horloge au niveau du réseau requiert que la distribution d'horloge à chaque sous-réseau possède les blocs d'ajustement de retard nécessaires pour réaliser une distribution de demande SYSREF synchrone à chacun des circuits intégrés de puce d'horloge de sous-réseau en aval. De cette manière, plusieurs BBP connectés à plusieurs sous-réseaux sont finalement synchronisés.

Algorithme d'étalonnage au niveau du système

Bien que les algorithmes MCS présentés dans les sections précédentes fournissent une phase déterministe de mise sous tension pour chaque canal de réception et de transmission, ces phases ne sont pas nécessairement alignées sur tous les canaux du domaine RF en raison de différences dans les longueurs de trace frontales RF entre les canaux. . Par conséquent, bien que les algorithmes MCS simplifient effectivement le processus d'étalonnage du réseau, il est toujours nécessaire de subir une routine d'étalonnage au niveau du système pour aligner les phases de chaque canal RF au sein du système.

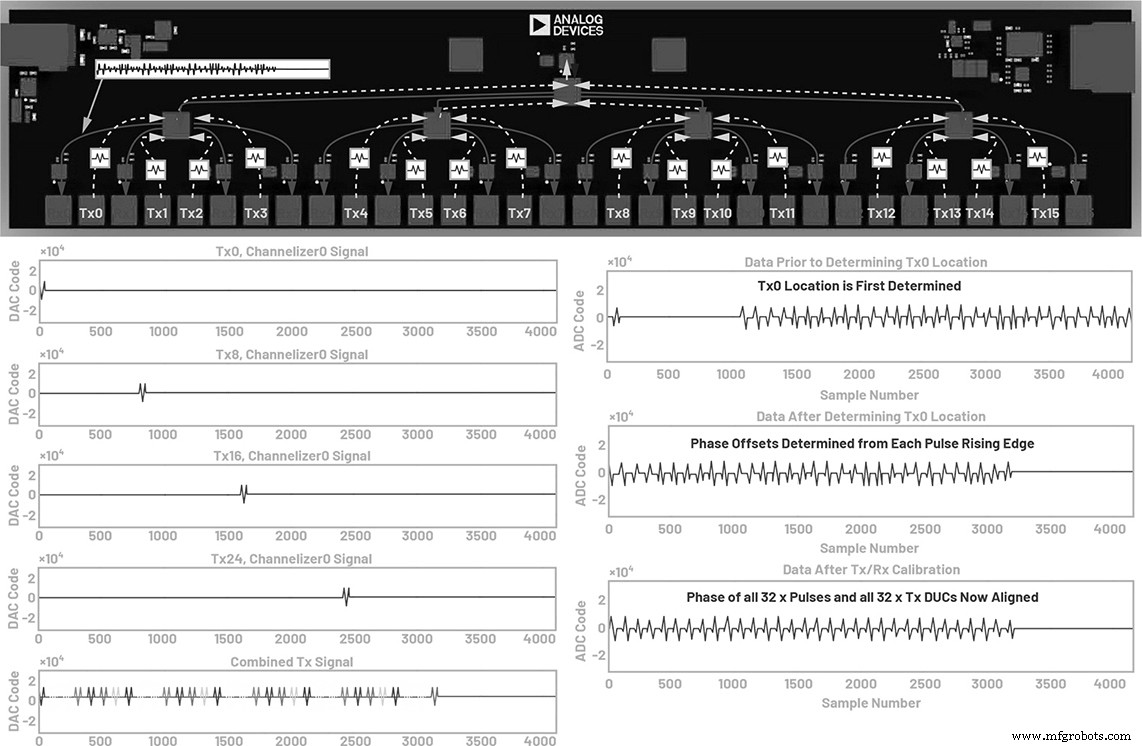

Il est donc nécessaire de développer un algorithme d'étalonnage efficace au niveau du système en plus d'effectuer les algorithmes MCS. La méthode d'étalonnage au niveau du système pour cet article utilise une forme d'onde de bande de base spécifique et est complètement autonome sans avoir besoin d'aucun équipement externe. Le système décrit dans cet article est capable d'injecter des formes d'onde de bande de base distinctes dans chaque canaliseur de la plate-forme. En utilisant cette capacité, une forme d'onde en bande de base constituée d'une impulsion d'une période pour chaque canaliseur de transmission est injectée dans le sous-réseau, comme illustré dans le coin inférieur gauche de la figure 5. Chaque canaliseur de transmission ne produit donc qu'une seule impulsion. Cependant, les formes d'onde sont décalées sur tous les canaux de transmission de sorte qu'une seule impulsion d'une période est émise à la fois dans tout le système. La sortie de tous les canaux de transmission est combinée dans le domaine RF, puis divisée et renvoyée dans tous les canaux de réception, comme indiqué dans le haut de la figure 5. Enfin, une capture de données de réception simultanée est effectuée pour tous les canaux de réception et les données sont enregistrées à une matrice de 4096 × 16, où 4096 est la taille de l'échantillon collecté pour les 16 canaux de réception.

cliquez pour l'image en taille réelle

Figure 5. Un algorithme d'étalonnage au niveau du système est utilisé en conjonction avec le MCS pour réaliser rapidement l'alignement de tous les canaux de réception et de transmission du système. (Source :Appareils analogiques)

Ces données sont ensuite analysées verticalement le long de la première colonne (correspondant à Rx0) pour localiser l'impulsion de canalisateur Tx0, comme indiqué dans le sous-parcelle en haut en bas à droite de la figure 5. Une fois l'impulsion Tx0 identifiée, tous les autres emplacements d'impulsion sont connus et la phase complexe du front montant de chaque impulsion est calculée et enregistrée dans un vecteur 1 × 16 qui correspond aux décalages de phase mesurés présents sur tous les canaux de transmission du système. Avec cette connaissance et en utilisant Tx0 comme référence de base, les phases complexes de tous les canaux de transmission sont ensuite modifiées en fonction des décalages mesurés.

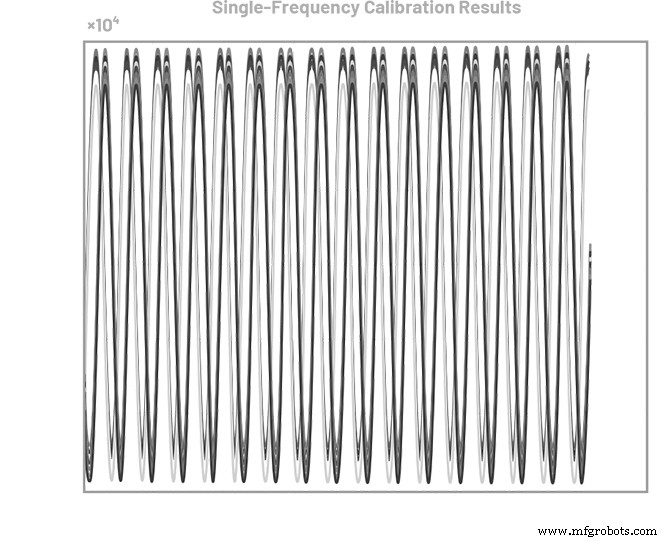

De même, étant donné que le même signal combiné est envoyé dans tous les canaux de réception, les données sont ensuite analysées horizontalement le long de la matrice (en regardant à travers tous les canaux de réception). Les phases complexes de tous les canaux de réception sont ensuite mesurées par rapport à Rx0 et enregistrées dans un vecteur 1x16 correspondant aux décalages de phase de réception mesurés présents dans le système. Les phases complexes NCO de réception sont ensuite ajustées dans tout le sous-réseau pour aligner en phase tous les canaux par rapport à Rx0, comme le montrent les codes ADC en phase (I) et en quadrature (Q) pour les 16 canaux de réception de la figure 6. On peut remarquer que, bien que le tracé de la figure 6 aligne la phase de tous les canaux, il n'aligne pas nécessairement tous les canaux en amplitude. Cependant, en utilisant les filtres à réponse impulsionnelle finie (FIR) sur puce maintenant présents sur ces circuits intégrés de numériseur, on pourrait également obtenir un alignement d'amplitude et de phase sur les canaux sans avoir besoin d'allouer des ressources FPGA gourmandes en énergie pour obtenir le même résultat.

cliquez pour l'image en taille réelle

Figure 6. L'alignement de phase I&Q de réception à 16 canaux est obtenu à l'aide du MCS et d'un algorithme d'étalonnage autonome au niveau du système. (Source :Appareils analogiques)

Cet algorithme d'étalonnage au niveau du système est actuellement réalisé dans MATLAB ® et prend environ trois secondes pour terminer. Cependant, s'il est implémenté en langage de description matérielle (HDL), ce temps d'étalonnage peut être encore réduit tout en conservant un algorithme complètement autonome. De plus, en s'appuyant sur les algorithmes MCS, si la fréquence et l'amplitude du système sont connues au démarrage, les utilisateurs peuvent charger les valeurs de décalage de phase à partir d'une table de recherche au lieu d'avoir à subir les mesures décrites dans cette méthode d'étalonnage au niveau du système. Dans ce cas, la méthode d'étalonnage au niveau du système peut être utilisée pour remplir les déphasages enregistrés dans une table de recherche lors d'un étalonnage en usine.

Conclusion

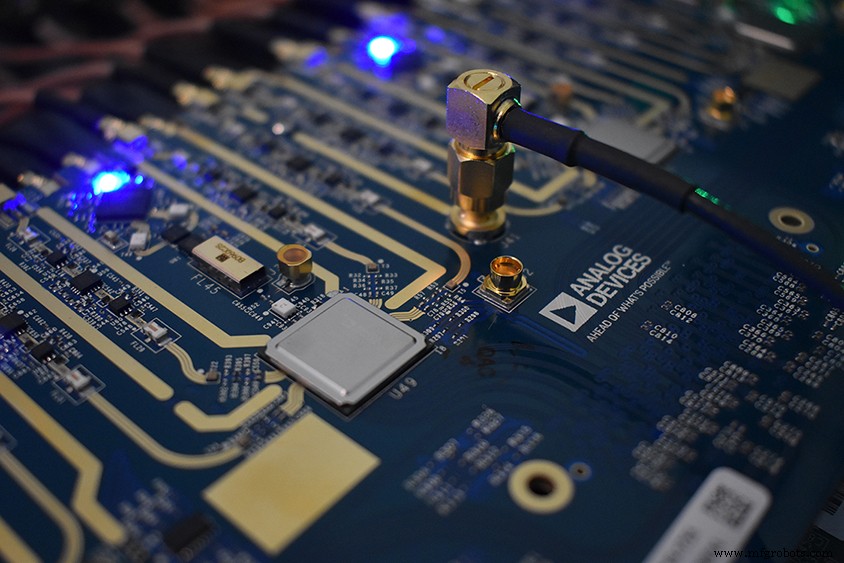

Un processus MCS réussi a été démontré en utilisant quatre circuits intégrés AD9081 MxFETM d'Analog Devices comme épine dorsale du sous-réseau. Les gradients thermiques à travers la plate-forme sont compensés à l'aide de blocs d'ajustement de phase dans quatre synthétiseurs PLL ADF4371. Un IC d'horloge HMC7043 est utilisé pour distribuer les SYSREF et les horloges BBP nécessaires à l'interface JESD204C. Les algorithmes MCS de l'AD9081 permettent des étalonnages simplifiés au niveau du système et fournissent une phase déterministe de mise sous tension pour les multiples fréquences et gradients thermiques présents dans le système. Un algorithme d'étalonnage efficace au niveau du système est également présenté qui est utilisé pour remplir les LUT pendant l'étalonnage en usine, et réduit donc considérablement le temps de démarrage du système. Cette plate-forme est illustrée à la figure 7 et est appelée Quad-MxFE. Le système est disponible à l'achat auprès d'Analog Devices. Ce travail est pertinent pour tout système multicanal présent dans tout radar à commande de phase, guerre électronique, instrumentation ou plate-forme 5G.

Figure 7. La plate-forme Quad-MxFE est disponible à l'achat auprès d'Analog Devices. (Source :Appareils analogiques)

Références

1 Del Jones. « Amorce JESD204C :Quoi de neuf et dedans pour vous - Partie 1 ». Dialogue analogique , Vol. 53, n° 2, juin 2019.

2 Del Jones. « Amorce JESD204C :Quoi de neuf et dedans pour vous - Partie 2. » Dialogue analogique , Vol. 53, n° 3, juillet 2019.

Embarqué

- 3 raisons pour lesquelles DevOps et Cloud ont besoin l'un de l'autre ; DevCloudOps

- Vecteurs et formes d'onde CA

- Structures et classes en C++

- Boîtes aux lettres :présentation et services de base

- Sémaphores :introduction et services de base

- Files d'attente :introduction et services de base

- Vidéo immersive, IA et phase suivante de la mise en forme technologique des ventes au détail

- Le tournage dur et la rectification cylindrique étaient faits l'un pour l'autre

- Types courants de fraiseuses et quand les utiliser