Déterminisme de la phase de mise sous tension :Utilisation de la synchronisation multipuce

L'intégration de plusieurs blocs de traitement du signal numérique (DSP), de convertisseurs numérique-analogique (DAC) à large bande et de convertisseurs analogique-numérique (ADC) à large bande au sein d'une seule puce monolithique permet désormais de décharger les ressources FPGA gourmandes en énergie pour permettent une empreinte plus petite, une puissance inférieure, des plates-formes de nombre de canaux accrus qui peuvent échantillonner à des taux plus élevés que ceux qui étaient auparavant réalisables. Parallèlement à cette nouvelle capacité, de nouveaux algorithmes de synchronisation multipuce (MCS) sont intégrés à ces circuits intégrés (CI), qui permettent aux utilisateurs d'obtenir une phase (déterministe) connue pour tous les canaux lors de l'alimentation du système ou de toute autre modification logicielle du système. Cette phase déterministe simplifie donc les algorithmes d'étalonnage au niveau du système plus larges nécessaires pour réaliser la synchronisation de tous les canaux à la sortie ou à l'entrée des réseaux frontaux attachés à ces circuits intégrés. Cet article présente des résultats expérimentaux qui démontrent cette capacité MCS tout en utilisant une plate-forme de récepteur/émetteur à 16 canaux composée de plusieurs circuits intégrés de numériseur, de sources d'horloge et d'interfaces numériques.

Schéma fonctionnel du système de haut niveau

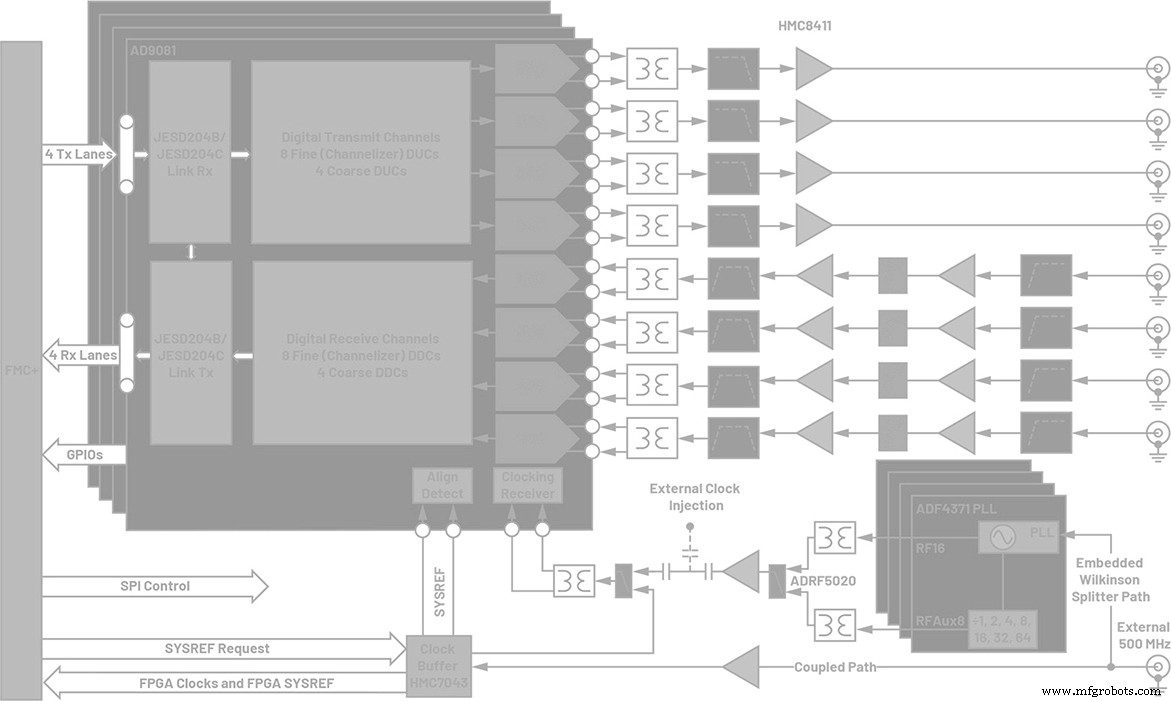

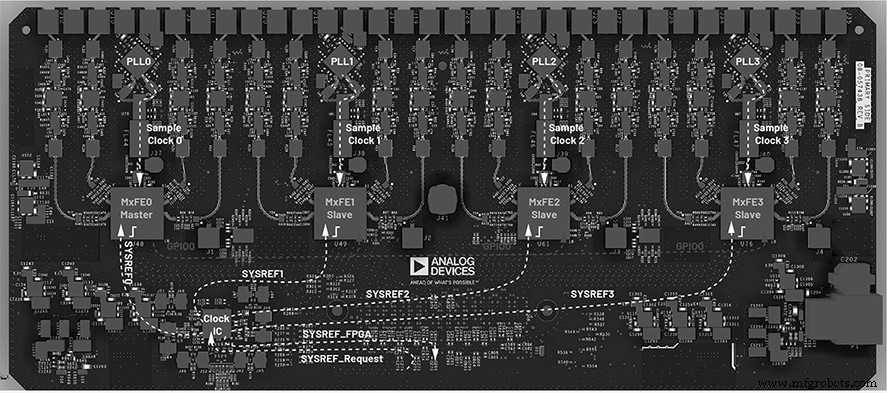

Un schéma fonctionnel du système utilisé pour ce test est illustré à la Figure 1 et se compose de quatre circuits intégrés DAC/ADC/DSP intégrés qui se composent chacun de quatre 12 DAC GSPS, quatre 4 GSPS ADC, et 12 convertisseurs élévateurs numériques (DUC) et 12 numériques blocs downconverter (DDC).

cliquez pour l'image en taille réelle

Figure 1. Un schéma fonctionnel de haut niveau du système utilisé pour démontrer le MCS et les algorithmes d'étalonnage multicanaux. (Source :Appareils analogiques)

Les DUC/DDC permettent une translation de fréquence et/ou une interpolation/décimation dans le domaine numérique. À l'aide d'une seule horloge de référence de 500 MHz injectée sur la carte, une mémoire tampon d'horloge verrouillée par référence est ensuite utilisée pour générer les signaux de référence du système nécessaires au MCS ainsi que les horloges requises pour l'interface numérique avec le processeur de bande de base (BBP). Le système contient également quatre synthétiseurs à boucle à verrouillage de phase (PLL) séparés qui génèrent les sources 12 GHz nécessaires pour cadencer chaque circuit intégré de numérisation à partir de la référence commune. Un frontal RF est connecté à chaque sortie/entrée du numériseur, ce qui crée un signal filtré et amplifié vers/depuis les connecteurs RF lancés par le bord. Une solution complète de distribution d'énergie est mise en œuvre. Toutes les tensions requises pour le système sont générées à partir d'une seule source de 12 V. Tous les signaux de transmission se propagent au bas de la carte, tandis que tous les signaux de réception se propagent sur le dessus de la carte pour obtenir l'isolation canal à canal la plus optimale.

Structure arborescente de l'horloge de sous-tableau

Comme mentionné précédemment, l'arbre d'horloge du sous-réseau se compose d'une seule source de référence de 500 MHz qui est divisée et envoyée aux entrées de référence de quatre circuits intégrés de synthétiseur PLL distincts, comme illustré ci-dessus à la figure 1. Ce signal de 500 MHz est également couplé à 10 dB, amplifié , et envoyé dans un autre CI tampon d'horloge qui est responsable de la génération des références système (SYSREF) et des horloges BBP requises pour l'interface numérique. L'objectif de cet arbre d'horloge est triple, car il :

- Permet aux retards SYSREF de chaque canal de corriger toute incompatibilité de longueur de trace entre les circuits intégrés.

- Permet l'ajustement individuel de la phase PLL/synthétiseur, et assure donc la synchronisation entre les sources d'horloge IC du numériseur respectives, pour compenser les gradients thermiques induits au sein du système.

- Permet à l'utilisateur de répondre aux exigences de configuration et de maintien nécessaires pour les circuits intégrés de numérisation.

Les circuits intégrés d'arbre d'horloge sont choisis pour démontrer que diverses anomalies de configuration de carte peuvent être corrigées dans le logiciel et/ou le matériel à l'aide de blocs de retard numériques et analogiques présents dans ces puces. En fin de compte, le résultat est un arbre d'horloge qui peut fournir une impulsion SYSREF à tous les circuits intégrés requis dans le même cycle d'horloge d'échantillonnage de chacun de ces circuits intégrés.

Interface numérique avec processeur de bande de base

Les quatre circuits intégrés de numérisation établissent chacun une interface de liaison numérique JESD204B ou JESD204C avec le BBP. 1,2 Cette interface est chargée de transmettre les codes ADC et DAC sur les traces physiques (SERDES) vers et depuis le BBP. Le nombre de traces SERDES différentielles utilisées dans cette interface est appelé nombre de voies (L) pour ce lien. La résolution binaire du convertisseur envoyée sur le lien est considérée comme N'. Le nombre de chemins de données canalisés, également appelés convertisseurs virtuels, est étiqueté M. Les résultats présentés dans cet article utilisent un lien JESD204C avec M =16, N' =16, L =4 pour les liens côté DAC et M =8 , N' =16, L =2 pour les liaisons côté ADC.

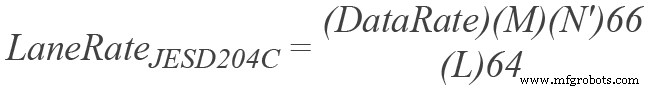

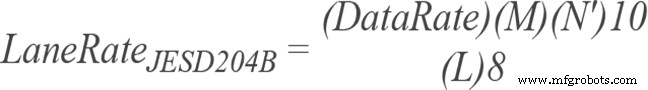

Le débit auquel les données sont transmises et reçues entre le numériseur IC et le BBP est appelé débit de voie. Les blocs DSP sur silicium (c'est-à-dire les DDC/DUC) permettent à l'utilisateur d'échantillonner les numériseurs à un débit différent du débit de données envoyé sur les voies physiques. En tant que tel, le débit de voie dépend du débit de données décimé/interpolé numériquement pour chaque chemin de données. Pour ce travail, un débit de données I/Q de 250 MSPS a été utilisé. Pour une interface JESD204C, le débit de voie est défini comme :

alors que pour une interface JESD204B, le débit de voie est défini comme :

Les résultats présentés dans cet article utilisent un débit de voie de 16,5 Gbit/s pour les liaisons JESD204C côté ADC et côté DAC.

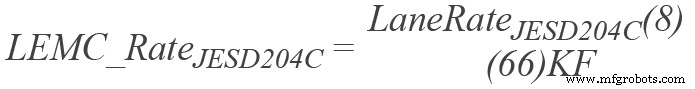

Chaque lien JESD204B/JESD204C peut être établi au sein de différentes sous-classes. Ces sous-classes sont séparées selon que la synchronisation multipuce ou la latence déterministe est requise. Pour ce travail, les données présentées utilisent un mode JESD204C de sous-classe 1, et utilisent donc des signaux SYSREF pour aligner des parties des données numériques transmises sur les multiples liaisons présentes dans le système. Plus précisément, dans ce mode de sous-classe 1 JESD204C, les signaux SYSREF sont utilisés pour aligner le compteur multibloc étendu local (LEMC), qui transmet à un débit :

où F est le nombre d'octets par trame JESD par voie et K est le nombre de trames par multitrame unique. Pour ce travail, F =8 et K =32, et donc un taux LEMC de 7.8125 MSPS est utilisé. La connaissance de ce taux LEMC est importante, car toute routine MCS réussie devra démontrer que les fréquences RF qui ne sont pas un multiple entier du taux LEMC sont capables d'atteindre une phase de mise sous tension déterministe.

Méthode de synchronisation multipuce

Dans ce système, les circuits intégrés ADC/DAC à large bande fournissent des circuits MCS pour permettre la mise sous tension déterministe de la phase sur tous les canaux RF d'émission et de réception, même en utilisant les blocs DUC/DDC DSP dans le circuit intégré. Cette fonction MCS permet aux utilisateurs de remplir une table de consultation (LUT) lors d'un étalonnage en usine afin de minimiser les temps d'arrêt opérationnels. Toute démonstration MCS réussie doit être capable de fournir une phase déterministe sur tous les canaux du système pour chaque tentative de fréquence RF, de gradient thermique et de cycle d'alimentation du système.

Les circuits intégrés ADC/DAC intégrés contiennent 12 blocs DUC et 12 blocs DDC, comme illustré ci-dessus dans la Figure 1. Chacun de ces blocs contient un sous-bloc d'interpolation (DUC) ou de décimation (DDC) pour modifier le débit de données du signal d'entrée numérique DAC ou Signal de sortie numérisé ADC, respectivement. Chaque DUC/DDC contient également un oscillateur à commande numérique (NCO) complexe qui permet une translation de fréquence dans le domaine numérique. Chacun de ces NCO est capable d'ajuster la phase complexe en temps réel de sorte que le signal numérique entre le DAC/ADC et le BBP puisse être modifié pour compenser diverses discordances de longueur de trace SERDES.

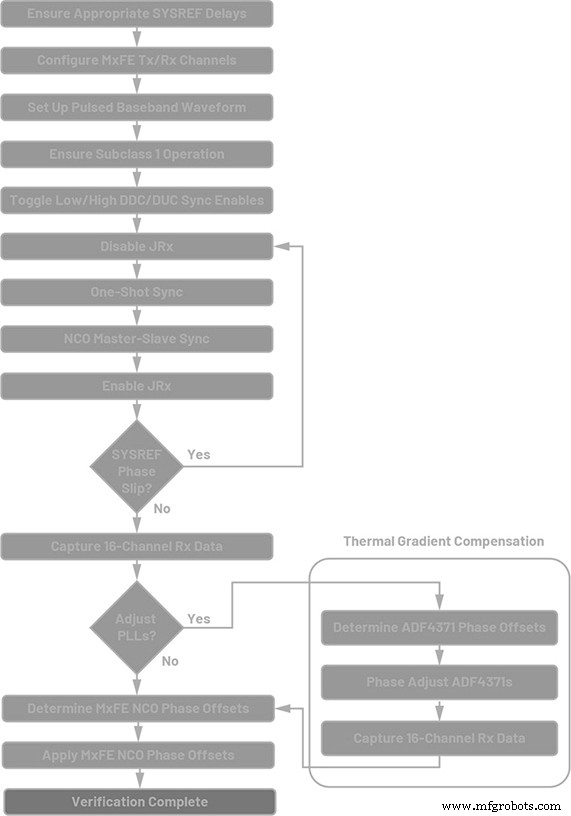

La fonction MCS de ces circuits intégrés ADC/DAC est responsable de la réalisation du déterminisme de phase dans tous les aspects du chemin de données du circuit intégré du numériseur. Le flux de travail pour atteindre le MCS est illustré à la figure 2.

cliquez pour l'image en taille réelle

Figure 2. Le workflow MCS implique des fonctionnalités distinctes qui alignent différentes parties du chemin de données. (Source :Appareils analogiques)

L'algorithme MCS peut être divisé en deux fonctions distinctes :

- Synchronisation unique :cette fonctionnalité est chargée d'aligner les données de bande de base envoyées sur les voies physiques de tous les circuits intégrés de numériseur au sein du système de sous-matrice.

- Synchronisation maître-esclave NCO :cette fonctionnalité est responsable de l'alignement de tous les NCO dans tous les différents circuits intégrés de numériseur au sein du système de sous-matrice.

La fonction de synchronisation unique nécessite d'abord que l'utilisateur définisse les paramètres de liaison JESD (tels que M, N', L, etc.), puis configure la logique de synchronisation pour toute moyenne SYSREF souhaitée (si vous utilisez des impulsions SYSREF continues). De plus, les délais LEMC souhaités peuvent être utilisés pour forcer la génération du LEMC à un certain délai après le front SYSREF. Une fois cette opération terminée, l'utilisateur active ensuite le bit de synchronisation unique dans chaque circuit intégré de numériseur, puis demande que les impulsions SYSREF soient envoyées à chaque circuit intégré au cours du même cycle d'horloge, comme illustré à la figure 3.

cliquez pour l'image en taille réelle

Figure 3. L'algorithme MCS utilise des signaux SYSREF pour implémenter une synchronisation unique et des signaux GPIO pour implémenter une synchronisation maître-esclave NCO afin d'obtenir une phase déterministe. (Source :Appareils analogiques)

Pour ce système, des retards analogiques fins ont été introduits dans le circuit intégré de tampon d'horloge pour permettre des SYSREF synchrones à tous les circuits intégrés de numériseur. Une vérification ultérieure peut être exécutée pour vérifier que le processus de synchronisation unique a été exécuté avec succès en interrogeant les registres au sein de chaque circuit intégré qui fournissent des informations sur la relation de phase entre le signal SYSREF et la limite LEMC de la liaison de chaque circuit intégré.

Une fois qu'une phase stable est mesurée (c'est-à-dire une fois que le registre de phase SYSREF-LEMC lit 0), l'utilisateur sait alors que les LEMC de tous les circuits intégrés de numériseur sont alignés et l'utilisateur peut alors procéder au processus de synchronisation maître-esclave NCO. Pour cette activité, les sous-tâches décrites pour la synchronisation unique sont contenues dans une interface de programmation d'application (API) fournie par le fabricant de la puce.

La fonction de synchronisation maître-esclave NCO affecte d'abord l'un des circuits intégrés de numériseur dans le sous-réseau pour agir en tant que puce maître, comme illustré ci-dessus à la figure 3. Tous les autres numériseurs sont alors considérés comme des circuits intégrés esclaves. Le circuit intégré maître est configuré de telle sorte que la broche GPIO0 de cet appareil soit configurée en tant que sortie et acheminée vers les réseaux GPIO0 des trois circuits intégrés de numériseur esclave. Les réseaux GPIO0 esclaves sont configurés comme entrées. L'utilisateur peut alors choisir de déclencher sur l'impulsion SYSREF, le front montant du LEMC ou le front descendant du LEMC. Pour les données présentées dans cet article, le front montant LEMC est utilisé comme source de déclenchement de synchronisation maître-esclave NCO et les réseaux GPIO sont acheminés via le BBP au lieu de localement sur le sous-réseau. Ensuite, les bits de synchronisation DDC sont basculés vers le bas puis vers le haut pour armer l'algorithme de synchronisation NCO côté ADC. De même, le bit d'alignement du microprocesseur est basculé vers le bas puis vers le haut pour armer l'algorithme de synchronisation NCO côté DAC.

Lorsque ce déclencheur est demandé, au prochain front montant du LEMC, le circuit intégré du numériseur maître émet un signal de sortie maître à l'état haut via son réseau GPIO0. Ce signal se propage aux entrées GPIO0 de chacun des appareils esclaves. Au prochain bord LEMC, tous les circuits intégrés de numériseur subissent un algorithme de réinitialisation NCO. Après cela, toutes les impulsions LEMC sont ignorées en ce qui concerne l'algorithme de synchronisation maître-esclave NCO. Comme pour la synchronisation unique, ces sous-tâches de synchronisation maître-esclave NCO sont contenues dans les fonctions de l'API pour la facilité d'utilisation de l'utilisateur.

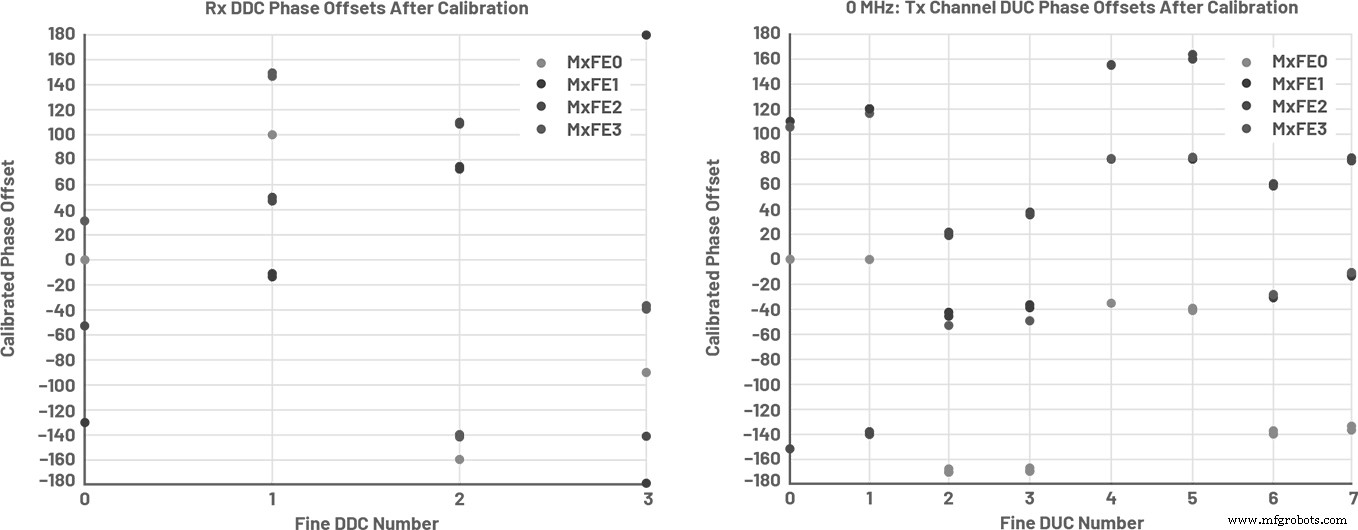

L'utilisation à la fois des fonctions de synchronisation unique et de synchronisation maître-esclave NCO aligne les deux entrées sur chaque DDC/DUC de telle sorte que le décalage de phase de sortie de chaque canal de réception et de transmission soit reproductible après plusieurs cycles d'alimentation, comme illustré à la Figure 4. Les données dans la figure 4 montre les décalages de phase calibrés sur 100 cycles d'alimentation (indiqués par plusieurs points pleins) pour chaque canaliseur de réception et de transmission pendant que le système fonctionne sous un gradient thermique statique lors de chaque redémarrage.

cliquez pour l'image en taille réelle

Figure 4. Les DDC fins de réception (à gauche) et les DUC fins de transmission (à droite) sont correctement alignés lors de l'exécution de l'algorithme MCS. (Source :Appareils analogiques)

Comme le montrent les multiples points présents sur cette figure, les points de chaque couleur pour un DDC/DUC donné sont tous étroitement regroupés à la même position après des cycles d'alimentation, décrivant ainsi une phase déterministe pour ce canal particulier. Pour les données de ce test, les huit DUC de canalisation ont été utilisés du côté émission, alors que seuls quatre des huit DDC de canalisation sont utilisés. Cependant, il a été confirmé qu'en effet, les huit DDC de canaliseur fournissent une phase déterministe tout en utilisant également l'algorithme MCS.

L'émission de cet algorithme au démarrage établit une phase déterministe pour chaque canal si les horloges d'échantillonnage du synthétiseur PLL et les IC SYSREF d'horloge maintiennent la même relation de phase au démarrage. Cependant, tout système subira des gradients thermiques, ce qui peut entraîner une dérive de l'horloge PLL et qui peut entraîner une phase de mise sous tension différente si elle n'est pas compensée. Pour compenser la dérive du gradient thermique au sein du système, cette plate-forme utilise des ajustements de phase du synthétiseur PLL.

Dans la prochaine partie de cette série d'articles, nous explorerons les ajustements de phase du synthétiseur PLL, l'évolutivité vers plusieurs sous-matrices et les algorithmes d'étalonnage au niveau du système.

Références

1 Del Jones. « Amorce JESD204C :Quoi de neuf et dedans pour vous - Partie 1 ». Dialogue analogique , Vol. 53, n° 2, juin 2019.

2 Del Jones. « Amorce JESD204C :Quoi de neuf et dedans pour vous - Partie 2. » Dialogue analogique , Vol. 53, n° 3, juillet 2019.

Embarqué

- Déphasage

- Phase AC

- C# en utilisant

- MACOM lance un nouvel amplificateur à bruit de phase ultra-faible

- Keysight lance un nouveau système de test de bruit de phase

- L'utilisation de plusieurs puces d'inférence nécessite une planification minutieuse

- Comment générer une forme d'onde de haute précision à l'aide d'un DAC et d'un PCB personnalisé

- Générateur d'horloge Verilog

- Utiliser une fraiseuse comme tour