Contrôle d'impédance dans la conception de circuits imprimés de circuits numériques à grande vitesse

Les technologies de contrôle d'impédance sont très importantes dans la conception de circuits numériques à grande vitesse dans laquelle des méthodes efficaces doivent être adoptées pour assurer l'excellente performance des PCB à grande vitesse.

Calcul d'impédance et contrôle d'impédance des lignes de transmission de circuit à grande vitesse sur PCB

• Modèle équivalent sur les lignes de transmission

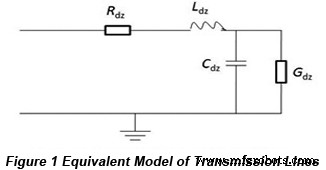

La figure 1 montre l'effet équivalent des lignes de transmission sur les PCB, qui est une structure comprenant un condensateur tandem et multiple, une résistance et une inductance (modèle RLGC).

La valeur typique de la résistance en tandem est comprise entre 0,25 et 0,55 ohms/pied et la valeur de résistance de plusieurs résistances reste généralement assez élevée. Avec la résistance parasite, la capacité et l'inductance ajoutées dans les lignes de transmission PCB, l'impédance globale sur les lignes de transmission est appelée impédance caractéristique (Z0 ). La valeur de l'impédance caractéristique est relativement faible à condition que le diamètre de la ligne soit grand, que la ligne soit proche de la puissance/terre ou que la constante diélectrique soit élevée. La figure 3 montre le modèle équivalent de la ligne de transmission avec une longueur de dz, sur la base duquel l'impédance caractéristique de la ligne de transmission peut être déduite comme formule : . Dans cette formule, L fait référence à l'inductance de chaque unité de longueur sur la ligne de transmission tandis que C fait référence à la capacité de chaque unité de longueur sur la ligne de transmission.

. Dans cette formule, L fait référence à l'inductance de chaque unité de longueur sur la ligne de transmission tandis que C fait référence à la capacité de chaque unité de longueur sur la ligne de transmission.

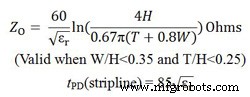

• Formule de calcul d'impédance et de retard des lignes de transmission sur PCB

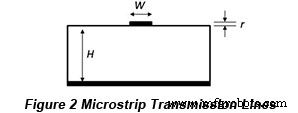

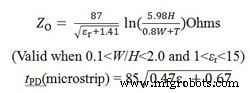

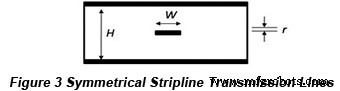

| Lignes de transmission sur PCB | Formule de calcul d'impédance et de retard |

|  |

|  |

Dans les formules ci-dessus, Z0 fait référence à l'impédance (Ohms), W fait référence à la largeur des lignes (pouces), T fait référence à l'épaisseur des lignes (pouces), H fait référence à la distance au sol (pouces), fait référence à la constante diélectrique relative du substrat, et tPD fait référence au temps de retard (ps/inch).

• Règles de disposition du contrôle d'impédance des lignes de transmission

Sur la base de l'analyse ci-dessus, le retard unitaire de l'impédance et du signal est indépendant de la fréquence des signaux mais lié à la structure de la carte, à la constante diélectrique relative du matériau de la carte et aux attributs physiques du routage. Cette conclusion est extrêmement importante pour comprendre les PCB à grande vitesse et pour la conception de PCB à grande vitesse. De plus, la vitesse de transmission de la ligne de transmission du signal dans la couche externe est beaucoup plus rapide que celle de la couche interne, de sorte que ces éléments doivent être pris en compte pour l'agencement de la disposition des lignes clés.

Le contrôle d'impédance est la prémisse importante pour la mise en œuvre de la transmission du signal. Cependant, selon la structure de la carte et la formule de calcul de l'impédance des lignes de transmission, l'impédance ne dépend que du matériau PCB et de la structure de la couche PCB, la largeur de ligne et les caractéristiques de routage étant inchangées pour la même ligne. Par conséquent, l'impédance d'une ligne ne changera pas sur différentes couches de PCB, ce qui n'est pas autorisé dans la conception de circuits à grande vitesse.

Un PCB haute vitesse à haute densité est conçu pour cet article et la plupart des signaux à bord ont des exigences d'impédance. Par exemple, la ligne de signal CPCI doit avoir une impédance de 65 ohms, un signal différentiel de 100 ohms et d'autres signaux tous de 50 ohms chacun. Selon l'espace de routage des PCB, un routage d'au moins dix couches doit être utilisé et un plan de conception de PCB à 16 couches est déterminé.

L'épaisseur globale de la planche ne pouvant excéder 2mm, il y a quelques difficultés au niveau de l'empilage avec quelques problèmes pris en compte :

1). Chaque couche de signal a des plans d'image adjacents pour protéger l'impédance et la qualité du signal.

2). Chaque plan d'alimentation a une couche de masse complète à côté d'eux afin que les performances de puissance puissent être bien assurées.

3). L'empilement des planches nécessite de l'équilibre, en évitant le gauchissement des planches.

La constante diélectrique du milieu est fixée à 4,3. Sur la base de la conception d'empilement ci-dessus, la largeur de ligne et la distance entre les lignes doivent être définies en fonction du résultat du calcul afin de garantir l'exigence d'impédance du signal. La largeur de ligne est obtenue comme le résultat suivant :

1). La largeur de la ligne de signal sur la couche de surface est de 5 mils avec une impédance de 58,7 Ohms.

2). La largeur de la ligne de signal CPCI sur la couche de surface est de 4,5 mils avec une impédance de 61,7 Ohms.

3). La largeur de la ligne de signal dans la couche interne est de 4,5 mils avec une impédance de 50,2 Ohms.

4). La largeur des lignes dans la zone BGA dans la couche interne et la couche de surface est de 4 mils avec une impédance de couche de surface de 64,6 Ohms et une impédance de couche interne de 52,7 Ohms.

5). La largeur de la ligne différentielle microruban dans la couche interne est de 5 mils avec une distance entre les lignes de 6 mils et une impédance de 100,54 Ohms.

6). La largeur de la ligne différentielle stripline dans la couche interne est de 4,5 mils avec une distance entre les lignes de 10 mils et une impédance de 96,6 Ohms.

La distance entre les lignes est définie comme suit :

1). La distance entre les lignes de signal (5 mils) sur la couche de surface est de 5,0 mils.

2). La distance entre les lignes de signal CPCI (4,5 mils) sur la couche de surface est de 9,0 mils.

3).. La distance entre les lignes de signal (4,5 mils) sur la couche intérieure est de 7,0 mils.

4). La distance entre les lignes sur la couche de surface et la couche intérieure est de 4,0 mils.

5). La distance entre les lignes de signal différentiel sur la couche interne et entre elles et les autres lignes de signal doit être maintenue à au moins 25 mils.

6). La distance entre les lignes de signal différentiel sur la couche de surface et entre elles et les autres lignes de signal doit être maintenue à au moins 20 mils.

Après l'impression du circuit imprimé, l'impédance de la carte de test est testée par le testeur d'impédance POLAR-Cits500 avec les résultats dans le tableau suivant. Les données indiquent que l'impédance doit être contrôlée dans la plage de 50Ohmۯ%, 60Ohmۯ% et 100Ohmۯ% dans le processus de conception et de fabrication de PCB à grande vitesse.

| Impédance préréglée (Ohm) | Impédance pratique (Ohm) |

| 50 | 47.52-52.33 |

| 60 | 57.65-61.35 |

| 100 | 93.65-106.35 |

LVDS et son contrôle d'impédance sur les PCB

• LVDS

LVDS est un type de niveau de transmission de signal série à grande vitesse avec les avantages d'une vitesse de transmission élevée, d'une faible consommation d'énergie, d'une forte capacité anti-interférence, d'une longue distance de transmission et d'une correspondance réalisable. Les domaines d'application de LVDS incluent l'informatique, la communication et la consommation.

• Conception d'impédance de LVDS

LVDS présente une variation de tension de seulement 350 MV avec la plus longue distance de transmission de plus de 10 mètres. Afin de garantir que les signaux ne seront pas influencés par le signal réfléchi lors du processus de transmission du signal dans les lignes de transmission, l'impédance des lignes de transmission doit être sous contrôle avec une impédance de ligne unique de 50 Ohms et une impédance différentielle de 100 Ohms. Dans l'application pratique, l'impédance peut être contrôlée en définissant une épaisseur d'empilement raisonnable et des paramètres moyens, en ajustant la largeur de ligne et la distance entre les lignes et en calculant l'impédance des lignes simples et des lignes différentielles à l'aide de certains outils d'analyse de simulation à grande vitesse.

Cependant, la plupart du temps, il est relativement difficile de répondre aux exigences d'impédance monoligne et d'impédance différentielle. D'une part, la plage de réglage de la largeur de ligne W et de la distance entre les lignes S est contrôlée par l'espace de conception physique. Par exemple, le routage et la largeur de ligne dans les connecteurs de marge avec BGA ou DIP sont influencés par la taille et la distance du pad. D'autre part, le changement de W et S influencera le résultat de l'impédance monoligne et différentielle. Jusqu'à présent, il est facile et pratique de déterminer la relation entre la largeur de ligne prédéfinie et la distance de ligne.

• Règles de routage LVDS

D'une manière générale, le routage différentiel des signaux est mis en œuvre selon des règles de conception d'impédance, ce qui est capable d'assurer la qualité LVDS. Dans le routage pratique, LVDS doit se conformer aux règles suivantes :

1). Les paires différentielles doivent être aussi courtes que possible, les lignes doivent être droites et le nombre de trous traversants doit être réduit. La distance entre les lignes de signal dans les paires différentielles doit être la même. Toutes ces règles contribuent à éviter les longs trajets et les nombreuses bifurcations. En ce qui concerne les virages, un virage à 45 degrés doit être utilisé au lieu de 90 degrés.

2). La distance entre les paires différentielles doit être maintenue plus de 10 fois afin de réduire la diaphonie entre les lignes. Si nécessaire, des trous de terre traversants peuvent être placés entre les paires différentielles pour l'isolation.

3). LVDS ne peut pas être divisé sur la surface. Bien que deux signaux différentiels soient des chemins de retour mutuels, le chemin de retour du signal ne peut pas être réduit en raison de la division à travers la surface. Néanmoins, les lignes de transmission entraîneront éventuellement une discontinuité d'impédance par manque de plans image.

4). Évitez les signaux différentiels entre les couches. Lors de la fabrication de PCB, la précision d'alignement d'empilement entre les couches est bien inférieure à la précision de gravure dans la même couche plus la perte moyenne lors de l'empilement, ce qui conduit à la modification de l'impédance différentielle entre les paires différentielles.

5). Dans la conception d'impédance, la méthode de couplage doit être utilisée.

6). Une structure d'empilement de PCB appropriée doit être définie pour assurer l'isolation entre les signaux de niveau de tension et le LVDS. Lorsque cela est possible, des signaux tels que TTL/CMOS haute vitesse peuvent être définis sur différentes couches, isolés du routage LVDS par des couches de masse et d'alimentation.

sept). Les paires de signaux différentiels doivent être compatibles avec la longueur du routage.

Ressources utiles

• Éléments affectant l'impédance caractéristique des PCB et des solutions

• Considérations de conception d'impédance pour les PCB Flex-Rigid

• Comment analyser et interdire l'impédance de l'alimentation PCB à grande vitesse

• Contrôle d'impédance des vias et son influence sur l'intégrité du signal dans la conception de circuits imprimés

• Service de fabrication de circuits imprimés complet de PCBCart - Plusieurs options à valeur ajoutée

• Service d'assemblage de circuits imprimés avancé de PCBCart - Commencez à partir de 1 pièce

Technologie industrielle

- Logiciel de mise en page de circuits imprimés

- Causes de la corrosion des PCB

- Considérations sur la disposition des circuits imprimés

- Considérations relatives à la conception de l'impédance pour les PCB flex-rigides

- Reculs et solutions dans la conception de circuits imprimés RF

- 3 techniques de routage sur la conception de circuits de signaux à grande vitesse sur PCB

- Conseils de mise en page à grande vitesse

- Analyse de l'intégrité du signal et conception de circuits imprimés sur un circuit mixte numérique-analogique à grande vitesse

- Défis de conception de circuits imprimés à grande vitesse sur l'intégrité du signal et leurs solutions