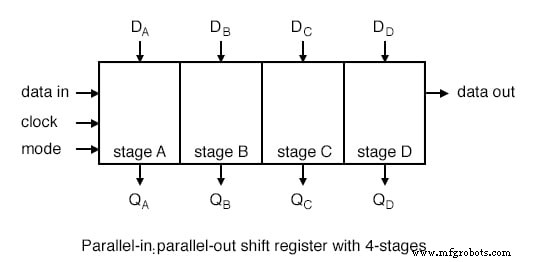

Registres à décalage universels :entrée parallèle, sortie parallèle

Le but du registre à décalage entrée/sortie parallèle est de prendre des données parallèles, de les décaler, puis de les sortir comme indiqué ci-dessous.

Un registre à décalage universel est un appareil à tout faire en plus de la fonction d'entrée/sortie parallèle.

Ci-dessus, nous appliquons quatre bits de données à un registre à décalage entrée/sortie parallèle à DA DB DC DD . Le contrôle de mode, qui peut être plusieurs entrées, contrôle le chargement parallèle par rapport au décalage.

Le contrôle de mode peut également contrôler la direction de décalage dans certains appareils réels. Les données seront décalées d'une position de bit pour chaque impulsion d'horloge.

Les données décalées sont disponibles aux sorties QA QB QC QD . Les « entrées de données » et « sorties de données » sont fournies pour la mise en cascade de plusieurs étapes.

Cependant, ci-dessus, nous ne pouvons que cascader les données pour le décalage vers la droite. Nous pourrions adapter la cascade de données de décalage à gauche en ajoutant une paire de signaux de pointage vers la gauche, « entrée de données » et « sortie de données », ci-dessus.

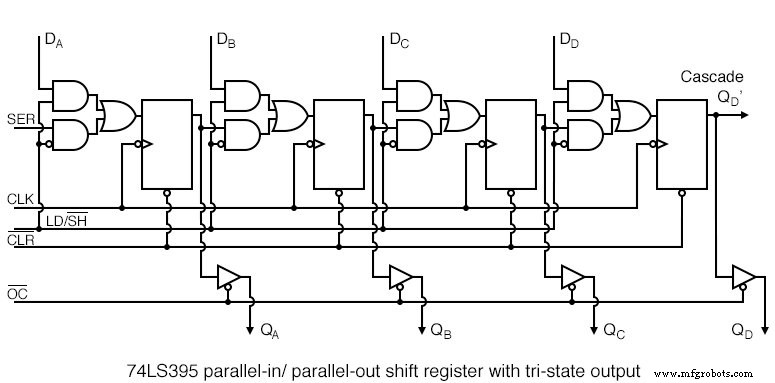

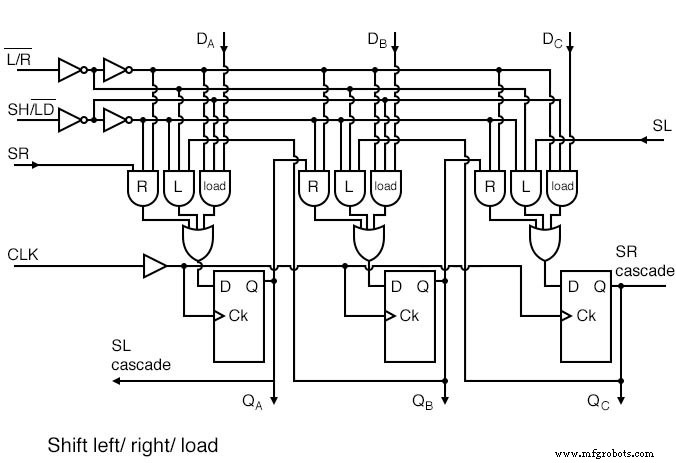

Les détails internes d'un registre à décalage parallèle entrée/sortie parallèle à décalage vers la droite sont indiqués ci-dessous.

Les tampons à trois états ne sont pas strictement nécessaires au registre à décalage entrée/sortie parallèle, mais font partie du dispositif du monde réel illustré ci-dessous.

Le 74LS395 correspond si étroitement à notre concept d'un hypothétique registre à décalage entrée/sortie parallèle à décalage vers la droite que nous utilisons une version trop simplifiée des détails de la fiche technique ci-dessus.

Voir le lien vers la fiche technique complète pour plus de détails, plus loin dans ce chapitre.

LD/SH' contrôle le multiplexeur ET-OU à l'entrée des données vers les FF. Si LD/SH’=1 , les quatre portes ET supérieures sont activées permettant l'application d'entrées parallèles DA DB DC DD aux quatre entrées de données FF.

Notez la bulle de l'onduleur à l'entrée d'horloge des quatre FF. Cela indique que le 74LS395 synchronise les données sur l'horloge négative, qui correspond à la transition de haut en bas.

Les quatre bits de données seront cadencés en parallèle à partir de DA DB DC DD à QA QB QC QD à la prochaine horloge négative. Dans cette « vraie partie », OC’ doit être faible si les données doivent être disponibles sur les broches de sortie réelles et non uniquement sur les FF internes.

Les données précédemment chargées peuvent être décalées vers la droite d'une position de bit si LD/SH'=0 pour les fronts d'horloge négatifs suivants.

Quatre horloges déplaceraient entièrement les données hors de notre registre à décalage à 4 bits. Les données seraient perdues à moins que notre appareil ne soit mis en cascade à partir de QD ' à SER d'un autre appareil.

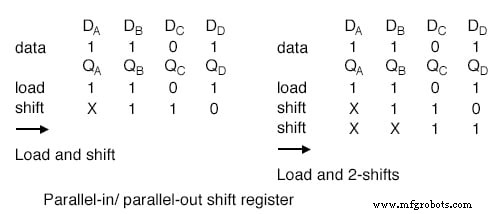

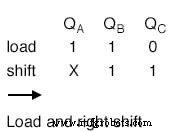

Ci-dessus, un modèle de données est présenté aux entrées DA DB DC DD . Le motif est chargé dans QA QB QC QD . Ensuite, il est décalé d'un bit vers la droite.

Les données entrantes sont indiquées par X , ce qui signifie que nous ne savons pas ce que c'est. Si la saisie (SER ) étaient fondés, par exemple, nous saurions quelles données (0 ) a été déplacé.

Également illustré, le décalage vers la droite de deux positions, nécessitant deux horloges.

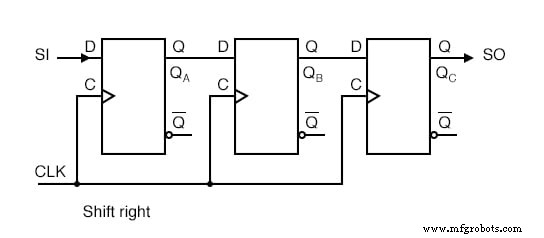

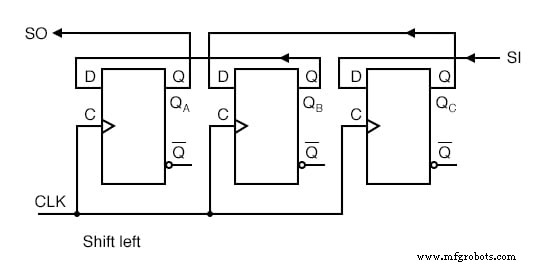

La figure ci-dessus sert de référence pour le matériel impliqué dans le déplacement à droite des données.

Il est même trop simple de s'embêter avec cette figure, sauf pour la comparaison avec des figures plus complexes à suivre.

Le décalage vers la droite des données est fourni ci-dessus pour référence au précédent levier vers la droite.

Si nous devons nous déplacer vers la gauche, les FF doivent être recâblés. Comparez avec le levier de vitesses droit précédent. Aussi, SI et SO ont été inversés. SI passe à QC . QC passe à QB . QB passe à QA . QR part sur le SO connexion, où il pourrait se transmettre en cascade à un autre levier de vitesses SI . Cette séquence de décalage de gauche est en arrière de la séquence de décalage de droite.

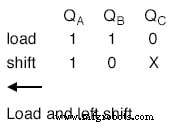

Ci-dessus, nous décalons le même modèle de données vers la gauche d'un bit.

Il y a un problème avec la figure "décaler à gauche" ci-dessus. Il n'y a pas de marché pour cela. Personne ne fabrique une pièce décalée vers la gauche.

Un « vrai appareil » qui déplace une direction peut être câblé à l'extérieur pour déplacer l'autre direction. Ou, devrions-nous dire qu'il n'y a ni gauche ni droite dans le contexte d'un appareil qui se déplace dans un seul sens.

Cependant, il existe un marché pour un appareil qui se déplacera à gauche ou à droite sur commande d'une ligne de commande. Bien sûr, gauche et droite sont valables dans ce contexte.

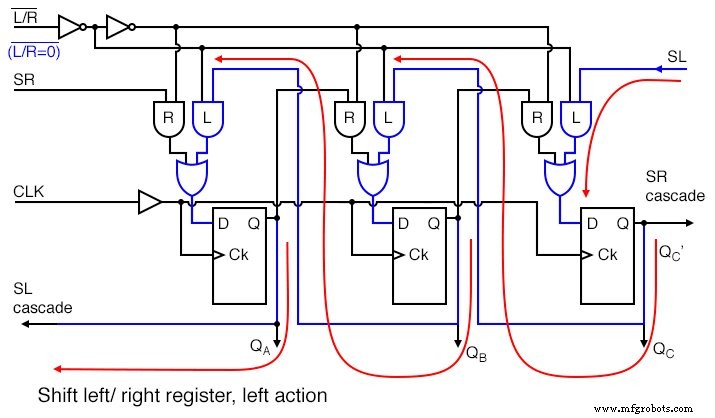

Ce que nous avons ci-dessus est un hypothétique registre à décalage capable de se déplacer dans les deux sens sous le contrôle de L'/R .

Il est configuré avec L'/R=1 pour déplacer la direction normale, à droite. L'/R=1 active le multiplexeur ET les portes étiquetées R .

Cela permet aux données de suivre le chemin illustré par les flèches, lorsqu'une horloge est appliquée. Le chemin de connexion est le même que la figure « trop simple » « décaler à droite » ci-dessus.

Les données sont transférées à SR , à QA , à QB , à QC , où il part à la cascade SR . Cette épingle pourrait entraîner SR d'un autre appareil vers la droite.

Et si on changeait L’/R à L’/R=0 ?

Avec L’/R=0 , le multiplexeur ET les portes étiquetées L sont activés, donnant un chemin, indiqué par les flèches, le même que la figure ci-dessus "décaler à gauche".

Les données sont transférées à SL , à QC , à QB , à QA , où il part à SL cascade . Cette épingle pourrait entraîner SL d'un autre appareil vers la gauche.

La principale vertu des deux figures ci-dessus illustrant le « décalage du registre gauche/droite » est la simplicité.

Le fonctionnement de la commande gauche droite L’/R=0 est facile à suivre. Une partie commerciale a besoin du chargement de données parallèle impliqué par le titre de la section. Cela apparaît dans la figure ci-dessous.

Maintenant que nous pouvons déplacer à la fois vers la gauche et la droite via L'/R , ajoutons SH/LD’ , shift/load et les portes ET étiquetées « load » pour permettre le chargement parallèle des données à partir des entrées DA DB DC .

Lorsque SH/LD’=0 , ET portes R et L sont désactivés, ET les portes « chargement » sont activées pour transmettre les données DA DB DC aux entrées de données FF. la prochaine horloge CLK synchronisera les données sur QA QB QC .

Tant que les mêmes données sont présentes, elles seront rechargées sur les horloges suivantes. Cependant, les données présentes pour une seule horloge seront perdues des sorties lorsqu'elles ne seront plus présentes sur les entrées de données.

Une solution consiste à charger les données sur une horloge, puis à procéder au décalage sur les quatre horloges suivantes. Ce problème est résolu dans le 74ALS299 par l'ajout d'une autre porte ET au multiplexeur.

Si SH/LD’ est remplacé par SH/LD’=1 , les portes ET étiquetées « charge » sont désactivées, permettant le contrôle gauche/droite L’/R pour régler le sens de déplacement sur le L ou R ET portes. Le changement de vitesse est comme dans les figures précédentes.

La seule chose nécessaire pour produire un dispositif intégré viable est d'ajouter la quatrième porte ET au multiplexeur comme évoqué pour le 74ALS299.

Ceci est montré dans la section suivante pour cette partie.

Périphériques d'entrée/sortie parallèle et universels

Examinons de plus près les registres à décalage d'entrée série/sortie parallèle disponibles sous forme de circuits intégrés, avec l'aimable autorisation de Texas Instruments.

Pour les fiches techniques complètes des appareils, suivez les liens.

-

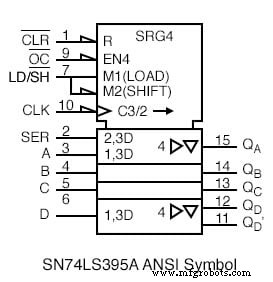

Registre à décalage 4 bits entrée/sortie parallèle SN74LS395A

-

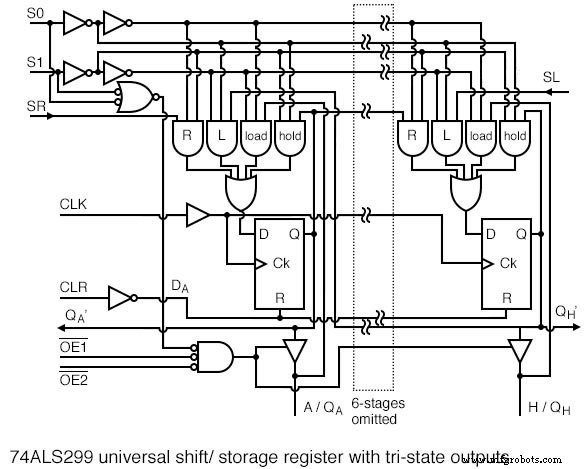

SN74ALS299 Registre à décalage universel 8 bits entrée/sortie parallèle

Nous avons déjà examiné les détails internes du SN74LS395A, voir la figure précédente, 74LS395 registre à décalage entrée/sortie parallèle avec sortie à trois états.

Directement au-dessus se trouve le symbole ANSI pour le 74LS395.

Pourquoi seulement 4 bits, comme indiqué par SRG4 au dessus? Le fait d'avoir à la fois des entrées parallèles et des sorties parallèles, en plus des broches de contrôle et d'alimentation, ne permet plus de bits d'E/S (entrée/sortie) dans un DIP (Dual Inline Package) à 16 broches.

R indique que les étages du registre à décalage sont réinitialisés par l'entrée CLR' (demi-flèche bas inverse active à l'entrée) de la section de commande en haut du symbole. OC' , lorsqu'il est bas, (inversez à nouveau la flèche) activera (EN4 ) les quatre tampons de sortie à trois états (QA QB QC QD ) dans la section données.

Charger/décaler’ (LD/SH’ ) à la broche (7) correspond aux internes M1 (charge) et M2 (changement). Recherchez les préfixes de 1 et 2 dans le reste du symbole pour déterminer ce qui est contrôlé par ceux-ci.

L'horloge sensible au front négatif (indiquée par la flèche inversée à la broche 10) C3/2 a deux fonctions.

Tout d'abord, les 3 de C3/2 affecte toute entrée ayant un préfixe de 3 , dites 2,3D ou 1,3D dans la section données.

Ce serait une charge parallèle à A, B, C, D attribué à M1 et C3 pour 1,3D . Deuxièmement, 2 de C3/2 -flèche droite indique la synchronisation des données partout où 2 apparaît dans un préfixe (2,3D à la broche 2).

Ainsi nous avons le pointage des données à SER dans QA avec le mode 2 . La flèche droite après C3/2 prend en compte le décalage aux étages de registre à décalage interne QA QB QC QD .

Les triangles pointant vers la droite indiquent la mise en mémoire tampon ; le triangle inversé indique trois états, contrôlé par le EN4 .

Notez que tous les 4 s dans le symbole associé au FR sont fréquemment omis. Étapes QB QC sont censés avoir les mêmes attributs que QD . QD ' passe en cascade au SER du package suivant à droite.

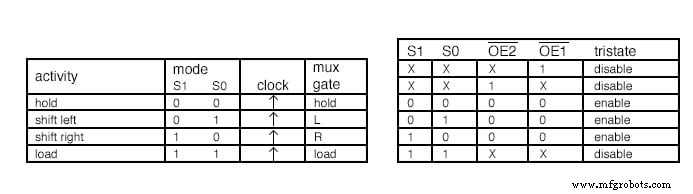

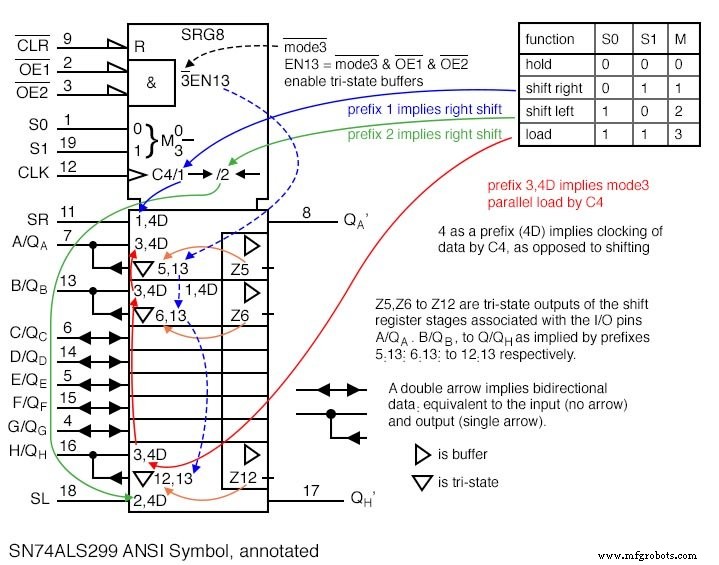

Le tableau ci-dessus, condensé à partir de la fiche technique data '299, résume le fonctionnement du registre à décalage/stockage universel 74ALS299.

Suivez le lien '299 ci-dessus pour plus de détails. Les portes du multiplexeur R , L , charger fonctionnent comme dans les figures précédentes "décaler le registre gauche/droit".

La différence est que le mode saisit S1 et S0 sélectionnez décalage à gauche, décalage à droite et charge avec le mode défini sur S1 S0 = au 01 , 10 , et 11 respectivement comme indiqué dans le tableau, activant les portes du multiplexeur L , R , et charger respectivement.

Voir le tableau. Une différence mineure est le chemin de charge parallèle à partir des sorties à trois états. En fait, les tampons à trois états sont (doivent être) désactivés par S1 S0 =11 faire flotter le bus d'E/S à utiliser comme entrées.

Un bus est un ensemble de signaux similaires. Les entrées sont appliquées à A , B par H (mêmes broches que QA , QB , via QH ) et acheminé vers la charge porte dans les multiplexeurs, et sur le D entrées des FF. Les données sont chargées en parallèle sur une impulsion d'horloge.

La seule nouvelle porte du multiplexeur est la porte ET étiquetée hold , activé par S1 S0 =00 . La prise gate active un chemin depuis le Q sortie du FF retour à la hold porte, à l'entrée D du même FF. Le résultat est qu'avec le mode S1 S0 =00 , la sortie est rechargée en permanence à chaque nouvelle impulsion d'horloge. Ainsi, les données sont conservées. Ceci est résumé dans le tableau.

Pour lire les données des sorties QA , QB , via QH , les tampons à trois états doivent être activés par OE2', OE1' =00 et mode =S1 S0 =00, 01 ou 10 .

C'est-à-dire que le mode est tout sauf load . Voir deuxième tableau.

Décalage à droite des données d'un paquet vers la gauche, décalages sur le SR saisir. Toutes les données décalées vers la droite de l'étape QH cascade vers la droite via QH '.

Cette sortie n'est pas affectée par les tampons à trois états. La séquence de décalage vers la droite pour S1 S0 =10 est :

SR> QA> QB> QC> QD> QE> QF> QG> QH (QH ')

Décaler à gauche les données d'un paquet vers la droite sur le SL saisir. Toutes les données décalées vers la gauche de l'étape QA cascade vers la gauche via QA ', également non affecté par les tampons à trois états. La séquence de décalage à gauche pour S1 S0 =01 est :

(QA ') QR

Le décalage peut avoir lieu avec les tampons à trois états désactivés par l'un des OE2' ou OE1' =1 . Cependant, les sorties du contenu du registre ne seront pas accessibles. Voir tableau.

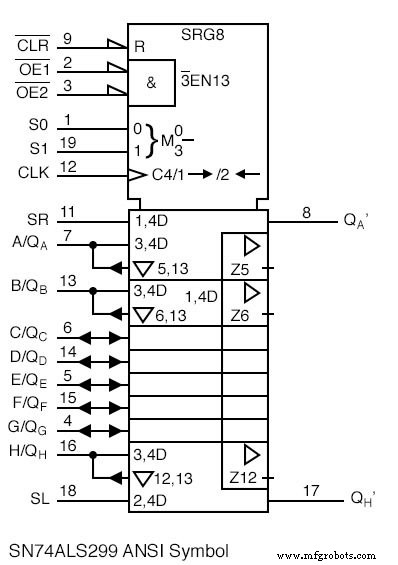

Le symbole ANSI "propre" pour le registre à décalage universel 8 bits à entrée/sortie parallèle SN74ALS299 avec sortie à trois états est indiqué ci-dessus à titre de référence.

La version annotée du symbole ANSI est montrée pour clarifier la terminologie qui y est contenue.

A noter que le mode ANSI (S0 S1) est inversé par rapport à l'ordre (S1 S0) utilisé dans le tableau précédent.

Cela inverse les nombres en mode décimal (1 et 2). En tout état de cause, nous sommes entièrement d'accord avec la fiche technique officielle, copiant cette incohérence.

Applications pratiques

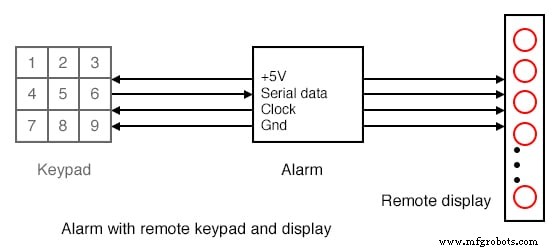

Le schéma fonctionnel Alarme avec clavier à distance est répété ci-dessous. Auparavant, nous avons construit le lecteur de clavier et l'affichage à distance en tant qu'unités distinctes.

Nous allons maintenant combiner à la fois le clavier et l'affichage en une seule unité à l'aide d'un registre à décalage universel.

Bien que séparés dans le schéma, le clavier et l'affichage sont tous deux contenus dans le même boîtier distant.

Nous allons charger en parallèle les données du clavier dans le registre à décalage sur une seule impulsion d'horloge, puis les déplacer vers la boîte d'alarme principale.

Dans le même temps, nous déplacerons les données LED de l'alarme principale vers le registre à décalage distant pour éclairer les LED.

Nous déplacerons simultanément les données du clavier et les données des LED dans le registre à décalage.

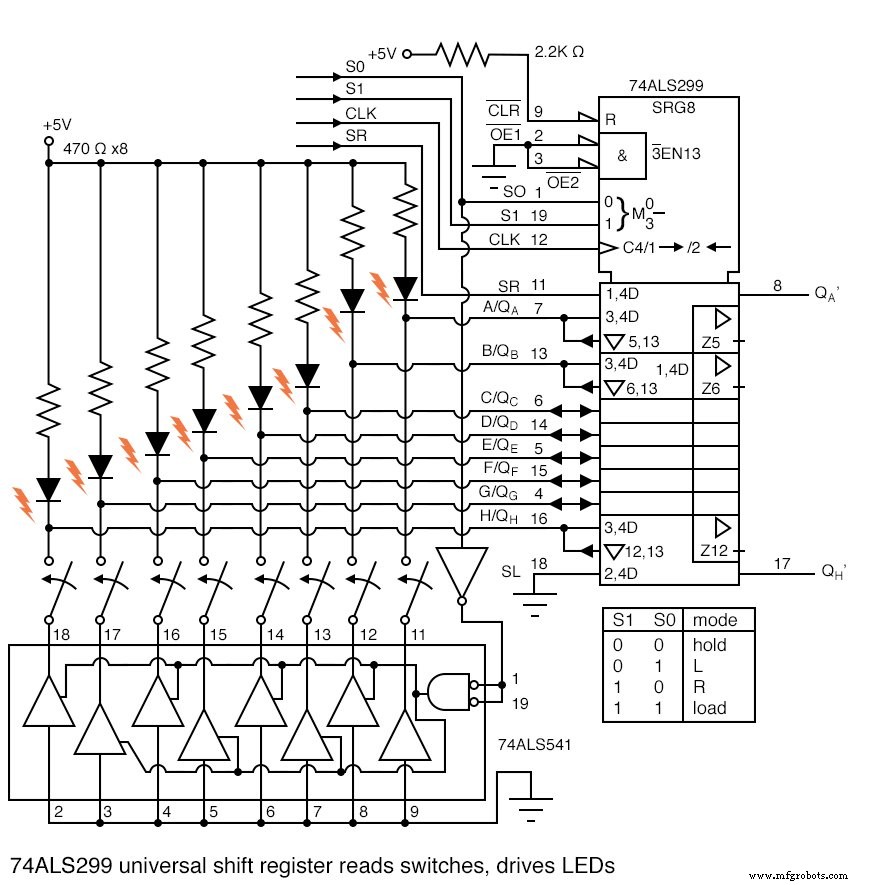

Huit LED et résistances de limitation de courant sont connectées aux huit broches d'E/S du registre à décalage universel 74ALS299.

Les LEDS ne peuvent être pilotées qu'en Mode 3 avec S1=0 S0=0 . Le OE1' et OE2' Les activations à trois états sont mises à la terre pour activer en permanence les sorties à trois états pendant les modes 0, 1, 2 .

Cela provoquera l'allumage (scintillement) des LED pendant le changement de vitesse. S'il s'agissait d'un problème, le EN1 ' et EN2' pourrait être sans fondement et mis en parallèle avec S1 et S0 respectivement pour n'activer que les buffers à trois états et allumer les LEDS pendant le maintien, mode 3 . Restons simples pour cet exemple.

Pendant le chargement parallèle, S0=1 inversé à 0, permet aux tampons octaux à trois états de mettre à la terre les essuie-glaces des commutateurs.

Les contacts de commutation supérieurs ouverts sont tirés au niveau logique haut par la combinaison résistance-LED sur les huit entrées.

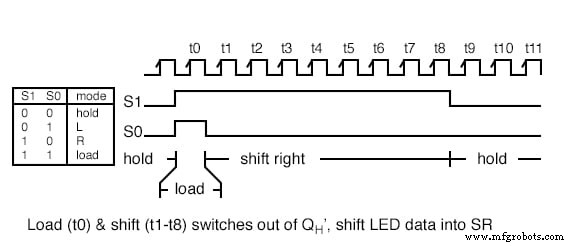

Toute fermeture de commutateur court-circuitera le niveau d'entrée bas. Nous chargeons en parallèle les données du commutateur dans le '299 à l'heure t0 lorsque les deux S0 et S1 sont élevés. Voir les formes d'onde ci-dessous.

Une fois S0 baisse, huit horloges (t0 àt8 ) les données de fermeture du commutateur de changement de vitesse sur le '299 via le Qh ' épingle.

Dans le même temps, de nouvelles données LED sont transférées à SR des 299 par les mêmes huit horloges. Les données LED remplacent les données de fermeture de l'interrupteur au fur et à mesure que le changement de vitesse se poursuit.

Après le 8e quart de travail, t8 , S1 passe au niveau bas pour le mode de maintien du rendement (S1 S0 =00 ). Les données dans le registre à décalage restent les mêmes même s'il y a plus d'horloges, par exemple, T9 , t10 , etc.

D'où viennent les formes d'onde ? Ils pourraient être générés par un microprocesseur si la fréquence d'horloge n'était pas supérieure à 100 kHz, auquel cas, il serait gênant de générer des horloges après t8 .

Si l'horloge était dans la plage des mégahertz, l'horloge fonctionnerait en continu. L'horloge, S1 et S0 serait généré par la logique numérique, non illustré ici.

FICHES DE TRAVAIL CONNEXES :

- Feuille de travail des registres à décalage

Technologie industrielle