Conception embarquée avec FPGA :ressources matérielles

Note de l'éditeur :alors que des algorithmes avancés continuent d'émerger pour la conception de produits intelligents, les développeurs ont souvent du mal à mettre en œuvre des systèmes embarqués capables de répondre aux demandes de traitement associées de ces algorithmes. Les FPGA peuvent fournir les performances requises, mais la conception avec des FPGA a longtemps été considérée comme limitée aux experts en programmation FPGA. Aujourd'hui, cependant, la disponibilité de FPGA plus puissants et d'environnements de développement plus efficaces a rendu le développement de FPGA largement accessible. Dans cet extrait, chapitre 4 du livre Architecting High-Performance Embedded Systems, l'auteur propose une revue complète des périphériques FPGA, des langages d'implémentation et du processus de développement FPGA, ainsi qu'une procédure détaillée sur la façon de commencer à implémenter des FPGA dans votre propre conception. L'extrait complet est présenté dans la série de fascicules suivante :

Note de l'éditeur :alors que des algorithmes avancés continuent d'émerger pour la conception de produits intelligents, les développeurs ont souvent du mal à mettre en œuvre des systèmes embarqués capables de répondre aux demandes de traitement associées de ces algorithmes. Les FPGA peuvent fournir les performances requises, mais la conception avec des FPGA a longtemps été considérée comme limitée aux experts en programmation FPGA. Aujourd'hui, cependant, la disponibilité de FPGA plus puissants et d'environnements de développement plus efficaces a rendu le développement de FPGA largement accessible. Dans cet extrait, chapitre 4 du livre Architecting High-Performance Embedded Systems, l'auteur propose une revue complète des périphériques FPGA, des langages d'implémentation et du processus de développement FPGA, ainsi qu'une procédure détaillée sur la façon de commencer à implémenter des FPGA dans votre propre conception. L'extrait complet est présenté dans la série de fascicules suivante :

1 :Ressources matérielles (cet article)

2 :Langages d'implémentation

3 :Processus de développement

4 :Construire un projet

5 :Implémentation

Adapté de Architecting High-Performance Embedded Systems, par Jim Ledin.

Développement de votre premier programme FPGA

Ce chapitre commence par une discussion sur l'utilisation efficace des dispositifs FPGA dans les systèmes embarqués temps réel et se poursuit par une description des éléments fonctionnels contenus dans les FPGA standard. La gamme de langages de conception FPGA, y compris le Matériel Langues de description (HDL ), les méthodes de diagramme de blocs et les langages de programmation de logiciels populaires, notamment C et C++, sont introduits. Le chapitre se poursuit par un aperçu du processus de développement FPGA et se termine par un exemple complet d'un cycle de développement FPGA commençant par un énoncé des exigences du système et se terminant par un système fonctionnel implémenté dans une carte de développement FPGA à faible coût.

Après avoir terminé ce chapitre, vous saurez comment les FPGA peuvent être appliqués dans les architectures de systèmes embarqués temps réel et comprendrez les composants qui constituent un circuit intégré FPGA. Vous aurez appris les langages de programmation utilisés dans la conception d'algorithmes FPGA et comprendrez la séquence d'étapes pour développer une application basée sur FPGA. Vous aurez également travaillé sur un exemple de développement FPGA complet sur une carte de développement à faible coût en utilisant des outils logiciels FPGA gratuits.

Nous aborderons les sujets suivants dans ce chapitre :

- Utiliser des FPGA dans des conceptions de systèmes embarqués en temps réel

- Langages d'implémentation FPGA

- Le processus de développement FPGA

- Développer votre premier projet FPGA

Exigences techniques

Les fichiers de ce chapitre sont disponibles sur https://github.com/PacktPublishing/Architecting-High-Performance-Embedded-Systems.

Utilisation des FPGA dans les conceptions de systèmes embarqués en temps réel

Comme nous l'avons vu dans les Eléments de FPGA section du Chapitre 1 , Architecte Haute Performance Systèmes embarqués , un périphérique FPGA typique contient un grand nombre de tables de recherche, de bascules, d'éléments RAM de bloc, de tranches DSP et d'autres composants. Bien qu'il puisse être instructif de comprendre les capacités détaillées de chacun de ces composants, de telles préoccupations ne sont pas nécessairement informatives pendant le processus de développement du FPGA. La contrainte la plus importante à garder à l'esprit est qu'un numéro de pièce FPGA spécifique contient un nombre fini de chacun de ces éléments, et une conception ne peut pas dépasser ces limites lorsqu'elle est ciblée sur ce modèle FPGA particulier.

Au lieu de cela, il est plus productif de voir le processus de développement du FPGA du point de vue de l'énoncé des exigences du système embarqué. Vous pouvez commencer à développer la conception FPGA ciblée sur un modèle FPGA choisi de manière quelque peu arbitraire. Au fur et à mesure que le développement progresse, vous pouvez atteindre une limite de ressources ou identifier une fonctionnalité FPGA requise par la conception qui n'est pas présente dans le FPGA actuellement ciblé. À ce stade, vous pouvez sélectionner une cible différente, plus performante, et poursuivre le développement.

Alternativement, alors que le développement de la conception touche à sa fin, vous pouvez réaliser que le FPGA cible que vous avez sélectionné à l'origine contient des ressources excessives et la conception pourrait être améliorée en sélectionnant un FPGA plus petit, avec des avantages potentiels en termes de coût inférieur, moins de broches, plus petite taille de boîtier, et une consommation d'énergie réduite.

Dans l'une ou l'autre de ces situations, il est généralement simple de basculer le FPGA ciblé vers un modèle différent au sein de la même famille. Les outils de développement et les artefacts de conception que vous avez créés à ce stade doivent être entièrement réutilisables avec le modèle FPGA nouvellement ciblé. S'il devient nécessaire de passer à une autre famille de FPGA du même fournisseur, ou à un modèle d'un autre fournisseur, le basculement nécessitera probablement plus de travail.

Le but de cette discussion est de souligner qu'il n'est pas trop important d'identifier un modèle de FPGA spécifique au début d'un effort de développement de système embarqué hautes performances. Au lieu de cela, les premières considérations devraient se concentrer sur la validation de la décision d'utiliser un FPGA dans le cadre de la conception, puis, si le FPGA est la meilleure approche de conception, procéder à la sélection d'un fournisseur de FPGA et d'une famille de périphériques appropriés.

Les exemples de projets dans ce livre seront basés sur la famille Xilinx Vivado d'outils de développement FPGA. Bien qu'une licence Vivado doive être achetée pour développer certaines familles de FPGA Xilinx, les dispositifs FPGA de l'Artix-7 avec lesquels nous allons travailler sont pris en charge gratuitement par Vivado. La famille Artix-7 FPGA combine les attributs de hautes performances, de faible consommation d'énergie et de coût total du système réduit. Des familles de dispositifs FPGA et des suites d'outils de développement similaires sont disponibles auprès d'autres fournisseurs de FPGA.

Le développement de FPGA est un processus assez complexe, avec une variété de types d'entrée de données d'analyse et de conception requis. Pour éviter de discuter de ces sujets à un niveau trop abstrait et pour présenter des résultats concrets en termes d'exemples de projets de travail, nous utiliserons Vivado tout au long du livre. Une fois que vous vous êtes familiarisé avec les outils et techniques décrits ici, vous devriez être en mesure de les appliquer à l'aide d'outils similaires d'autres fournisseurs.

Les sections suivantes discuteront de certaines caractéristiques de différenciation clés des familles de FPGA et des modèles individuels au sein de ces familles, y compris la quantité de RAM de bloc, la quantité et les types de signaux d'E/S disponibles, les ressources matérielles spécialisées sur puce et l'inclusion de un ou plusieurs cœurs de processeur matériel dans le package FPGA.

Bloquer la RAM et la RAM distribuée

Bloquer la RAM est utilisé pour implémenter des régions de mémoire dans un FPGA. Une région mémoire particulière est spécifiée en termes de largeur en bits (généralement 8 ou 16 bits) et de profondeur, qui définit le nombre d'emplacements de stockage dans la région mémoire.

La quantité totale de RAM de bloc dans un FPGA est généralement spécifiée en termes de kilobits (Ko ). La quantité de RAM de bloc disponible varie selon les familles de FPGA et parmi les modèles au sein d'une famille particulière. Comme on peut s'y attendre, les pièces plus grosses et plus chères ont généralement une plus grande quantité de ressources qui peuvent être utilisées comme bloc de RAM.

Dans les FPGA Xilinx, et à des degrés divers dans les FPGA d'autres fournisseurs, une catégorie distincte de mémoire appelée RAM distribuée est disponible en plus de la RAM de bloc. RAM distribuée est construit à partir des éléments logiques utilisés dans les tables de consultation et réutilise les circuits de ces dispositifs pour former de minuscules segments de RAM, chacun contenant 16 bits. Ces segments peuvent être agrégés pour former des blocs de mémoire plus grands si nécessaire.

La RAM de bloc a tendance à être utilisée à des fins traditionnellement associées à la RAM, telles que la mise en œuvre de la mémoire cache du processeur ou comme tampon de stockage pour les données d'E/S. La RAM distribuée peut être utilisée à des fins telles que le stockage temporaire des résultats de calcul intermédiaires. Étant donné que la RAM distribuée est basée sur des circuits de table de recherche, l'utilisation de RAM distribuée dans une conception réduit les ressources disponibles pour la mise en œuvre des opérations logiques.

La RAM de bloc peut avoir un seul port ou deux ports. La RAM de bloc à port unique représente le modèle d'utilisation courant d'un processeur qui lit et écrit la RAM pendant le fonctionnement.

La RAM de bloc à deux ports fournit deux ports de lecture/écriture, qui peuvent tous deux lire ou écrire activement la même région de mémoire simultanément.

La RAM de bloc à deux ports est idéale pour les situations où des données sont transférées entre des parties d'un FPGA fonctionnant à des vitesses d'horloge différentes. Par exemple, un sous-système d'E/S peut avoir une vitesse d'horloge de quelques centaines de MHz lorsqu'il reçoit un flux de données entrant. Le sous-système d'E/S écrit les données entrantes dans le bloc RAM lorsqu'elles arrivent via l'un des canaux d'E/S haute vitesse du FPGA. Un sous-système distinct au sein du FPGA, fonctionnant à une vitesse d'horloge différente, peut lire les données du deuxième port du bloc RAM sans interférer avec le fonctionnement du sous-système d'E/S.

Block RAM peut également fonctionner en premier entré, premier sorti (FIFO ) mode. Dans l'exemple du flux de données série entrant, le sous-système d'E/S peut insérer des mots de données dans la FIFO au fur et à mesure qu'ils arrivent et le sous-système de traitement peut les lire dans le même ordre. La RAM de bloc en mode FIFO fournit des signaux indiquant si la FIFO est pleine, vide, presque pleine ou presque vide. Les définitions de presque complète et presque vide relèvent du concepteur du système. Si vous attribuez presque vide pour signifier qu'il reste moins de 16 éléments dans le FIFO, vous pouvez alors être assuré que chaque fois que le FIFO n'indique pas qu'il est presque vide, vous pouvez lire 16 éléments sans autre vérification de la disponibilité des données.

Lors de l'utilisation de la RAM de bloc en mode FIFO, il est essentiel que la logique d'insertion d'éléments dans la FIFO ne tente jamais d'écrire lorsque la FIFO est pleine et que la logique de lecture de la FIFO ne tente jamais de lire lorsque la FIFO est vide. Si l'un de ces événements se produit, le système perdra des données ou tentera de traiter des données non définies.

Broches d'E/S FPGA et fonctionnalités associées

Étant donné que les FPGA sont destinés à être utilisés dans des applications hautes performances, leurs broches d'E/S sont généralement capables d'implémenter une variété de normes d'E/S haute vitesse. Lors de la mise en œuvre d'une conception avec une suite d'outils de développement FPGA, le développeur du système doit effectuer des tâches qui incluent l'attribution de fonctions à des broches particulières sur le boîtier FPGA et la configuration de chacune de ces broches pour qu'elle fonctionne avec la norme d'interface appropriée. Des étapes supplémentaires doivent être effectuées pour associer les signaux d'entrée et de sortie dans le code de modèle FPGA avec les broches de boîtier correctes.

Au niveau des broches, les signaux d'E/S individuels sont soit asymétriques, soit différentiels.

Un signal asymétrique est référencé au sol. Logique Transistor-Transistor traditionnelle (TTL ) et Semiconducteur à oxyde métallique complémentaire (CMOS ) les signaux numériques fonctionnent sur une plage de 0 à 5 VCC par rapport à la terre.

Les FPGA modernes ne prennent généralement pas en charge la plage de signaux 5 VDC héritée, mais prennent en charge les signaux TTL et CMOS fonctionnant sur une plage de tension réduite, réduisant ainsi la consommation d'énergie et améliorant la vitesse. TTL basse tension (LVTTL ) fonctionnent sur une plage de 0 à 3,3 V CC. CMOS basse tension (LVCMOS ) sont sélectionnables avec des tensions de signalisation de 1,2, 1,5, 1,8, 2,5 et 3,3 V. Ces types de signaux sont nommés LVCMOS12, LVCMOS15, LVCMOS18, LVCMOS25 et LVCMOS33. D'autres types de signaux asymétriques hautes performances sont disponibles, notamment la Logique d'émetteur-récepteur haute vitesse (HSTL ) et Stub-Series Termination Logic (SSTL ).

Les signaux asymétriques sont largement utilisés à des fins de basse fréquence, telles que la lecture des entrées de bouton-poussoir et l'éclairage des LED. Les signaux asymétriques sont également utilisés dans de nombreux protocoles de communication à faible vitesse tels que I2C et SPI. Un inconvénient important des signaux asymétriques est que tout bruit couplé dans les fils et les pistes de la carte de circuit imprimé transportant le signal a le potentiel de corrompre l'entrée du récepteur. Ce problème peut être considérablement réduit grâce à l'utilisation de la signalisation différentielle.

Pour les taux de transfert de données les plus élevés, la signalisation différentielle est l'approche privilégiée.

Signaux différentiels utilisez une paire de broches d'E/S et dirigez des signaux opposés sur les deux broches.

En d'autres termes, une broche est entraînée à une tension plus élevée et l'autre à une tension inférieure pour représenter un bit de données 0 et les tensions des broches sont inversées pour représenter un bit 1. Le récepteur différentiel soustrait les deux signaux pour déterminer si le bit de données est 0 ou 1. Étant donné que les deux fils ou traces transportant le signal différentiel sont physiquement situés très près l'un de l'autre, tout bruit qui se couple dans l'un des signaux se couplera à l'autre. d'une manière très similaire. L'opération de soustraction supprime la grande majorité du bruit, permettant un fonctionnement fiable à des taux de transfert de données beaucoup plus élevés que les signaux asymétriques.

Un certain nombre de normes de signaux différentiels sont prises en charge par les FPGA standard. Plusieurs versions différentielles de HSTL et SSTL sont définies, avec une variété de niveaux de tension de signalisation pour chacune.

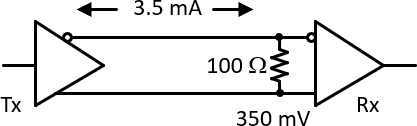

Signalisation différentielle basse tension (LVDS ) a été introduit en tant que norme en 1994 et continue d'être utilisé dans diverses applications. Un émetteur de signalisation LVDS produit un courant constant de 3,5 mA et change la direction du courant circulant dans la résistance du récepteur pour produire des changements d'état représentant les valeurs de données 0 et 1 comme indiqué sur la Figure 4.1 :

Figure 4.1 – Interface LVDS

Dans la communication LVDS, comme dans les autres normes de signalisation différentielle et asymétrique, il est important que l'impédance du chemin de communication entre l'émetteur et le récepteur corresponde étroitement à l'impédance de terminaison, qui est de 100 ohms dans le cas du LVDS. Si l'impédance du canal de communication ne correspond pas à l'impédance de terminaison, des réflexions peuvent se produire sur la ligne, empêchant une réception fiable des données.

L'impédance des paires de traces de signaux différentiels est fonction de la géométrie des traces de paires et de leur relation avec le plan de masse. Comme nous le verrons au Chapitre 6 , Conception de circuits avec KiCad , il est simple de concevoir des circuits imprimés qui satisfont aux exigences des normes de signalisation différentielle à grande vitesse.

Ressources matérielles spécialisées

Les FPGA incluent généralement une sélection de ressources matérielles dédiées pour les fonctions qui sont couramment requises et sont soit implémentées plus efficacement dans le matériel plutôt que d'utiliser des fonctions FPGA synthétisées, soit impossibles à implémenter avec des composants FPGA. Voici quelques exemples de ces ressources :

- Interfaces vers la RAM dynamique externe (DRAM ) pour stocker de grandes quantités de Ces interfaces prennent généralement en charge une norme DRAM commune telle que DDR3.

- Convertisseurs analogique-numérique.

- Boucles à verrouillage de phase, utilisées pour générer plusieurs fréquences d'horloge.

- Traitement du signal numérique multiplier-accumuler (MAC ) matériel.

Ces ressources matérielles permettent le développement de systèmes complexes avec des capacités étendues. Un matériel dédié est fourni pour des fonctions telles que l'opération MAC, car les performances matérielles sont nettement meilleures que la fonctionnalité équivalente synthétisée utilisant des ressources logiques FPGA.

Noyaux de processeur

Certaines familles de FPGA incluent des cœurs de processeurs matériels dans le but de combiner une vitesse d'exécution logicielle maximale avec les avantages de performances des algorithmes implémentés par FPGA. Par exemple, la famille Xilinx Zynq-7000 intègre un processeur matériel ARM Cortex-A9 avec une structure FPGA traditionnelle.

Les conceptions FPGA qui ne nécessitent pas de processeur matériel peuvent implémenter un processeur utilisant les ressources FPGA, appelé processeur logiciel . Les processeurs logiciels sont hautement configurables, bien qu'ils ne soient généralement pas capables d'égaler les performances d'un processeur implémenté dans le matériel.

La section suivante présentera les principaux langages de programmation et méthodes de saisie de données utilisés pour développer des algorithmes FPGA.

Réimprimé avec la permission de Packt Publishing. Copyright © 2021 Édition Packt

Jim Ledin est le PDG de Ledin Engineering, Inc. Jim est un expert en conception, développement et test de logiciels et de matériel embarqués. Il est également accompli dans l'évaluation de la cybersécurité des systèmes embarqués et les tests d'intrusion. Il a un B.S. diplôme en génie aérospatial de l'Iowa State University et un M.S. diplôme en génie électrique et informatique du Georgia Institute of Technology. Jim est un ingénieur électricien professionnel enregistré en Californie, un professionnel certifié de la sécurité des systèmes d'information (CISSP), un hacker éthique certifié (CEH) et un testeur de pénétration certifié (CPT).

Jim Ledin est le PDG de Ledin Engineering, Inc. Jim est un expert en conception, développement et test de logiciels et de matériel embarqués. Il est également accompli dans l'évaluation de la cybersécurité des systèmes embarqués et les tests d'intrusion. Il a un B.S. diplôme en génie aérospatial de l'Iowa State University et un M.S. diplôme en génie électrique et informatique du Georgia Institute of Technology. Jim est un ingénieur électricien professionnel enregistré en Californie, un professionnel certifié de la sécurité des systèmes d'information (CISSP), un hacker éthique certifié (CEH) et un testeur de pénétration certifié (CPT). Contenus associés :

- Les outils open source aident à simplifier la programmation FPGA

- Implémentation d'algorithmes à virgule flottante dans les FPGA ou les ASIC

- Tirer parti des FPGA pour l'apprentissage en profondeur

- Les outils logiciels migrent le code GPU vers les FPGA pour les applications d'IA

- Les FPGA remplacent les ASIC dans les ADAS basés sur la vision Subaru Eyesight

- Comment les FPGA Flash simplifient les exigences de sécurité fonctionnelle

- Tirer parti des avantages des FPGA instantanés

- Configuration FPGA utilisant un flash NOR haute vitesse

- Comment la technologie FPGA évolue pour répondre aux nouvelles exigences système de milieu de gamme

Pour plus d'informations sur Embedded, abonnez-vous à la newsletter hebdomadaire d'Embedded.

Embarqué

- Comment éviter les surprises coûteuses dans la conception de matériel connecté

- Qu'est-ce que la conception de systèmes embarqués :étapes du processus de conception

- Simplifier le développement IoT avec Eclipse IoT

- Développement de machines à états avec développement piloté par les tests

- Cypress :ModusToolbox Suite simplifie la conception de l'IoT

- Treillis :MachX03D FPGA améliore la sécurité avec des capacités matérielles de racine de confiance

- Kit de conception mesure la tension artérielle avec capteur optique

- Java 9 - Amélioration de Try With Resources

- Tout compris avec additif