Le processeur croisé à faible coût prend en charge l'inférence de point de terminaison

BRISTOL, Royaume-Uni — XMOS a adapté son cœur de processeur Xcore pour l'apprentissage automatique, créant un processeur croisé pour les applications AIoT. Le Xcore.ai sera disponible à partir de 1 $.

Xcore.ai, la troisième génération de produits basés sur la conception de base exclusive de l'entreprise, est conçue pour l'inférence et la prise de décision en temps réel dans les terminaux, et peut également gérer les fonctions de traitement du signal, de contrôle et de communication.

La nouveauté de cette puce de troisième génération est une capacité de pipeline vectoriel pour les applications d'apprentissage automatique. Il s'agit du seul processeur croisé de ce type à prendre en charge les réseaux de neurones binarisés (1 bit), qui gagnent en importance pour l'IA à très faible consommation dans les applications de point de terminaison, car ils offrent une amélioration de l'ordre de grandeur des performances et de la densité de mémoire échangée. pour une réduction modeste de la précision (le Xcore.ai prend également en charge les nombres 32 bits, 16 bits et 8 bits).

Le Xcore.ai rejoint une nouvelle classe de systèmes sur puces compatibles avec l'IA pour les applications de point de terminaison, le processeur croisé (Image :XMOS)

Xcore.ai rejoint une classe émergente de processeurs de point de terminaison avec capacité d'IA, le processeur croisé. Inventé par NXP, ce terme décrit une nouvelle catégorie importante d'appareils avec les performances d'un processeur d'application combinées à la facilité d'utilisation, la faible consommation d'énergie et le fonctionnement en temps réel d'un microcontrôleur.

« Si vous parlez aux clients de « microcontrôleurs », ils pensent aux appareils Cortex-M0, M3 ou M4 qui coûtent 75 centimes ou moins, avec des performances relativement faibles, une centaine de MIPS environ. Ensuite, les « SoC » pourraient être quelque chose avec des cœurs quad-A53, qui fonctionnent à un gigahertz. Il y a un grand écart pour les choses au milieu, comme les processeurs pour la voix, qui est un problème mathématique particulièrement difficile, nécessitant des milliers de MIPS. Il y a donc ce grand écart avec un domaine d'application vraiment vaste et important au milieu, et il mérite un nom », a déclaré Mark Lippett, PDG de XMOS, dans une interview exclusive avec EETimes.

Interfaces vocales

Le produit de deuxième génération annoncé précédemment par la société, le XVF3510, a été lancé en juillet 2019 en tant qu'ASIC pour les interfaces vocales, mais sous le capot, le silicium est également basé sur la conception Xcore exclusive de la société, livrée avec le micrologiciel. Les conceptions de référence pour les solutions vocales en champ lointain basées sur le XVF3510 sont qualifiées pour le service vocal Alexa d'Amazon.

Compte tenu de l'histoire de XMOS dans le secteur de la voix, il n'est pas surprenant que la puce Xcore.ai soit initialement destinée aux applications d'interface vocale qui nécessitent l'IA pour la détection de mots clés ou les fonctions de dictionnaire.

« Soyons absolument clairs, la voix est la charge de travail d'IA la plus importante au niveau du terminal, et le restera probablement pendant un certain temps encore. Mais pour améliorer les interfaces vocales, vous constaterez que les appareils deviendront plus multimodaux », a déclaré Lippett, décrivant une tendance à utiliser différents types de capteurs pour rendre les applications plus sensibles au contexte, qu'il s'agisse de détecter la présence d'une personne ou de détecter où ils parlent.

Mark Lippett (Image :XMOS)

"Il existe de nombreuses possibilités d'améliorer l'expérience utilisateur non seulement en écoutant de l'audio, mais en faisant plus que cela", a-t-il déclaré.

De nombreuses applications pour l'IA dans les appareils IoT reposent sur une combinaison de confidentialité, de sécurité et de sûreté qui nécessite que le traitement soit effectué au point de terminaison. Lippett a décrit les fonctions de sécurité des appareils qui utilisent la voix et le radar pour éteindre le four si seuls des enfants sont présents dans la cuisine, par exemple.

Xcore.ai ira donc sur le marché avec des bibliothèques prévues pour la création d'interfaces vocales, mais Lippett a déclaré qu'il disposait d'une capacité de réserve pour que les clients puissent construire leurs propres systèmes. Une interface MIPI est incluse pour l'entrée de la caméra.

Architecture Xcore

La puce Xcore.ai délivre jusqu'à 3200 MIPS, 51,2 GMACC et 1600 MFLOPS. Il dispose d'1 Mo de SRAM intégrée et d'une interface DDR basse consommation pour l'extension.

Par rapport à un appareil Cortex-M7 qui offre à peu près le même niveau d'intégration que Xcore.ai, fonctionnant à une fréquence de fonctionnement similaire, les propres chiffres de XMOS attribuent leur part à 32 fois les performances de traitement de l'IA et 15 fois les performances DSP.

"Dans le monde des terminaux, il doit s'agir d'un rapport qualité-prix, il ne sert à rien de parler de l'un sans l'autre", a déclaré Lippett. « Nous avons été très agressifs sur le prix, nous pouvons descendre à 1 $ pour cette pièce [en volume]. D'une manière générale, nous sommes environ la moitié du coût [de l'appareil Cortex-M7 comparable] et nous le faisons sauter hors de l'eau en termes de performances. »

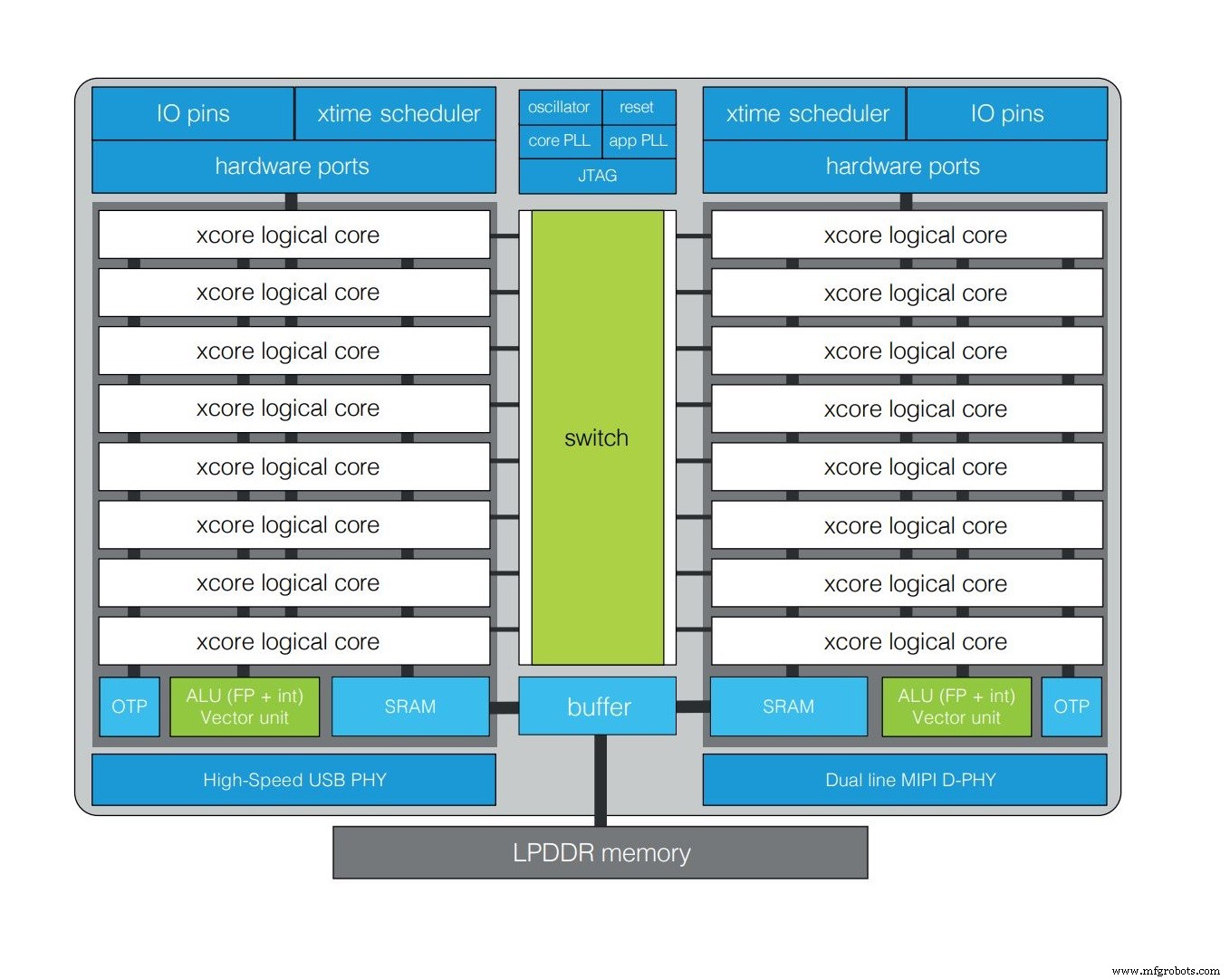

Le Xcore est basé sur des cœurs logiques disposés en tuiles avec mémoire,

ALU et unités vectorielles (Image :XMOS)

Xcore.ai est basé sur l'architecture Xcore propriétaire de XMOS. Le Xcore lui-même est construit sur des blocs de construction appelés cœurs logiques, qui peuvent être utilisés pour les E/S, le DSP, les fonctions de contrôle ou l'accélération AI. Il y a huit cœurs logiques sur chaque tuile, avec deux tuiles dans chaque puce Xcore.ai, et les concepteurs peuvent choisir le nombre de cœurs à allouer à chaque fonction. Chaque tuile contient également de la mémoire, des ALU et une unité vectorielle à laquelle les cœurs logiques partagent l'accès.

« De manière critique, ils [partagent l'accès] d'une manière très prévisible », a déclaré Lippett. « C'est ce qui est spécial avec le Xcore. Au départ, nous voulions offrir une flexibilité d'E/S aux ingénieurs logiciels, et le matériel n'est pas très tolérant si vous dépassez les délais. Ainsi, le Xcore est multicœur, non pas parce que nous voulons répartir les charges de travail et faire les choses très rapidement — nous pouvons le faire — mais en réalité c'est multicœur parce que nous voulons donner à certaines parties de l'application leurs propres ressources, de sorte que lorsque c'est nécessaire, c'est prêt. Il est conçu de bas en haut pour offrir ce type de précision de synchronisation. »

Le mappage de différentes fonctions (E/S, DSP, contrôle, AI) aux cœurs logiques du firmware permet la création d'un « SoC virtuel », entièrement écrit en logiciel. Dans l'exemple ci-dessous, un cœur effectue des tâches qui seraient normalement effectuées dans le matériel, telles que I 2 S, je 2 Les pilotes C et LED, et certains cœurs traitent le réseau de neurones, tandis que d'autres effectuent des tâches qui seraient normalement effectuées par logiciel. Définir tout cela dans un logiciel est plus rapide, pour répondre aux demandes transitoires des appareils IoT. Le développement est également moins cher, a déclaré Lippett, permettant aux entreprises de créer des solutions économiques même dans les segments de marché plus petits.

Un exemple d'application mappée sur un appareil Xcore.ai (Image :XMOS)

"La façon dont nous voyons l'évolution du marché est que le marché exige des fonctionnalités plus diversifiées, et les entreprises devront réagir plus rapidement", a déclaré Lippett. « Il est très difficile de parier sur l'IoT pendant deux ans sans créer une plate-forme très générique qui pourrait ne pas [éventuellement] être assez bonne pour aucun segment. [Avec le Xcore.ai], il est beaucoup plus facile de mettre des appareils sur le marché beaucoup plus rapidement, avec moins d'investissements, et de placer efficacement des paris plus petits sur des marchés plus petits et de rendre ces marchés économiques. »

Comment XMOS rivalisera-t-il avec les grands fabricants de microcontrôleurs s'installant dans cet espace de processeurs croisés ?

« Pas en construisant des SoC basés sur ARM ! Parce qu'ils le font très bien », a déclaré Lippett. « La seule façon de rivaliser avec ces gars-là est d'avoir un avantage architectural. Il s'agit des capacités intrinsèques du Xcore en termes de performances, mais aussi de flexibilité. »

Embarqué

- Renesas met l'accent sur l'intelligence des terminaux au salon Embedded World 2019

- Les MCU ciblent les conceptions sécurisées de points de terminaison et de périphérie IoT

- Les modules de processeur sans fil pré-certifiés disposent d'une connectivité Bluetooth Mesh

- L'utilisation de plusieurs puces d'inférence nécessite une planification minutieuse

- PMIC simplifie les conceptions de processeurs multi-rails

- Petit circuit intégré haptique prenant en charge les appareils portables à faible consommation

- Processeur multicœur intégrant une unité de traitement neuronal

- Le radar sur puce à 60 GHz prend en charge les exigences de l'industrie automobile

- IC de gestion de l'alimentation prend en charge la famille de processeurs d'application