Xilinx améliore les performances RFSoC avec une adresse IP numérique frontale pour les radios 5G

Xilinx a annoncé son dispositif frontal numérique (DFE) Zynq RFSoC conçu pour les déploiements 5G New Radio (NR). S'appuyant sur l'architecture Zynq UltraScale de l'entreprise, le Zynq RFSoC DFE étend la famille Xilinx RFSoC avec une implémentation IP matérielle des fonctions gourmandes en calcul nécessaires pour prendre en charge efficacement la 5G NR ainsi que la 4G héritée dans les unités radio (RU) 5G émergentes.

Pour tout son potentiel, la 5G pose de multiples défis aux développeurs d'infrastructures 5G. Alors que les concepteurs de smartphones et d'autres appareils mobiles peuvent choisir parmi une gamme croissante de chipsets 5G, les exigences variées associées à la large gamme de capacités de la 5G exigent généralement des solutions plus spécialisées.

Alors que la version 15 du 3GPP a jeté les bases de la 5G NR en mettant l'accent sur le haut débit mobile amélioré (eMBB), la version 16 plus tôt cette année a étendu la 5G à de nouveaux types de services de communication axés sur l'ultra-fiabilité Communication à faible latence (URLLC) et communication massive de type machine (mMTC). URLLC répond au besoin d'un délai de réponse minimal requis pour les applications critiques telles que l'automatisation industrielle, la chirurgie à distance et le transport, tandis que mMTC prend en charge les déploiements à grande échelle et à haute densité d'appareils intelligents dans des applications telles que les villes intelligentes et les usines intelligentes. Les futures versions 3GPP continueront d'étendre la 5G avec des fonctionnalités telles que NR MIMO (entrées multiples et sorties multiples), le partage dynamique du spectre, les améliorations URLLC et autres dans la version 17, ainsi qu'une prise en charge étendue de domaines d'application spécifiques dans la version 18.

En utilisant les capacités 5G telles que la virtualisation des fonctions réseau (NFV) et le découpage du réseau, les fournisseurs de solutions 5G peuvent fournir des réseaux spécialisés capables de fournir la combinaison unique de services requise pour chaque application et client. Pourtant, tenir la promesse d'une flexibilité étendue des réseaux 5G dépend de la disponibilité d'appareils capables d'offrir une combinaison appropriée de performances et de flexibilité ainsi qu'une efficacité énergétique.

"Avec l'évolution des besoins du marché autour de la 5G, les solutions RF intégrées doivent être adaptables pour répondre aux futures normes", a déclaré Liam Madden, vice-président exécutif et directeur général du groupe Wired and Wireless de Xilinx. , dans un rapport. « Zynq RFSoC DFE offre l'équilibre optimal entre cette adaptabilité et l'IP à fonction fixe. »

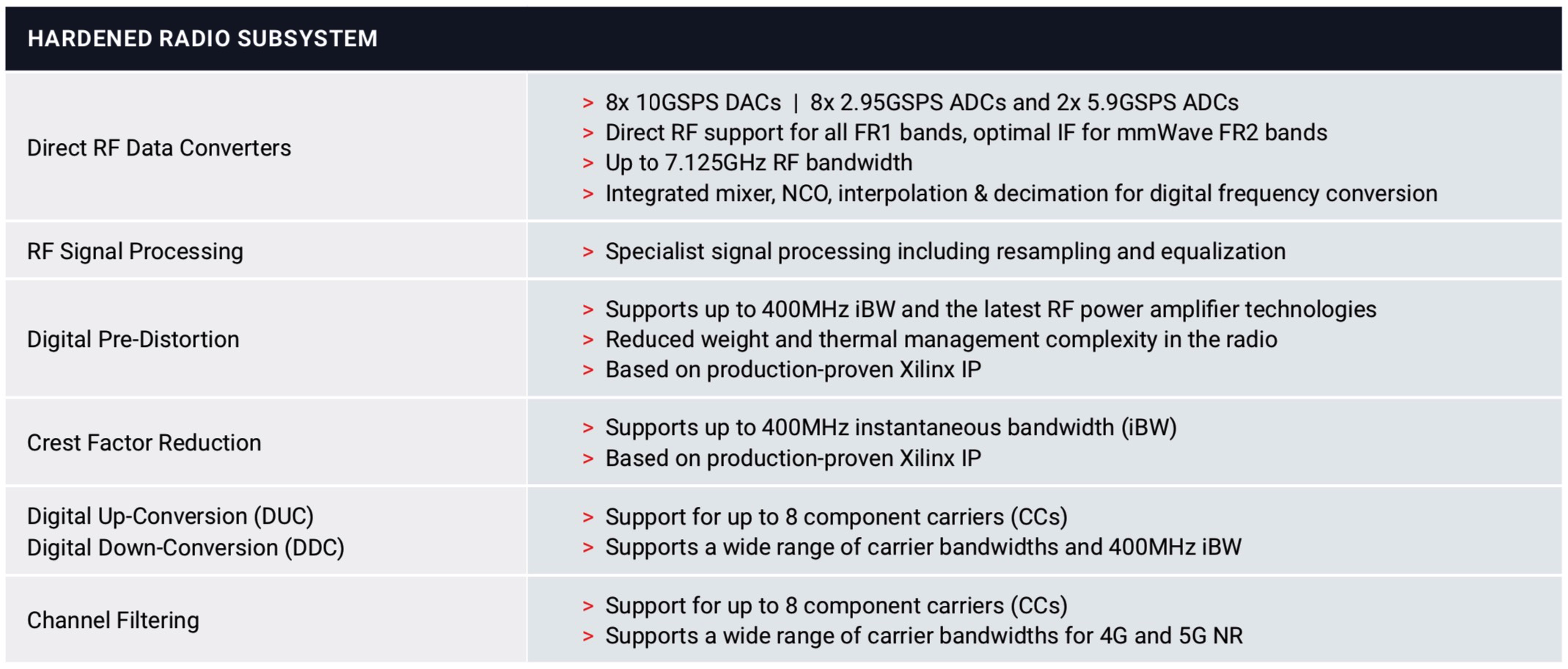

Le Zynq RFSoC DFE intègre une adresse IP matérielle qui implémente les fonctionnalités de base requises dans les chemins de signal 5G RU (Figure 1).

cliquez pour l'image en taille réelle

Figure 1. L'IP dur Zynq RFSoC DFE prend en charge une large gamme de capacités de traitement requises pour la 5G NR ainsi que les radios 4G héritées. (Source :Xilinx)

Étant donné que le cœur IP dur DFE utilise une empreinte plus petite que l'implémentation IP logicielle équivalente dans l'ancien appareil Zynq RFSoC Gen 3, le nouvel appareil peut prendre en charge davantage de cœurs DFE, ce qui augmente les performances de calcul DFE et diminution de la consommation d'énergie par rapport à l'appareil précédent. En conséquence, le Zynq RFSoC DFE peut atteindre un minimum de 2 fois les performances de traitement DFE par watt par rapport à un appareil Zynq RFSoC Gen 3 pleinement utilisé, selon Xilinx.

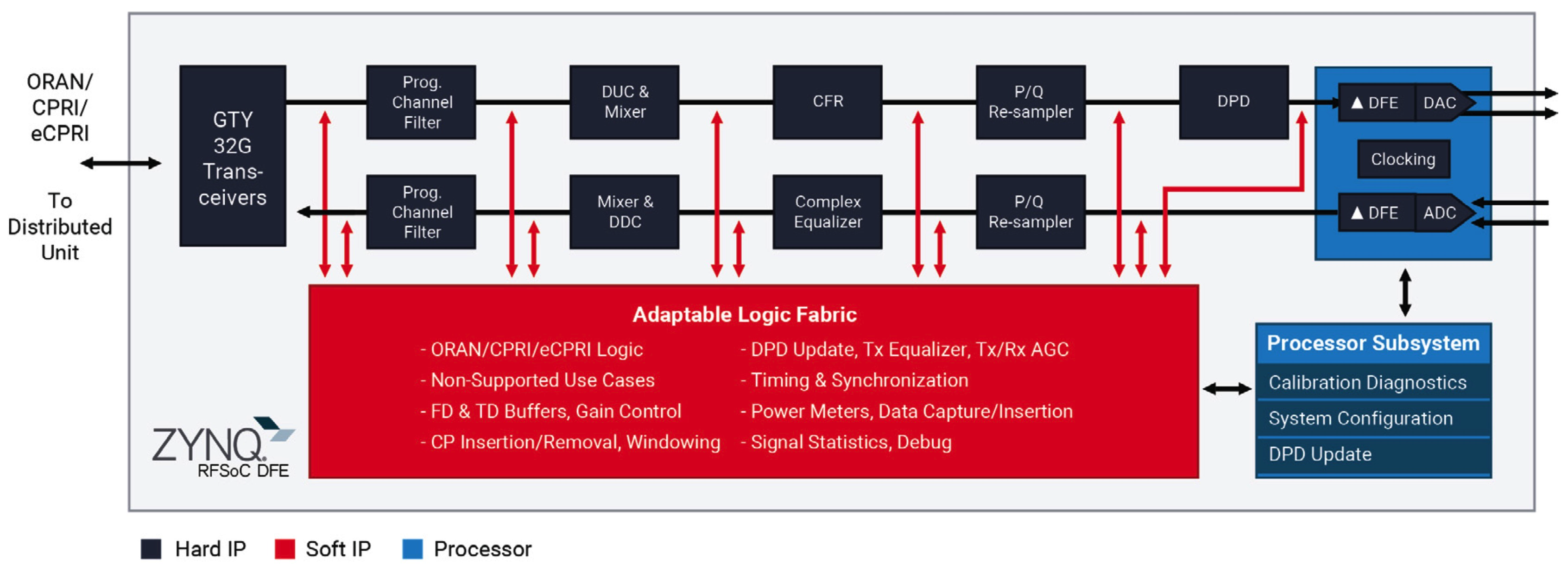

Dans le même temps, les développeurs peuvent modifier le chemin du signal, en contournant les blocs IP durs ou en insérant leur propre fonctionnalité implémentée dans la structure logique (Figure 2).

cliquez pour l'image en taille réelle

Figure 2. L'architecture fonctionnelle Zynq RFSoC DFE combine IP dur, matrice logique et sous-système de processeur. (Source :Xilinx)

La documentation et l'assistance de conception Zynq RFSoC DFE sont disponibles pour les clients à accès anticipé, avec des expéditions prévues au cours du premier semestre 2021. Pour plus d'informations, visitez la page produit Xilinx RFSoC DFE. Xilinx fournit également de plus amples informations sur l'appareil dans le cadre de son événement virtuel 5G les 18 et 19 novembre.

Embarqué

- Xilinx étend le portefeuille Zynq UltraScale+ RFSoC à la prise en charge complète du spectre inférieur à 6 GHz

- Cadence :Tensilica ConnX B20 DSP augmente les performances jusqu'à 30 fois pour les communications 5G

- Renesas :solution de sécurité fonctionnelle RX avec certification logicielle SIL3 pour équipements industriels

- Renesas :MCU RX72M avec prise en charge EtherCAT pour les applications industrielles

- ST :les microcontrôleurs STM32H7 associent performances dual-core et intégration de fonctionnalités riches

- SoC améliore les performances des wearables

- Lanner :solution optimisée pour la virtualisation avec processeur multicœur

- Indicateurs globaux de maintenance, performances de disponibilité

- Blog :Appareils médicaux à haute performance