Conception et recherche de PCB sur une carte de mot de passe à haut débit basée sur PCIE

À l'heure actuelle, le développement rapide de la technologie Internet témoigne de l'application massive du courrier électronique, du paiement en ligne et de la communication personnelle. Dans ce contexte, la sécurité de l'information a été un thème de recherche critique dans le monde entier. La technologie PKI (Public Key Infrastructure) fournit un service de sécurité en utilisant la théorie et la technologie des clés publiques. La technologie PCIE (Peripheral Component Interface Express) a reçu de nombreuses applications dans les dispositifs à grande vitesse en tant que norme de bus d'E/S de troisième génération appliquant la transmission de données en série et la technologie d'interconnexion point à point. Dans le domaine de la conception de systèmes numériques, une fréquence d'horloge relativement élevée entraîne des problèmes d'intégrité du signal, d'intégrité de l'alimentation et de diaphonie, et la conception de circuits imprimés traditionnels ne répond pas aux exigences de stabilité du système.

Cet article propose un schéma de conception de PCB sur une carte de mot de passe à grande vitesse basée sur PCIE en fonction des avantages de la transmission série à grande vitesse PCIE.

Schéma de conception global

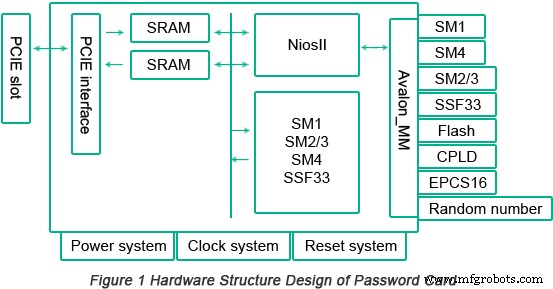

La puce FPGA EP4CGX50CF23C6N appartenant au Cyclone IV GX conçue par Altera est appliquée dans cette conception, intégrant le module PCIE IP hardcore et mettant en œuvre 4 conceptions de carte de mot de passe de transmission de données à haute vitesse. Quatre types de puces, puce 1, puce 2, puce 3 et puce 4, sont capables d'implémenter respectivement des algorithmes de SM1, SM2/SM3, SM4 et SSF33 et d'implémenter des fonctionnalités d'initialisation de carte de mot de passe, d'administration de clé secrète, de sauvegarde et de récupération et d'autorité la gestion. Les cartes de mot de passe sont appliquées dans les PC, connectées à la carte principale des PC via l'emplacement PCIE et contrôlées par les PC. L'IP hardcore dans FPGA est appliqué pour implémenter PCIE, conduisant à la communication entre le cœur PCIE et le cache SRAM et le module de contrôle. En tant que centre de contrôle, NiosII implémente la fonction de logiciel de carte de mot de passe. Pendant ce temps, une puce de mot de passe supplémentaire implémente la communication entre chaque module d'interface et la carte de mot de passe. La conception de la structure matérielle de la carte de mot de passe est illustrée à la figure 1 ci-dessous.

Conception de circuits imprimés à grande vitesse

• Empilage et mise en page

La conception de l'empilement est le problème le plus important à prendre en compte et une conception d'empilement raisonnable peut inhiber le rayonnement EMI (interférence électromagnétique), rendant la tension transitoire sur le plan d'alimentation ou la couche de masse aussi faible que possible et protégeant le champ électromagnétique du signal et de la puissance. Généralement, une carte multicouche et plusieurs puissances sont appliquées dans la conception de circuits numériques à grande vitesse. La conception de l'empilement de PCB est mise en œuvre sur la base d'éléments complets, notamment la fréquence d'horloge du circuit, le coût de fabrication du PCB, la densité des broches, la période de fabrication et la fiabilité. De plus, les couches de panneaux multicouches doivent être maintenues symétriques et le nombre de panneaux doit être un nombre pair, car une conception d'empilement asymétrique entraînera un gauchissement des panneaux. La carte de mot de passe conçue dans cet article est connectée au PC via l'emplacement PCIE et la taille et la forme de la carte de circuit imprimé sont fixées avec une hauteur d'environ 67 mm et une longueur d'environ 174 mm, configurant la broche d'interface PCIE X4 en bas. En raison de la densité élevée des composants et du routage épais, le nombre de couches de PCB est ramassé en 6 couches avec une répartition de la couche de signal, de la couche d'alimentation, de la couche de signal, de la couche d'alimentation, de la couche de masse et de la couche de signal. Cette conception contient 3 couches de signal, 1 couche de masse et 2 couches d'alimentation, fournissant l'environnement requis par l'intégrité du signal.

Après la détermination de l'empilement des PCB, les groupes de composants et la disposition doivent être mis en œuvre. Tout d'abord, la position des composants doit être programmée en fonction de la dimension et du motif du PCB, en tenant compte de la connexion de ligne, du partitionnement fonctionnel, de la garniture et de la beauté entre les composants. Ensuite, les composants doivent être raisonnablement répartis selon différentes qualités de tension de composant pour rendre les fils de tension aussi courts que possible, ce qui est capable de réduire les interférences du bruit de puissance et d'augmenter la stabilité de la puissance. Le placement de la puce doit prêter attention à la relation entre son circuit auxiliaire et sa puce et au placement de l'oscillateur à cristal derrière les broches d'horloge. Les composants à bruit élevé doivent être évités d'être placés autour de l'oscillateur à cristal et doivent être proches de ses composants d'entraînement. De plus, le placement de chaque broche d'alimentation et de signal de puce doit être pris en compte avec leurs positions et leur direction ajustées en fonction des lignes connectées. Étant donné que le rapport entre la longueur et la largeur de la carte de mot de passe est supérieur à 2:1 avec les positions de l'emplacement PCIE, les trous de chargement et la LED d'indication fixe, la disposition des composants pour les composants fixes doit être considérée en premier dans la disposition des composants. De plus, en raison du grand nombre de lignes de connexion entre le composant et le FPGA, la disposition des composants doit être mise en œuvre avec le FPGA comme centre avant les positions des autres composants afin que la pièce supérieure et inférieure du PCB puisse être utilisée efficacement dans l'ordre. pour laisser suffisamment d'espace entre les composants et les composants et les trous de positionnement.

• Conception d'alimentation

Dans la conception de circuits imprimés à grande vitesse, la conception du système d'alimentation est directement liée au succès de l'ensemble du système. Le bruit généré par l'alimentation et la terre doit être réduit au minimum afin d'assurer la fiabilité des produits. L'application du schéma de distribution de puissance dans la méthode des couches fait référence au fait que la puissance est distribuée à travers le métal sur toute la couche, ce qui diminue l'impédance de puissance et le bruit et augmente la fiabilité. Étant donné que plusieurs puissances sont concernées par le PCB, une conception de couche multi-puissance doit être appliquée, capable d'éliminer les interférences de couplage d'impédance publique en tant que boucle de bruit. L'application de la capacité de découplage est capable de résoudre le problème de l'intégrité de l'alimentation puisque le condensateur ne peut être placé que sur la couche inférieure ou la couche supérieure du PCB, sur la base de laquelle les fils reliant les condensateurs de découplage doivent être courts et larges. Selon le matériau de la puce, le courant traversant les lignes électriques peut être calculé et la largeur des conducteurs peut être déterminée. Plus les câbles sont larges, plus ils peuvent transporter de courant. La formule expérimentale est illustrée par :W(largeur de ligne :mm) ≥ L(mm/A) x I(courant :A)

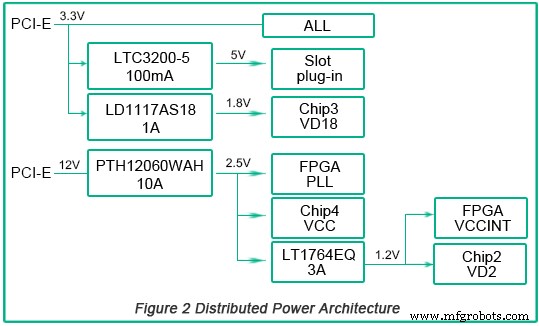

Plusieurs alimentations sur PCB obtiennent un ou deux types d'alimentation de la carte d'alimentation à l'aide de la carte arrière et l'alimentation est ensuite convertie en une autre alimentation requise par les composants. La conversion de puissance est divisée en deux architectures :architecture de puissance centralisée et architecture de puissance distribuée. Le premier fait référence à la puissance fournie par une puissance indépendante puis convertie en toutes sortes de puissances requises, tandis que le second fait référence à la conversion de puissance multigrade. Étant donné que l'architecture d'alimentation centralisée présente les inconvénients d'un coût élevé et d'une grande surface de circuit imprimé, une architecture d'alimentation distribuée est appliquée dans cette conception. La carte cryptographique concerne 6 puissances, dont 12V, 3.3V, 5V, 2.5V, 1.2V et 1.8V. Cette conception commence par la participation de l'alimentation 3,3 V et 12 V dans l'emplacement PCIE, puis l'alimentation 3,3 V est capable de générer une alimentation 5 V et une alimentation 1,8 V via une puce de conversion de tension, alimentant le plug-in et la puce 3. Ensuite, l'alimentation 12 V est convertie en alimentation 2,5 V pour alimenter le FPGA et la puce 4. Enfin, l'alimentation 2,5 V est convertie en alimentation 1,2 V pour alimenter le FPGA et la puce 2. L'architecture d'alimentation distribuée de la carte cryptographique est illustrée à la figure 2 ci-dessous.

• Conception à trou traversant

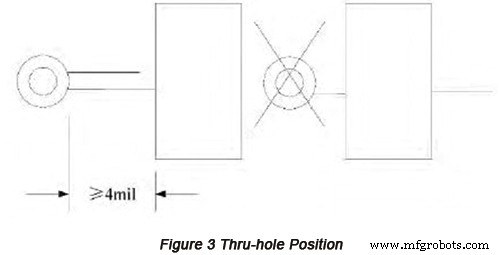

Dans le processus de conception de la disposition des PCB multicouches à haute densité, des trous traversants doivent être appliqués, transmettant le signal d'une couche à une autre couche pour fournir une communication électrique entre les couches. La conception de la position des trous traversants doit être mise en œuvre avec beaucoup de soin. Les trous traversants ne doivent pas être placés sur le tampon et une ligne imprimée peut être appliquée pour la connexion, ce qui entraînerait des problèmes tels que la pierre tombale et une soudure insuffisante. Le masque de soudure doit être enduit sur le tampon de trou traversant avec une distance fixée à 4 mil et les trous traversants ne doivent pas être placés au centre du tampon pour les composants de puce du côté soudure. La position des trous traversants est illustrée à la figure 3 ci-dessous.

De plus, la position du trou traversant ne doit pas être trop proche du doigt d'or dont le côté enfichable doit contenir un chanfrein. Afin de rendre les cartes de circuits imprimés branchées dans l'emplacement PCIE, un chanfrein de (1 ~ 1,5) x 45 ° peut être conçu sur les deux bords latéraux de la carte enfichable.

• Routage de signal à grande vitesse

Dans le processus de routage, la distribution doit être ajustée raisonnablement pour réduire au minimum les lignes de connexion afin de réduire la diaphonie. Dans le processus de routage de signal numérique à grande vitesse, la couche de signal proche du routage de couche multi-puissance doit être éloignée de la surface de référence de puissance afin d'éviter la génération d'un chemin de retour par le courant de signal.

Étant donné que la fréquence du signal d'horloge de circuit à grande vitesse est relativement élevée, la gigue, la dérive et la déformation influencent grandement le système, de sorte que la conception de circuits imprimés à grande vitesse nécessite de petites interférences d'onde de signal. Par conséquent, le problème de la distribution et du routage des horloges doit être considéré en premier lieu. Le routage doit être mis en œuvre sur des signaux d'horloge à grande vitesse et le routage des lignes de signal d'horloge principales doit être aussi court que possible, droit et exempt de trous traversants et de partie d'alimentation afin d'éviter la diaphonie entre l'horloge et l'alimentation. Lorsque plusieurs horloges avec des fréquences différentes sont appliquées sur le même PCB, deux lignes d'horloge avec des fréquences différentes ne doivent pas être maintenues parallèles. Cependant, pour plusieurs composants utilisant des signaux d'horloge avec la même fréquence, le réseau peut être distribué par type d'araignée, type d'arbre et type de branche.

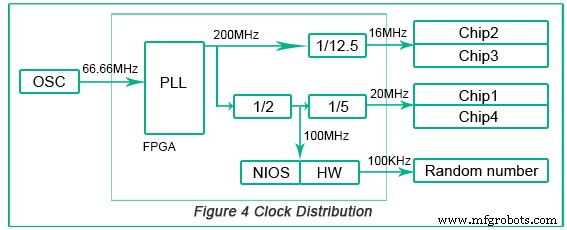

Dans la carte cryptographique à grande vitesse, le FPGA obtient une horloge de 66,66 MHz via l'oscillateur à cristal sur PCB. Après avoir bouclé avec des verrous intrinsèques à l'intérieur du FPGA, une horloge de base de 200 MHz est générée comme interface pour que la puce 2 et la puce 3 fassent fonctionner l'horloge. Ensuite, une horloge de 100 MHz est fournie après le circuit de division de fréquence intrinsèque en tant que softcore NiosII et l'horloge de travail du circuit matériel à l'intérieur du FPGA. La fréquence divisée 16 MHz est l'horloge de travail pour la puce 2 et la puce 3 tandis que la fréquence divisée 20 MHz est l'horloge de travail pour la puce 1 et la puce 4. La distribution d'horloge est affichée dans la figure 4 ci-dessous.

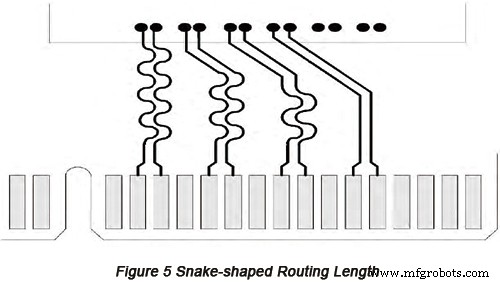

La transmission de signal à grande vitesse entre l'emplacement PCIE et le PC est mise en œuvre par une carte cryptographique à grande vitesse sous la forme d'un routage de paires différentielles pour éviter les problèmes concernant l'intégrité du signal. D'une manière générale, les fils de mise à la terre ne sont pas placés entre les signaux de paires différentielles, sinon l'effet de couplage entre les signaux de paires différentielles sera détruit. Après l'acheminement des signaux de paires différentielles, le cuivre est placé autour des signaux haute vitesse PCB avec un espace libre entièrement rempli de fils de mise à la terre pour augmenter la capacité EMI du circuit. La clé du routage PCB est de maintenir la symétrie des paires différentielles. Si la longueur des paires différentielles n'est pas compatible, la précision de la lecture et de l'écriture des données sera affectée par la diminution du débit de transmission des données. Pour assurer la validité de la lecture des données du système dans la même période, la différence de retard entre les signaux différentiels doit être maintenue dans une catégorie autorisée et la longueur de routage doit être strictement la même. Par conséquent, un routage en forme de serpent peut être appliqué pour résoudre ce problème en ajustant le délai. Dans cette conception, la communication est mise en œuvre par PC via PCIE et carte cryptographique et la transmission et la réception de signaux à grande vitesse sont mises en œuvre par des signaux de paires différentielles avec la longueur du routage PCB contrôlée dans les 25mil. Le diagramme correspondant de la longueur de routage en forme de serpent est illustré à la figure 5.

Ressources utiles

• Comment concevoir des PCB de haute qualité

• Éléments de conception de PCB influençant la fabrication SMT

• Recherche sur la conception de PCB à grande vitesse dans les systèmes d'application embarqués

• Traitement isométrique différentiel et Vérification par simulation de la conception de circuits imprimés à grande vitesse

• Service de fabrication de circuits imprimés complet de PCBCart - Plusieurs options à valeur ajoutée

• Service d'assemblage de circuits imprimés avancé de PCBCart - Commencez à partir de 1 pièce

Technologie industrielle

- Matériaux et conception de PCB pour haute tension

- Capacités de courbure Flex et Rigid-Flex dans la conception de circuits imprimés

- Étapes et processus Apprenez à protéger votre conception de PCB

- Une ligne directrice de la conception de schémas à la conception de circuits imprimés basée sur Altium Designer

- Reculs et solutions dans la conception de circuits imprimés RF

- 3 techniques de routage sur la conception de circuits de signaux à grande vitesse sur PCB

- Conseils de mise en page à grande vitesse

- Conception de la dissipation thermique interne du PCB basée sur le modèle thermique

- Discussion sur l'alimentation et la masse dans la compatibilité électromagnétique des PCB