Simplification des chaînes de signaux d'acquisition de données AC et DC

Les phénomènes d'échantillonnage dans les convertisseurs analogique-numérique (CAN) induisent des problèmes d'aliasing et de rebond capacitif, et pour résoudre ces problèmes, les concepteurs utilisent des filtres et des amplificateurs de pilotage qui présentent leurs propres défis. Cela rend difficile l'obtention de performances DC et AC de précision dans les domaines d'application à bande passante moyenne et les concepteurs finissent par sacrifier les objectifs du système pour le faire.

Cet article décrit les CAN sigma-delta (∑-Δ) en temps continu qui résolvent de manière inhérente et spectaculaire les problèmes d'échantillonnage en simplifiant les chaînes de signaux. Ils suppriment le besoin de filtres et de tampons d'anticrénelage et résolvent les erreurs de décalage de la chaîne de signaux et les problèmes de dérive associés aux composants supplémentaires. Ces avantages réduisent la taille de la solution, facilitent la conception de la solution et améliorent la correspondance de phase et la latence globale du système. Cet article établit également une comparaison avec les convertisseurs à temps discret et met en évidence les avantages du système, ainsi que les contraintes liées à l'utilisation des CAN sigma-delta en temps continu.

Principes de base de l'échantillonnage

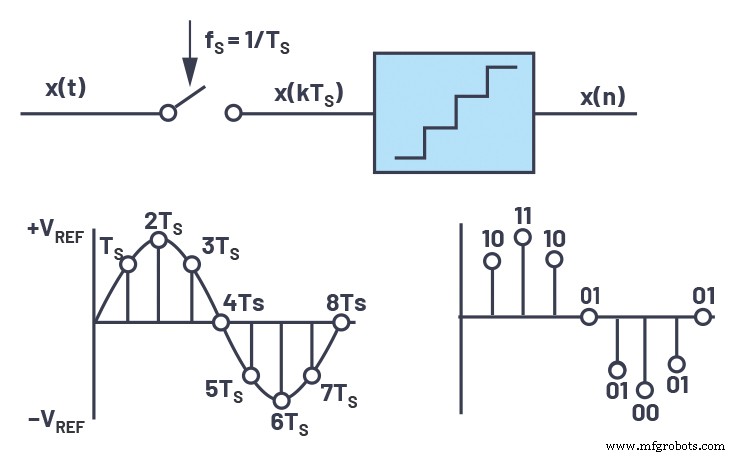

La numérisation des données implique les deux processus fondamentaux d'échantillonnage et de quantification, comme le montre la figure 1. L'échantillonnage est la première étape dans laquelle un signal analogique variable en continu x(t) est converti en un signal à temps discret x(n) en utilisant l'échantillonnage fréquence fS. Le résultat est régulièrement séparé par une période de 1/TS (fS =1/TS).

cliquez pour agrandir l'image

Figure 1. Échantillonnage des données. (Source :Appareils analogiques)

La deuxième étape est la quantification, qui rapproche la valeur de ces échantillons à temps discret à l'une des valeurs finies possibles et est représentée en code numérique, comme le montre la figure 1. Cette quantification à un ensemble fini de valeurs conduit à une erreur de numérisation appelée bruit de quantification.

Le processus d'échantillonnage entraîne également un repliement, dans lequel nous voyons le repliement des signaux d'entrée et ses harmoniques autour de la fréquence d'horloge d'échantillonnage et de maintien. Le critère de Nyquist exige que la fréquence d'échantillonnage soit au moins le double de la fréquence la plus élevée contenue dans le signal. Si la fréquence d'échantillonnage est inférieure au double de la fréquence maximale du signal analogique, un phénomène connu sous le nom de repliement se produira.

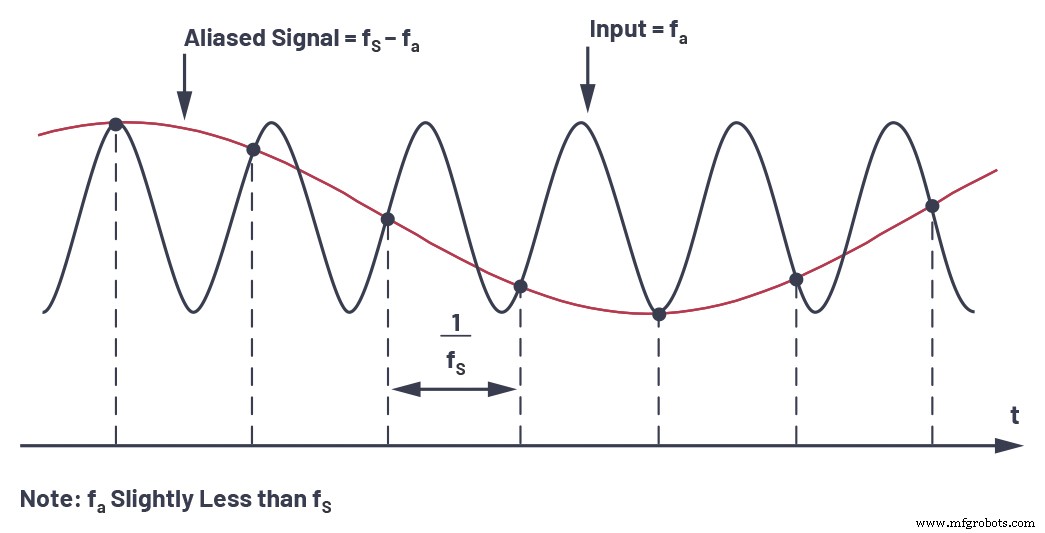

Afin de comprendre les implications de l'aliasing dans le domaine temporel et fréquentiel, considérons d'abord le cas d'une représentation dans le domaine temporel d'une onde sinusoïdale à une seule tonalité échantillonnée, comme illustré à la figure 2. Dans cet exemple, la fréquence d'échantillonnage, fS, n'est pas au moins 2fa, mais seulement légèrement plus que la fréquence d'entrée analogique, fa, ne répondant ainsi pas au critère de Nyquist. Notez que le motif des échantillons réels produit une onde sinusoïdale repliée à une fréquence inférieure égale à fS – fa.

cliquez pour agrandir l'image

Figure 2. Aliasing :représentation dans le domaine temporel. (Source :Appareils analogiques)

cliquez pour agrandir l'image

Figure 3. Aliasing :représentation dans le domaine fréquentiel. (Source :Appareils analogiques)

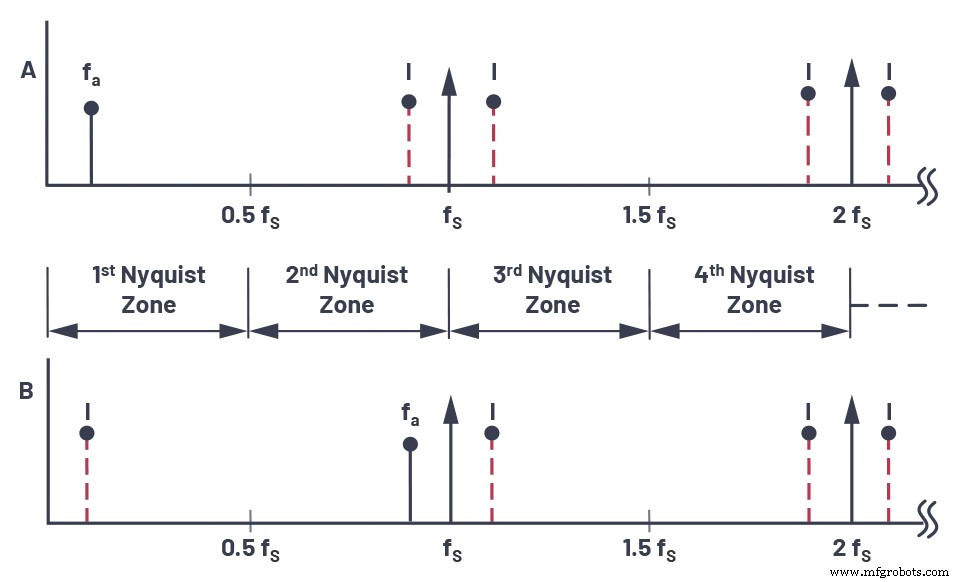

La représentation correspondante dans le domaine fréquentiel de ce scénario est illustrée à la figure 3.

La bande passante de Nyquist est définie comme étant le spectre de fréquences allant du courant continu à fS/2. Le spectre de fréquences est divisé en un nombre infini de zones de Nyquist, chacune ayant une largeur égale à 0,5fS. En pratique, l'échantillonneur idéal est remplacé par un ADC suivi d'un processeur FFT. Le processeur FFT ne fournit qu'une sortie de dc vers fS/2; c'est-à-dire les signaux ou alias qui apparaissent dans la première zone Nyquist.

Considérons le cas d'une onde sinusoïdale monofréquence de fréquence fa échantillonnée à une fréquence fS par un échantillonneur d'impulsions idéal (voir Figure 1). Supposons également que fS> 2fa. La sortie du domaine fréquentiel de l'échantillonneur affiche des alias, ou des images, du signal d'origine autour de chaque multiple de fS; c'est-à-dire à des fréquences égales à | ± KfS ± fa|, K =1, 2, 3, 4, etc.

Considérons maintenant le cas d'un signal qui est en dehors de la première zone de Nyquist sur la figure 3. La fréquence du signal n'est que légèrement inférieure à la fréquence d'échantillonnage, correspondant à la condition indiquée dans la représentation du domaine temporel de la figure 2. Notez que même si le le signal est en dehors de la première zone de Nyquist, son image (ou alias), fS - fa, tombe à l'intérieur. En revenant à la figure 3, il est clair que si un signal indésirable apparaît à l'une des fréquences d'image de fa, il se produira également à fa, produisant ainsi une composante de fréquence parasite dans la première zone de Nyquist.

Combattre les défis pour des performances de précision

Pour les applications hautes performances, les concepteurs de systèmes doivent lutter contre le bruit de quantification, l'aliasing et les problèmes d'échantillonnage d'entrée de condensateur commuté résultant du processus d'échantillonnage. Les deux types d'ADC de précision, c'est-à-dire les registres d'approximations successives (SAR) et les ADC sigma-delta, disponibles dans l'industrie, sont conçus à l'aide de techniques d'échantillonnage à condensateur commuté.

Bruit de quantification

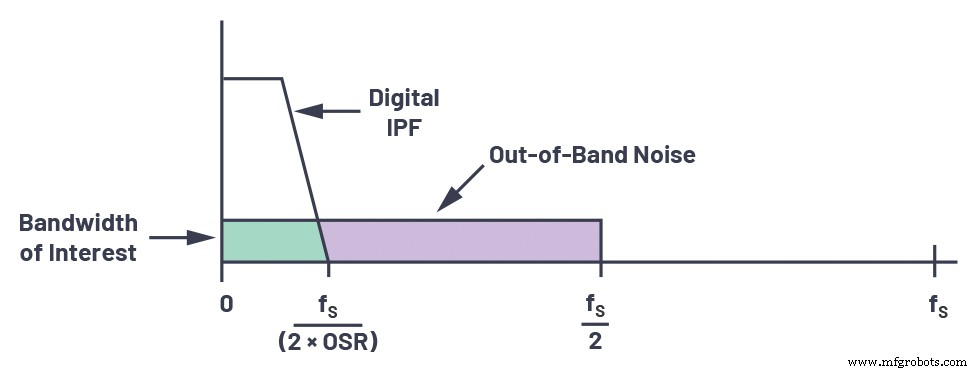

Dans un ADC Nyquist idéal, la taille LSB de l'ADC déterminera le bruit de quantification qui sera ajouté à l'entrée, tout en effectuant une conversion analogique-numérique. Ce bruit de quantification est étalé sur la bande passante de fS/2. Pour lutter contre le bruit de quantification, la première technique est le suréchantillonnage, qui échantillonne le signal d'entrée à une fréquence beaucoup plus élevée que la fréquence de Nyquist pour augmenter le rapport signal sur bruit (SNR) et la résolution (ENOB). En suréchantillonnage, la fréquence d'échantillonnage est choisie pour être N fois la fréquence de Nyquist (2 × fIN), et par conséquent le même bruit de quantification doit maintenant s'étendre sur N fois la fréquence de Nyquist. Cela assouplit également les exigences relatives au filtre anticrénelage. Le rapport de suréchantillonnage (OSR) est défini comme fS/2fIN, où fIN est le signal BW d'intérêt. En règle générale, le suréchantillonnage de l'ADC par un facteur de quatre fournit un bit supplémentaire de résolution, ou une augmentation de 6 dB de la plage dynamique. L'augmentation du taux de suréchantillonnage entraîne une réduction globale du bruit et l'amélioration de la plage dynamique (DR) due au suréchantillonnage est ΔDR =10log10 OSR en dB.

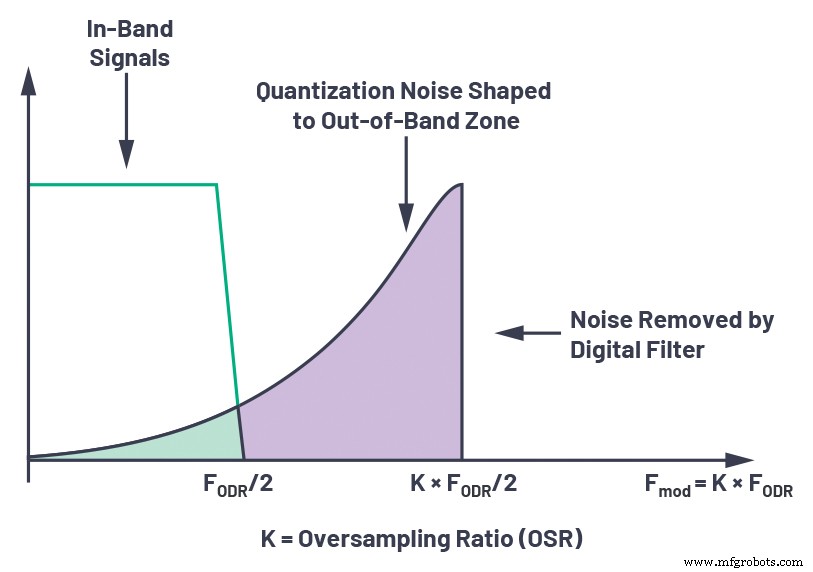

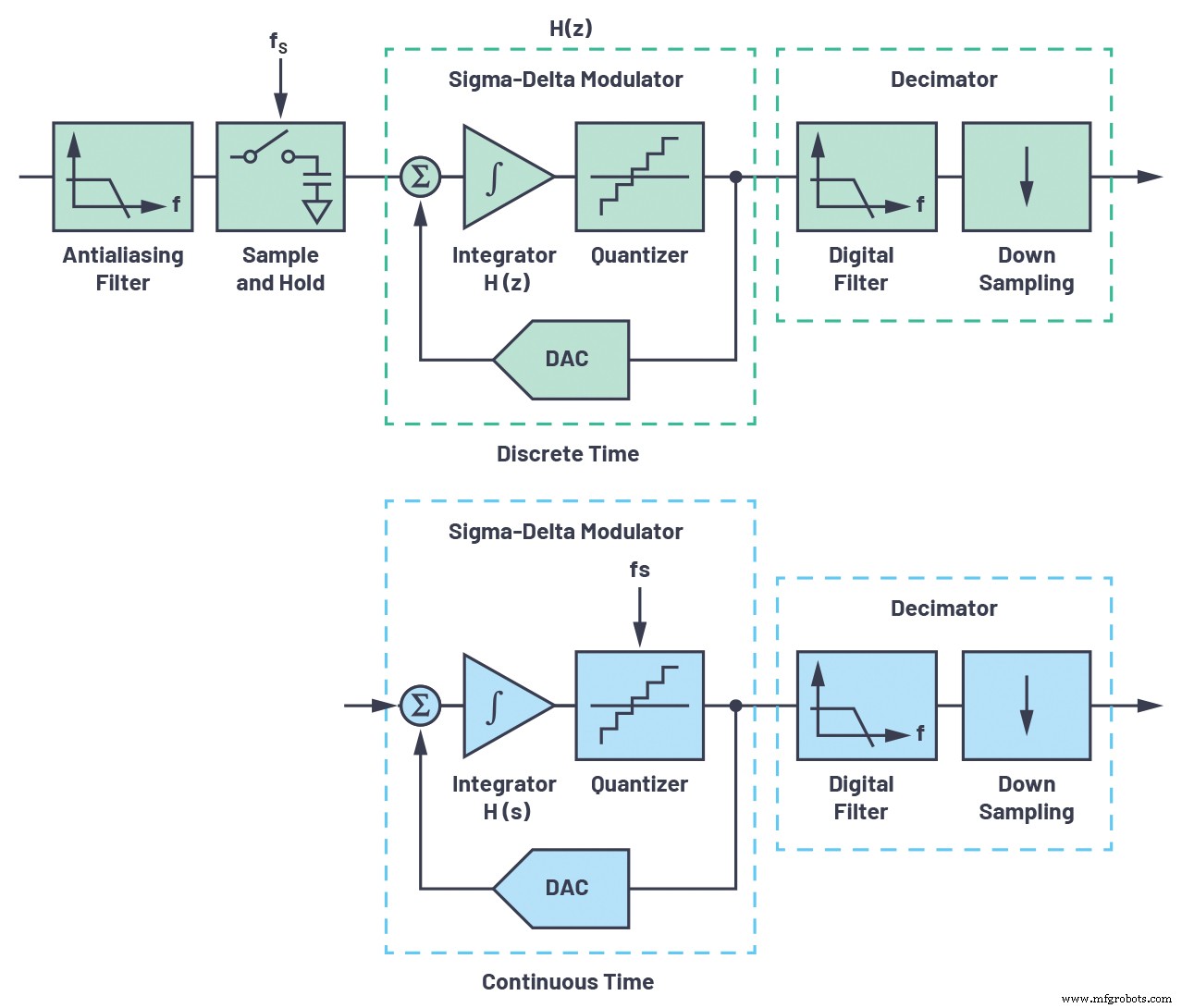

Le suréchantillonnage est intrinsèquement utilisé et mis en œuvre avec un filtre numérique intégré et une fonctionnalité de décimation. Le modulateur de suréchantillonnage de base du CAN sigma-delta façonne le bruit de quantification de telle sorte que la majeure partie de celui-ci se produit en dehors de la bande passante d'intérêt, ce qui entraîne une augmentation de la plage dynamique globale aux basses fréquences, comme le montre la figure 4. Le filtre passe-bas numérique (LPF ) supprime ensuite le bruit de quantification en dehors de la bande passante d'intérêt, et le décimateur réduit le débit de données de sortie au débit de Nyquist.

cliquez pour agrandir l'image

Figure 4. Un exemple de suréchantillonnage. (Source :Appareils analogiques)

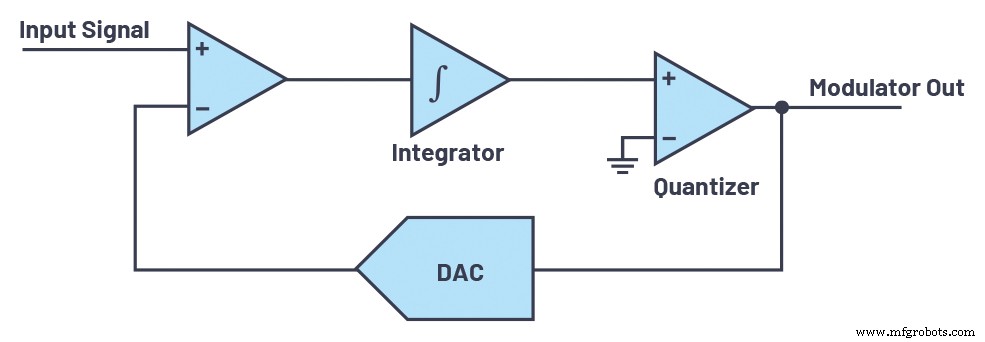

La mise en forme du bruit est l'autre technique pour réduire le bruit de quantification. Dans les CAN sigma-delta, un quantificateur basse résolution (un bit à cinq bits) est utilisé à l'intérieur d'une boucle après le filtre de boucle. Un DAC est utilisé comme retour pour soustraire le signal quantifié de l'entrée, comme le montre la figure 5.

cliquez pour agrandir l'image

Figure 5. Mise en forme du bruit. (Source :Appareils analogiques)

L'intégrateur continuera à additionner l'erreur de quantification résultant de la mise en forme du bruit de quantification à des fréquences plus élevées, qui peuvent ensuite être filtrées à l'aide d'un filtre numérique. La figure 6 illustre la densité spectrale de puissance (PSD) de la sortie x[n] d'un CAN sigma-delta typique. La pente de mise en forme du bruit dépend de l'ordre du filtre de boucle H(z) (voir Figure 11) et est de (20 × n) dB/décade, où n est l'ordre du filtre de boucle. L'ADC sigma-delta atteint une haute résolution dans la bande grâce à une combinaison de mise en forme du bruit et de suréchantillonnage. La bande passante intrabande est égale à fODR/2 (ODR signifie débit de données de sortie). Une résolution plus élevée peut être obtenue en augmentant l'ordre du filtre de boucle ou en augmentant le taux de suréchantillonnage.

cliquez pour agrandir l'image

Figure 6. Graphique de suréchantillonnage et de mise en forme du bruit. (Source :Appareils analogiques)

Création d'alias

Pour lutter contre l'aliasing dans les applications hautes performances, des filtres d'antialiasing d'ordre supérieur sont utilisés pour éviter toute quantité de repli. Un filtre anticrénelage est un filtre passe-bas qui limite la bande du signal d'entrée et garantit qu'il n'y a pas de composante de fréquence dans le signal au-delà de la bande passante d'intérêt qui peut se replier. Les performances du filtre dépendront de la proximité du signal hors bande par rapport à fS/2 et de la quantité d'atténuation requise.

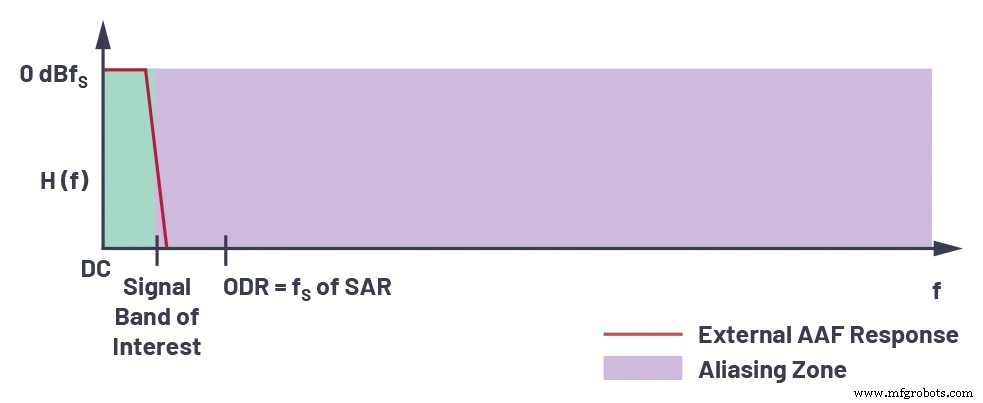

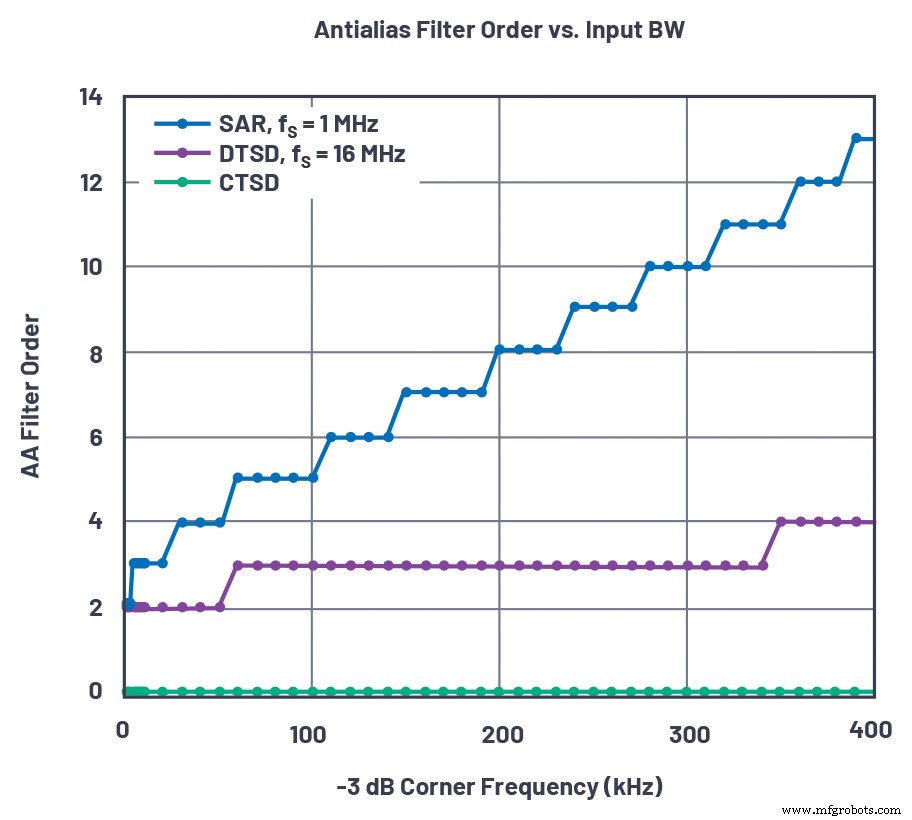

Pour les CAN SAR, l'écart entre le signal d'entrée BW et la fréquence d'échantillonnage n'est pas énorme, nous avons donc besoin d'un filtre d'ordre supérieur qui nécessite une conception de filtre complexe d'ordre supérieur avec plus de puissance et plus de distorsion. Par exemple, si un SAR à vitesse d'échantillonnage de 200 kSPS a un BW d'entrée de 100 kHz, le filtre anticrénelage devra rejeter un signal d'entrée de>100 kHz pour s'assurer qu'il n'y a pas de crénelage. Cela nécessite un filtre d'ordre très élevé. La figure 7 montre la demande en courbe abrupte.

cliquez pour agrandir l'image

Figure 7. Exigence d'alias. (Source :Appareils analogiques)

Si une vitesse d'échantillonnage de 400 kSPS est choisie pour détendre l'ordre du filtre, la réjection est nécessaire pour une fréquence d'entrée> 300 kHz. L'augmentation de la vitesse d'échantillonnage augmentera la puissance, et pour une vitesse double, la puissance serait également doublée. Un suréchantillonnage supplémentaire au détriment de la puissance détendra davantage l'exigence de filtre anticrénelage, car la fréquence d'échantillonnage est beaucoup plus élevée que la BW d'entrée.

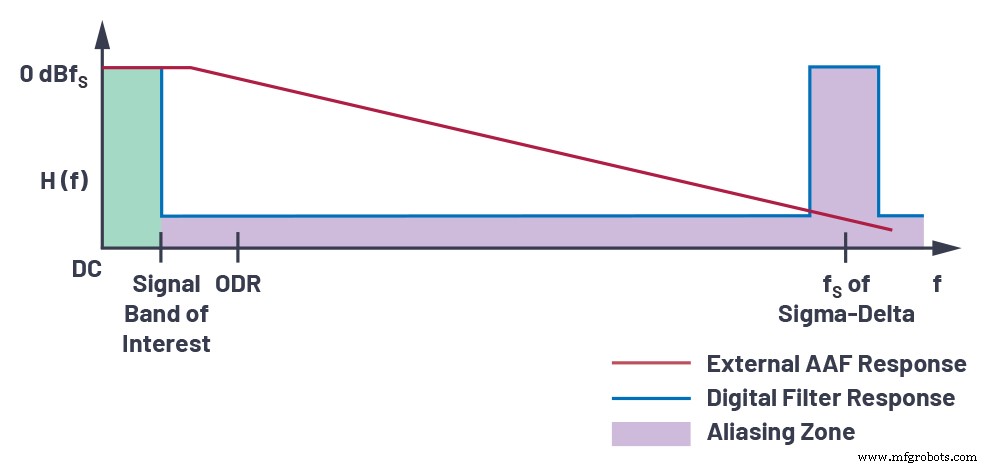

Dans les CAN sigma-delta, l'entrée est suréchantillonnée à un OSR beaucoup plus élevé, de sorte que l'exigence de filtre anticrénelage est assouplie car la fréquence d'échantillonnage est beaucoup plus élevée que le BW d'entrée, comme le montre la figure 8.

cliquez pour agrandir l'image

Figure 8. Filtre d'anticrénelage requis dans sigma-delta. (Source :Appareils analogiques)

La figure 9 donne une idée de la complexité de l'AAF pour les architectures SAR et sigma-delta à temps discret (DTSD). Si nous prenons une bande passante d'entrée de -3 dB de 100 kHz pour obtenir une atténuation de 102 dB à la fréquence d'échantillonnage fS, un filtre anticrénelage de second ordre sera nécessaire pour un CAN DTSD tout en obtenant la même atténuation à fS nécessitera un filtre de cinquième ordre utilisant un ADC SAR.

Pour un CAN sigma-delta en temps continu (CTSD), l'atténuation est inhérente, nous n'avons donc pas besoin de filtre d'anticrénelage.

cliquez pour agrandir l'image

Figure 9. Filtre AAF requis pour diverses architectures. (Source :Appareils analogiques)

Ces filtres peuvent être un problème pour les concepteurs de systèmes, et ils doivent les optimiser pour le statisme qu'ils fournissent dans la bande d'intérêt et fournir autant de rejet que possible. Ils ajoutent également de nombreuses autres erreurs telles que le décalage, le gain, l'erreur de phase et le bruit au système, réduisant ainsi ses performances.

De plus, les CAN hautes performances sont de nature différentielle, nous avons donc besoin de deux fois plus de composants passifs. Pour obtenir une meilleure correspondance de phase dans les applications multicanaux, tous les composants de la chaîne du signal doivent bien correspondre. En conséquence, des composants avec des tolérances plus strictes sont nécessaires.

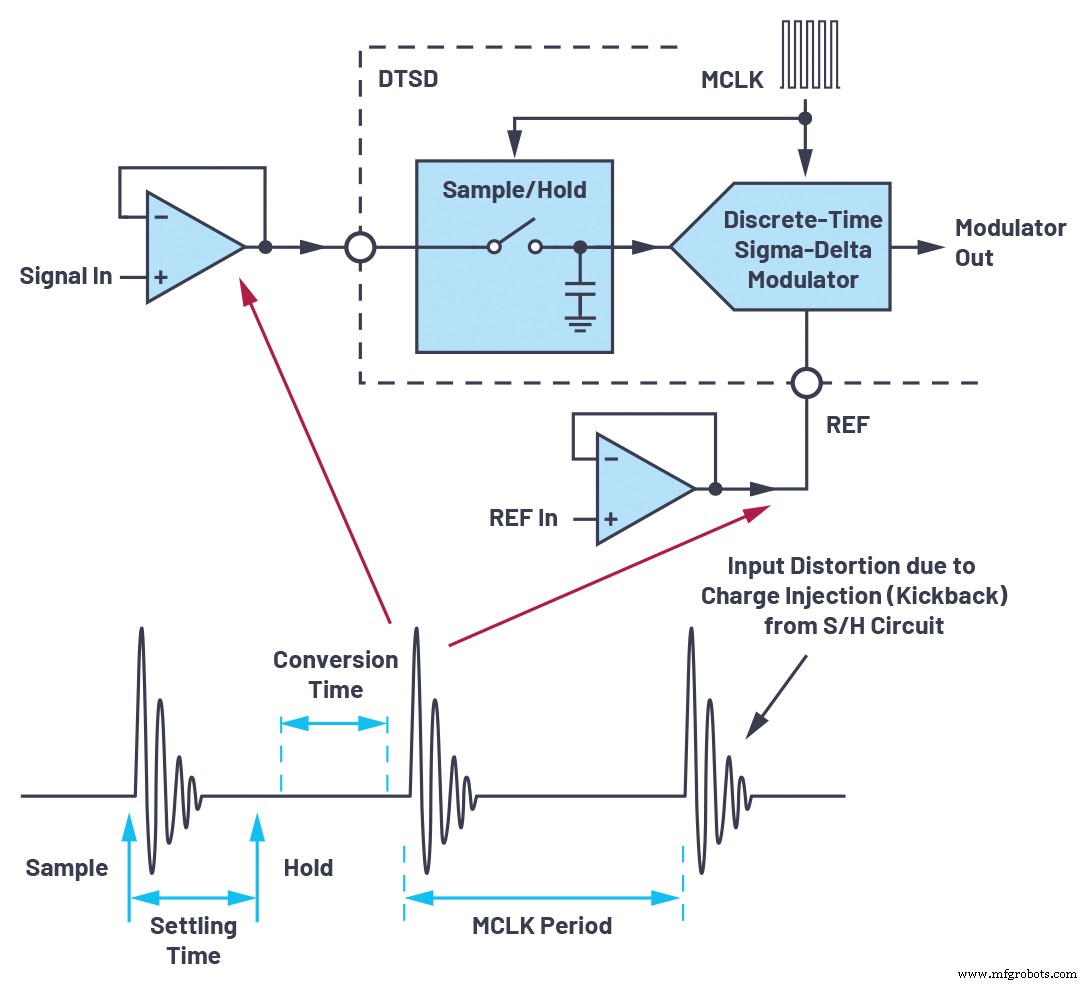

Entrée de condensateur commuté

L'échantillonnage d'entrée de condensateur commuté repose sur le temps d'établissement de l'entrée échantillonnée sur un condensateur, créant une demande de courant transitoire de charge/décharge lorsque le commutateur d'échantillonnage est activé/désactivé. C'est ce qu'on appelle le rebond sur l'entrée et nécessite un amplificateur de pilotage d'entrée qui peut supporter ces courants transitoires. De plus, l'entrée doit être réglée à la fin du temps d'échantillonnage et la précision de l'entrée échantillonnée détermine les performances de l'ADC, ce qui implique que l'amplificateur de pilotage doit se régler rapidement après l'événement de rebond. Cela conduit au besoin d'un pilote à bande passante élevée qui peut prendre en charge une stabilisation rapide et absorber le rebond du fonctionnement du condensateur commuté. Dans les entrées de condensateur commuté, chaque fois que l'échantillonnage est activé, le pilote doit immédiatement fournir la charge du condensateur de maintien. Cette augmentation soudaine de courant ne peut être fournie à temps que si le conducteur dispose de capacités de bande passante suffisantes. En raison des parasites du commutateur, il y aura un rebond sur le conducteur au moment de l'échantillonnage. Si le rebond ne s'installe pas avant le prochain échantillonnage, il en résultera une erreur d'échantillonnage, corrompant ainsi l'entrée ADC.

cliquez pour agrandir l'image

Figure 10. Rebond d'échantillonnage. (Source :Appareils analogiques)

La figure 10 montre le rebond sur le DTSD ADC. Si, par exemple, la fréquence d'échantillonnage est de 24 MHz, le signal de données doit se stabiliser en 41 ns. Étant donné que la référence est également une entrée de condensateur commuté, un tampon à bande passante élevée est également nécessaire sur la broche d'entrée de référence. Ces tampons de signal d'entrée et de référence ajoutent au bruit et diminuent les performances globales de la chaîne de signaux. De plus, les composants de distorsion du pilote de signal d'entrée (autour de la fréquence S&H) ajoutent aux exigences d'anticrénelage. De plus, avec des entrées de condensateur commuté, les changements de vitesse d'échantillonnage entraîneront une variation du courant d'entrée. Cela pourrait entraîner un réajustement du système pour réduire l'erreur de gain générée dans le pilote ou l'étage précédent lors de la conduite de l'ADC.

ADC Sigma-Delta en temps continu

Un CAN CTSD est une architecture alternative de CAN sigma-delta qui tire parti de principes tels que le suréchantillonnage et la mise en forme du bruit, mais qui dispose d'un autre moyen de mettre en œuvre l'opération d'échantillonnage qui offre des avantages significatifs pour le système.

La figure 11 montre une comparaison d'une architecture DTSD et d'une architecture CTSD. Comme nous le voyons dans l'architecture DTSD, l'entrée est échantillonnée avant la boucle. Le filtre de boucle H(z) est discret dans le temps et implémenté à l'aide d'intégrateurs à condensateur commuté. Le DAC de retour est également basé sur un condensateur commuté. Comme il y a un échantillonnage à l'entrée, ce qui entraînera un problème d'aliasing de fS , un filtre anticrénelage supplémentaire est requis sur l'entrée avant qu'elle ne soit échantillonnée.

cliquez pour agrandir l'image

Figure 11. Schémas de blocs modulaires en temps discret et en temps continu. (Source :Appareils analogiques)

CTSD n'a pas d'échantillonneur en entrée. Il est plutôt échantillonné au niveau du quantificateur à l'intérieur de la boucle. Le filtre de boucle est désormais à temps continu à l'aide d'intégrateurs à temps continu, tout comme le DAC de retour. Semblable à la quantification qui est mise en forme, le repliement dû à l'échantillonnage est également mis en forme. Cela se traduit par un CAN presque sans échantillonnage, ce qui en fait une classe à part.

La fréquence d'échantillonnage du CTSD est fixe, contrairement au DTSD où la fréquence d'échantillonnage du modulateur peut être facilement mise à l'échelle. De plus, les CAN CTSD sont connus pour être moins tolérants à la gigue que les équivalents à condensateur commuté. Les oscillateurs à quartz ou CMOS du commerce fournissent des horloges à faible gigue aux CAN localement, ce qui permet d'éviter de transmettre une horloge à faible gigue sur isolation et réduit la CEM.

Les deux principaux avantages du CTSD sont le rejet d'alias inhérent et les entrées résistives pour les signaux et la référence.

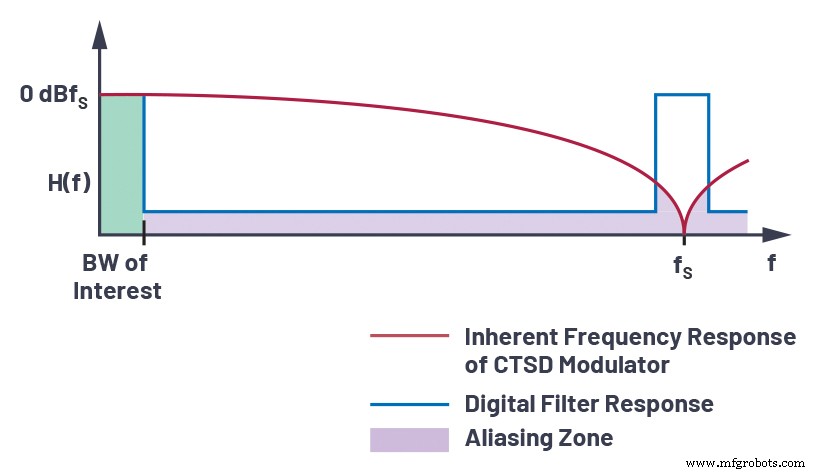

Anticrénelage inhérent

Le déplacement du quantificateur à l'intérieur de la boucle entraîne un rejet d'alias inhérent. Comme le montre la figure 12, le signal d'entrée traverse le filtre de boucle avant d'être échantillonné et l'erreur de repliement (alias), qui est introduite au niveau du quantificateur, voit également ce filtre. Le signal et l'erreur d'alias verront la même fonction de transfert de bruit que la boucle sigma-delta, et les deux auront une mise en forme de bruit similaire à celle du bruit de quantification dans les architectures sigma-delta. Ainsi, la réponse en fréquence de la boucle CTSD rejette naturellement les signaux d'entrée autour de multiples entiers de la fréquence d'échantillonnage, agissant comme un filtre anticrénelage.

cliquez pour agrandir l'image

Figure 12. Réponse en fréquence d'un modulateur CTSD. (Source :Appareils analogiques)

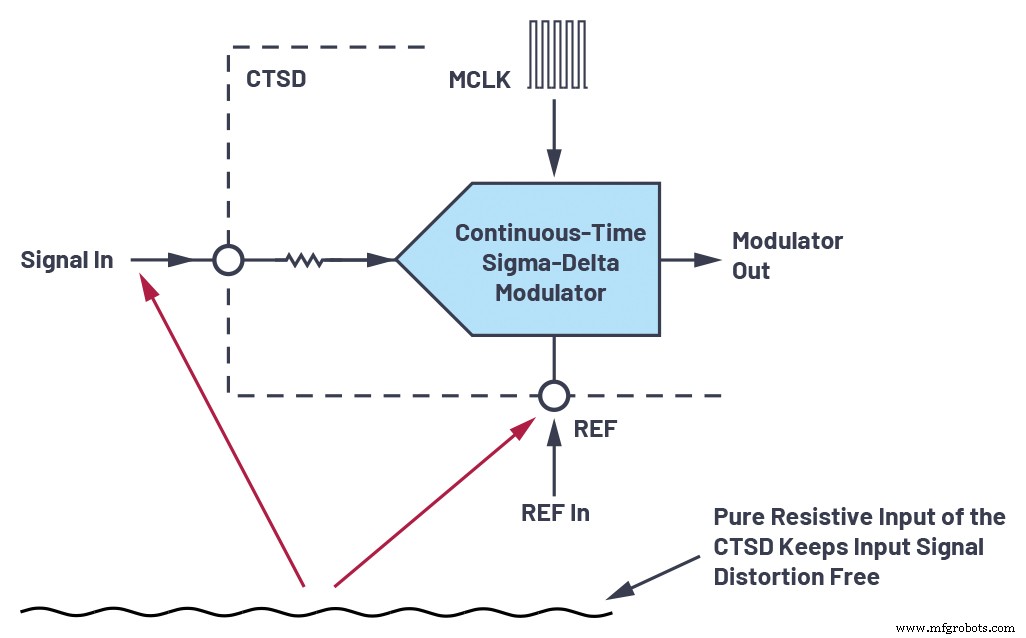

Entrée résistive

Le fait d'avoir des entrées résistives sur les entrées de signal et de référence le rend plus facile à piloter que les configurations d'échantillonnage et de maintien. Avec des entrées résistives constantes, il n'y a pas de rebond et le pilote peut être complètement retiré. L'entrée est sans distorsion, comme le montre la figure 13. Et puisque la résistance d'entrée est constante, le réajustement du système pour les erreurs de gain est également éliminé.

cliquez pour agrandir l'image

Figure 13. Stabilisation d'entrée pour CTSD. (Source :Appareils analogiques)

Les entrées analogiques peuvent être bipolaires même si l'ADC a une alimentation unipolaire. Cela peut éliminer le besoin de décalage de niveau d'une extrémité avant bipolaire à l'ADC. Les performances en courant continu de l'ADC peuvent ne pas être les mêmes car la résistance d'entrée a maintenant un courant d'entrée dépendant du mode commun ainsi que le courant d'entrée.

La charge de référence est également résistive, ce qui réduit le rebond de commutation, donc un tampon de référence séparé n'est pas nécessaire. La résistance d'un filtre passe-bas peut être intégrée à la puce afin qu'elle puisse suivre la charge résistive sur la puce (car elles pourraient être du même matériau), pour une dérive de température d'erreur de gain réduite.

L'architecture CTSD n'est pas nouvelle, mais les mégatendances des marchés de l'industrie et de l'instrumentation exigent des performances de précision en courant continu et en courant alternatif à des bandes passantes plus élevées. De plus, les clients préfèrent une conception de plate-forme unique qui répondrait à la plupart de leurs solutions afin de réduire leur temps de mise sur le marché.

L'architecture CTSD a été le choix dans un large éventail d'applications allant de l'audio haute performance à l'extrémité avant RF du combiné cellulaire en raison d'un certain nombre d'avantages par rapport aux autres types d'ADC. Les avantages comprennent une plus grande facilité d'intégration et une faible consommation d'énergie, mais aussi, et peut-être plus important encore, parce que l'utilisation d'un CTSD résout un certain nombre de problèmes importants au niveau du système. En raison d'un certain nombre de lacunes technologiques, l'utilisation du CTSD était auparavant limitée à une fréquence audio/bande passante relative et à une plage dynamique inférieure. Par conséquent, les convertisseurs de débit Nyquist hautes performances tels que les CAN à approximations successives et les convertisseurs DTSD suréchantillonnés ont été la solution principale pour les applications de précision, hautes performances/bande passante moyenne.

Cependant, les récentes avancées technologiques ont permis de surmonter de nombreuses limitations. Par exemple, l'AD7134 d'Analog Devices prend en charge un CAN de haute précision à bande passante CC à 400 kHz basé sur CTSD qui atteint des spécifications de performances considérablement plus élevées, tout en offrant une précision CC et, à son tour, permettant la solution à un certain nombre de problèmes importants au niveau du système en haute applications d'instrumentation de performance. L'AD7134 intègre également un convertisseur de fréquence d'échantillonnage asynchrone (ASRC) fournissant des données à des débits variables dérivés de la vitesse d'échantillonnage fixe du CTSD. Le débit de données de sortie peut être indépendant de la fréquence d'échantillonnage du modulateur et peut permettre une utilisation réussie des CAN CTSD pour différents débits granulaires. La possibilité de modifier le débit de données de sortie à un niveau granulaire permet également aux utilisateurs d'utiliser un échantillonnage cohérent.

Le rejet d'alias inhérent supprime le besoin d'un filtre d'anticrénelage, ce qui se traduit par moins de composants et une taille de solution plus petite. Plus important encore, les problèmes de performances liés à un filtre anticrénelage tel que le statisme, les erreurs telles que le décalage, le gain et l'erreur de phase, et le bruit dans le système ne sont plus présents. Un filtre anticrénelage ajoute également de manière significative à la latence globale dans la chaîne de signal en fonction du rejet nécessaire. La suppression du filtre supprime complètement ce retard, permettant une conversion de précision dans les applications de boucle de commande numérique bruyantes.

Sans filtre anticrénelage au niveau du système, l'adaptation de phase dans les systèmes multicanaux peut être considérablement améliorée. Ceci est particulièrement utile dans les applications exigeant une faible inadéquation entre les canaux, telles que la surveillance des vibrations, les mesures de puissance, les modules d'acquisition de données et le sonar. En raison de leur action de filtrage inhérente, les CAN CTSD sont également immunisés contre tout type d'interférence au niveau du système, ainsi qu'à l'intérieur du circuit intégré lui-même. Dans les ADC DTSD et les ADC SAR, il faut veiller à ce qu'il y ait moins d'interférences lorsque l'ADC échantillonne. En outre, il y aurait une immunité contre les interférences sur les lignes d'alimentation en raison de l'action de filtrage inhérente. Avec des entrées analogiques à résistance constante et des entrées de référence, l'exigence de pilote peut également être complètement supprimée. Encore une fois, cela résout les problèmes de performances tels que les erreurs telles que le décalage, le gain, l'erreur de phase et le bruit du système ne sont plus là.

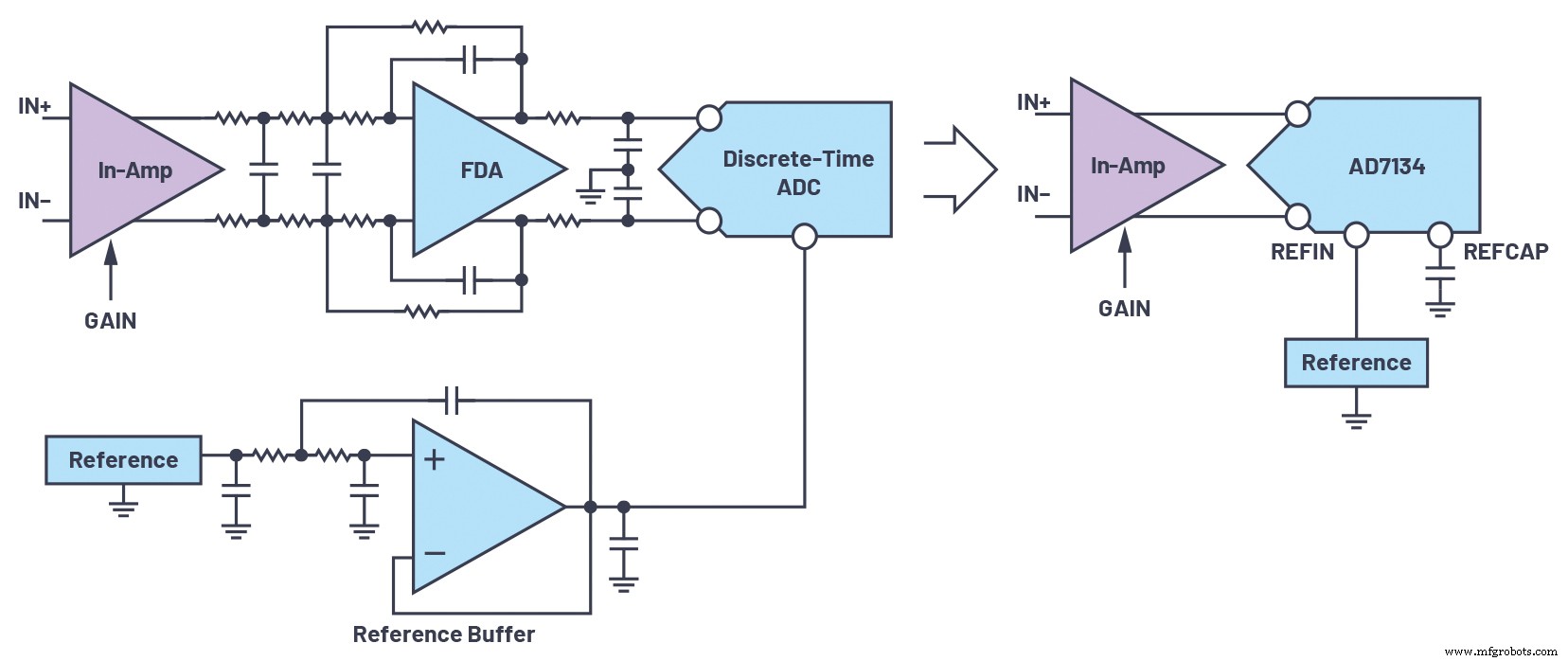

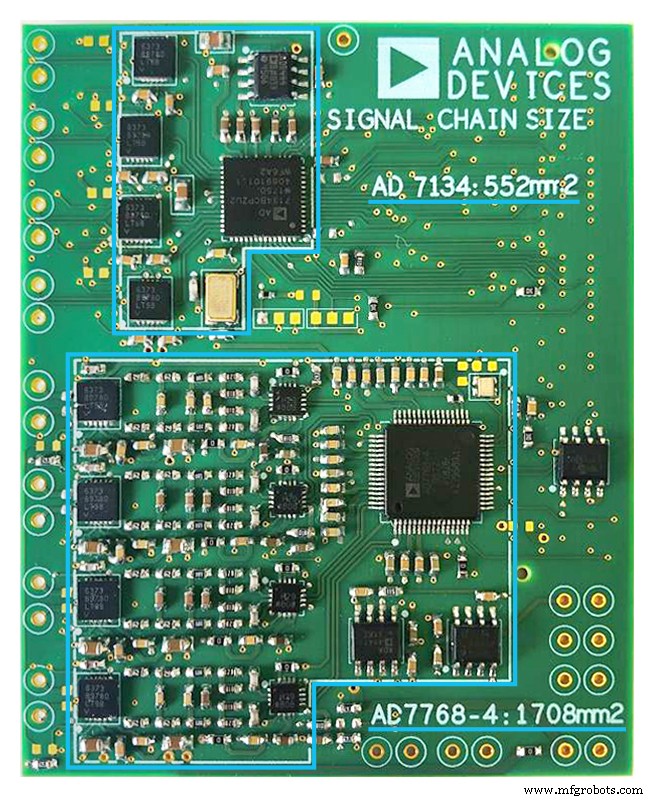

La lutte pour atteindre les performances de précision est très minime car le nombre d'éléments conçus est considérablement réduit. Cela se traduit par un temps de conception plus rapide, une mise sur le marché plus rapide pour les clients, une gestion plus simple des nomenclatures et une fiabilité. La suppression d'un filtre anticrénelage, d'un pilote et d'un tampon de référence réduira considérablement la surface de la carte système. Un amplificateur d'instrumentation peut être utilisé pour piloter directement l'ADC. Par exemple, avec l'AD7134, comme il s'agit d'un CAN à entrée différentielle uniquement, un ampli différentiel tel que le LTC6373 peut être utilisé comme pilote. La comparaison de la figure 14 montre la chaîne de signaux pour une chaîne de signaux à temps discret et une chaîne de signaux à temps continu. Notre expérience montre 70 % d'économies de surface par rapport à une chaîne de signaux à temps discret équivalente, ce qui en fait un excellent choix pour les applications multicanaux à haute densité.

En conclusion, cette approche offre une réduction significative de la taille du système, simplifie la conception de la chaîne de signaux, rend le système plus robuste et réduit le temps global de mise sur le marché grâce à une conception facile sans échanger les paramètres de performance exigés par les applications d'instrumentation de précision.

cliquez pour agrandir l'image

Figure 14. Une comparaison de chaînes de signaux en temps discret (à gauche) et en temps continu (à droite). (Source :Appareils analogiques)

cliquez pour agrandir l'image

Figure 15. Comparaison de la taille des chaînes de signaux en temps discret et en temps continu. (Source :Appareils analogiques)

Références

Kester, Walt. « MT-002 : que signifie le critère de Nyquist pour la conception de votre système de données échantillonnées ». Analog Devices, Inc., 2009.

Pavan, Shanti. « Rejet d'alias des modulateurs Δ∑ à temps continu avec DAC à rétroaction de condensateur commuté. » Transactions IEEE sur les circuits et les systèmes I :articles réguliers , Vol. 58, n° 2, février 2011.

Schreier, Richard et Gabor C. Temes. Comprendre les convertisseurs de données Delta-Sigma. John Wiley et fils, 2005.

Remerciements

L'auteur tient à remercier Abhilasha Kawle, Avinash Gutta et Roberto Maurino pour leur soutien à cet article.

Embarqué

- Termes et concepts de la mémoire numérique

- Variables C# et types de données (primitifs)

- Conversion de type Python et conversion de type

- Apacer :lancement des cartes CV110-SD et CV110-MSD dans le monde

- Swissbit :solutions de sécurité matérielles pour protéger les données et les appareils

- Hyperconvergence et stockage secondaire :2e partie

- Créer une IA responsable et digne de confiance

- Blockchain et chaînes d'approvisionnement :libérer le potentiel

- Le sens des Data Fabrics et leurs avantages pour les chaînes d'approvisionnement