Utilisation de l'analyseur logique intégré (ILA) et de l'entrée/sortie virtuelle (VIO)

Ce didacticiel couvre l'utilisation de l'analyseur logique intégré (ILA) et Entrée/Sortie virtuelle (VIO) cœurs pour déboguer et surveiller votre conception VHDL dans l'IDE Xilinx Vivado.

Dans de nombreux cas, les concepteurs doivent effectuer une vérification sur puce. Autrement dit, accéder au comportement d'un signal interne dans leur conception FPGA à des fins de vérification.

Une option consiste à amener ces signaux sur les broches du FPGA et à les connecter aux LED pour voir leur comportement visuellement. Cette option est simple, rapide et fonctionne bien pour les cas simples, mais elle n'est ni flexible, ni évolutive, ni réaliste.

Une autre option est d'avoir un analyseur logique externe avec des fonctionnalités avancées qui peuvent afficher et décrire le comportement de ces signaux, mais cela nécessite un équipement externe et relativement coûteux.

L'analyseur logique intégré (ILA) est une alternative qui combine les avantages des deux options précédentes. Il est simple, rapide, flexible et possède de nombreuses fonctionnalités avancées qui aident les concepteurs à visualiser et vérifier rapidement le comportement des signaux choisis.

Aperçu

Cet article contient plusieurs captures d'écran de l'interface graphique de Vivado. Cliquez sur les images pour les agrandir !

Utilisez la barre latérale pour naviguer dans le plan pour ce didacticiel, ou faites défiler vers le bas et cliquez sur le bouton de navigation contextuel dans le coin supérieur droit si vous utilisez un appareil mobile.

ILA et VIO

L'ILA et le VIO sont des IP personnalisables gratuites de Xilinx. L'ILA IP vous aide à sonder facilement les signaux internes à l'intérieur de votre FPGA et à les faire sortir dans un environnement de simulation pour les surveiller et vérifier leur comportement.

Contrairement à ILA, le VIO IP vous permet de piloter virtuellement des signaux internes à l'intérieur de votre FPGA pour stimuler ou contrôler votre conception, comme piloter le signal RESET.

- Propriété intellectuelle de Xilinx :analyseur logique intégré (ILA)

- Propriété intellectuelle de Xilinx :entrée/sortie virtuelle (VIO)

Exigences

- Une carte FPGA Xilinx

- La suite de conception Vivado

- Connaissance de base du VHDL

J'utilise le kit d'évaluation Kintex-7 FPGA KC705, mais les méthodes présentées dans ce didacticiel devraient fonctionner sur n'importe quelle carte FPGA Xilinx moderne.

Téléchargez l'exemple de projet

Vous pouvez télécharger l'exemple de projet et le code VHDL en utilisant le formulaire ci-dessous. Cela devrait fonctionner dans Vivado version 2020.2 ou plus récente.

Extrayez le Zip et ouvrez le ila_tutorial.xpr fichier dans Vivado pour voir l'exemple de conception, ou lisez le reste de cet article pour apprendre à le créer à partir de zéro.

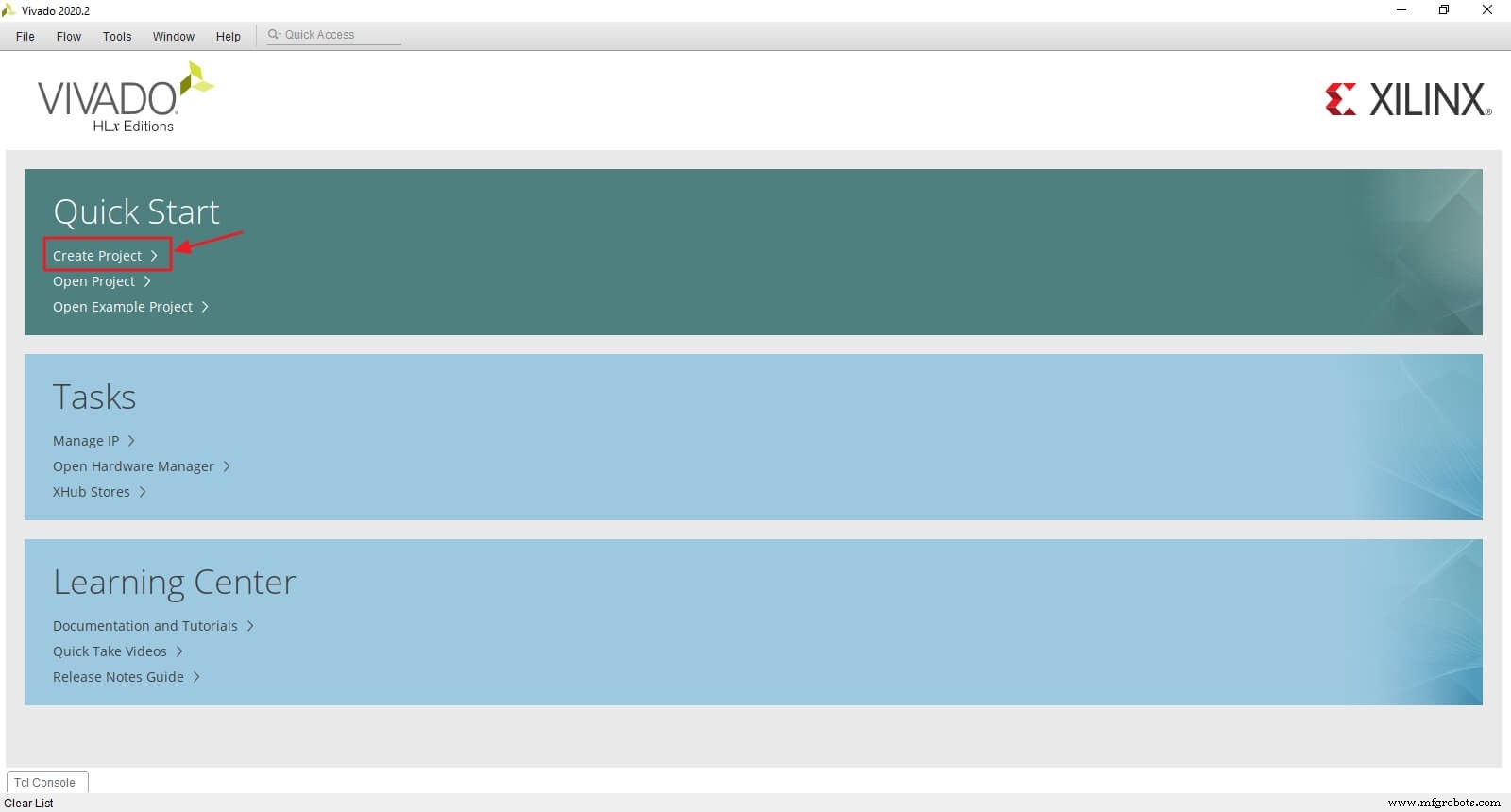

Créer un projet avec Vivado

Commencez par ouvrir Vivado. Dans l'écran de bienvenue de Vivado, cliquez sur Créer un projet bouton.

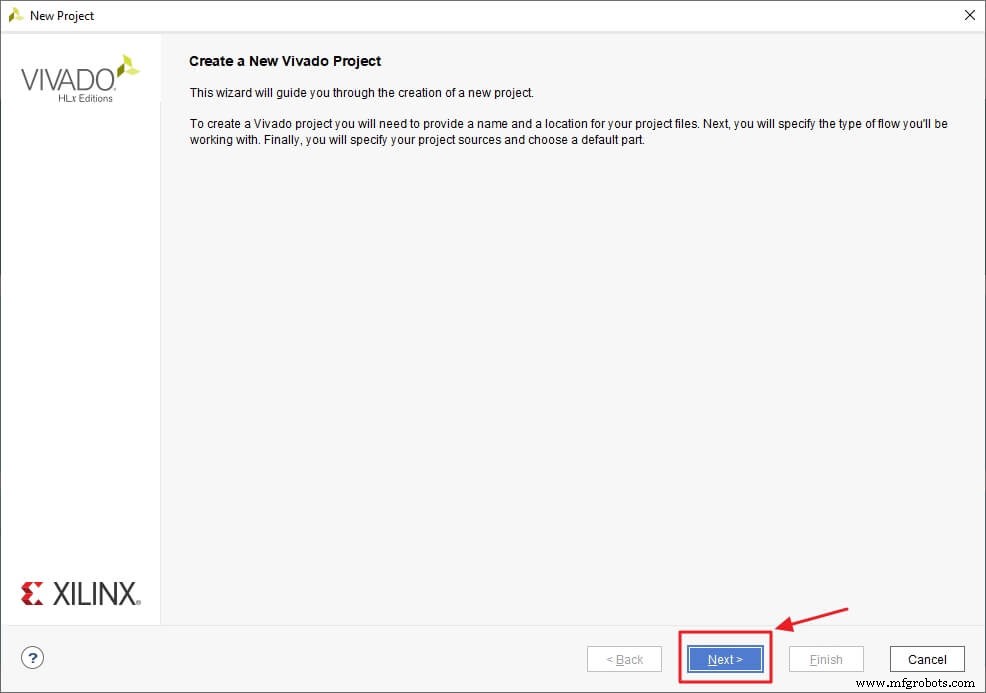

Cliquez sur Suivant pour continuer.

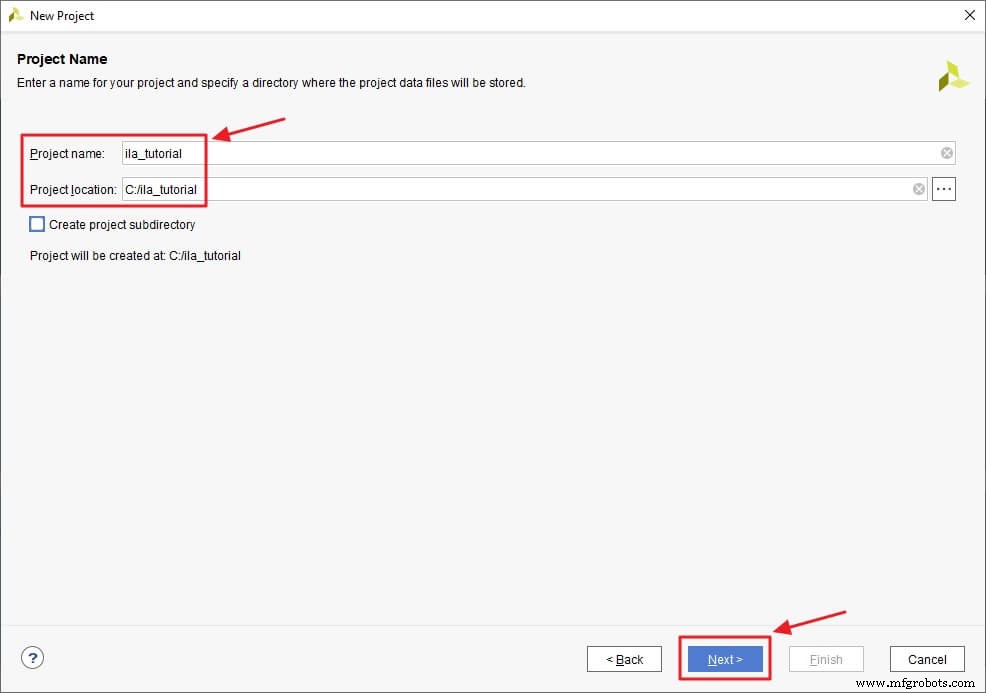

Changez le nom du projet en ila_tutorial et cliquez sur Suivant.

Remarque : N'utilisez pas d'espaces dans le nom du projet. Utilisez plutôt un trait de soulignement ou un tiret.

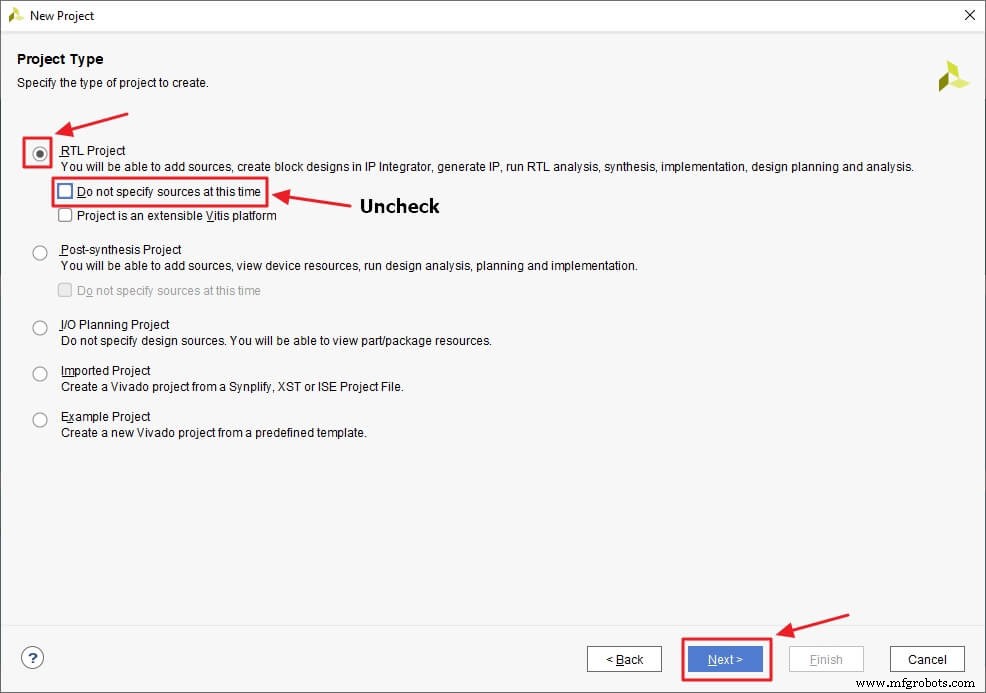

Choisissez Projet RTL et décochez Ne pas spécifier les sources pour le moment et cliquez sur Suivant pour continuer.

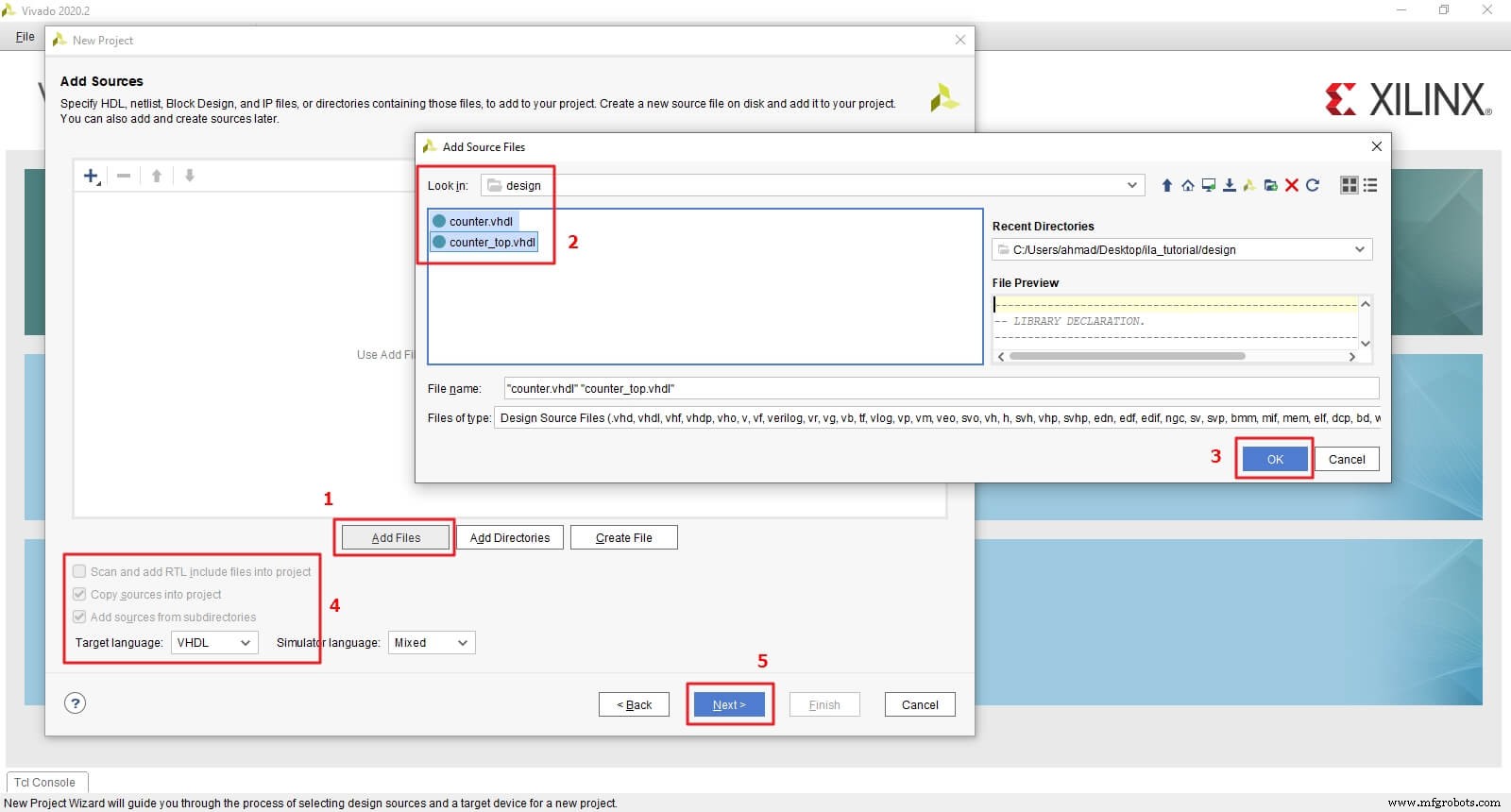

Ajoutez les fichiers sources ; counter.vhdl et counter_top.vhdl du dossier de conception. Choisissez VHDL pour la langue cible. Cochez Copier les sources dans le projet et cliquez sur Suivant pour continuer.

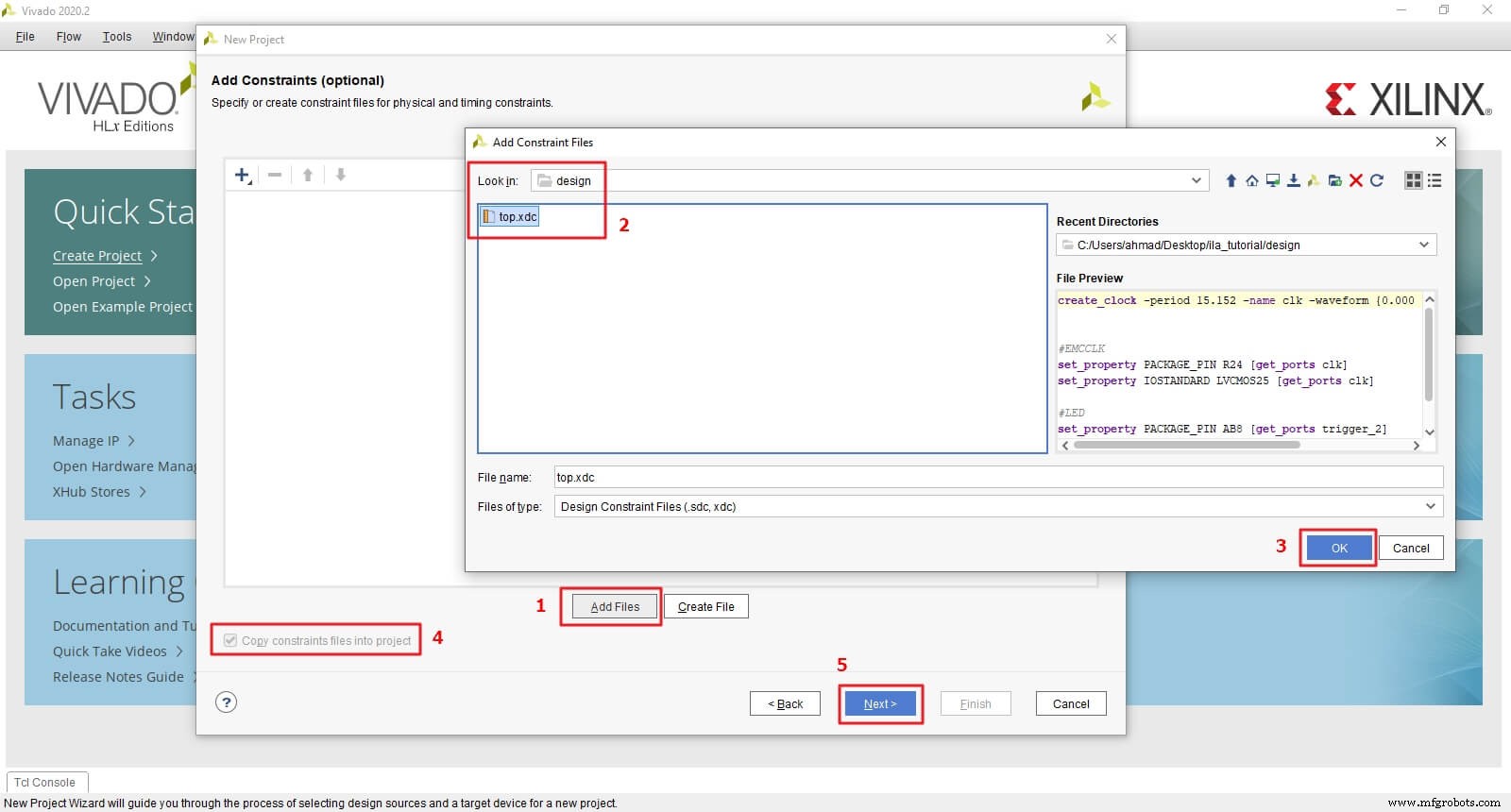

Ajoutez le fichier de contraintes top.xdc du dossier de conception. Cochez Copier les fichiers de contraintes dans le projet et cliquez sur Suivant pour continuer.

Remarque : ce fichier de contraintes est spécifique à la carte KC705. Vous devez changer le clk pin et la goupille led selon votre tableau. Et aussi, la -période de votre horloge embarquée.

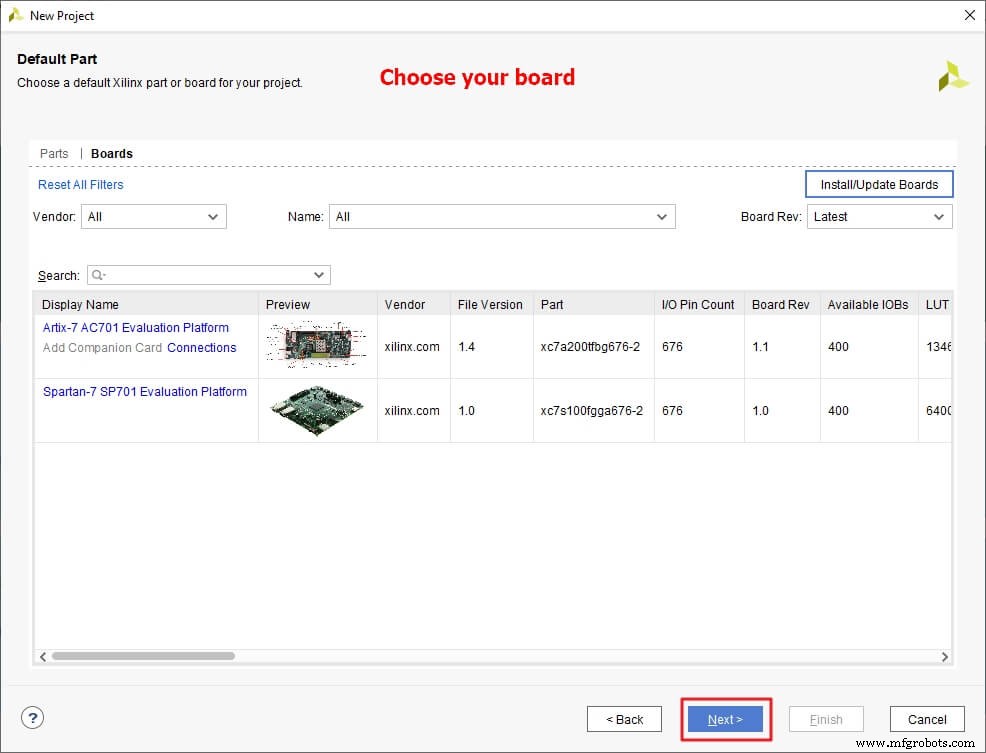

Recherchez votre tableau et sélectionnez-le dans la liste. Cliquez sur Suivant pour continuer.

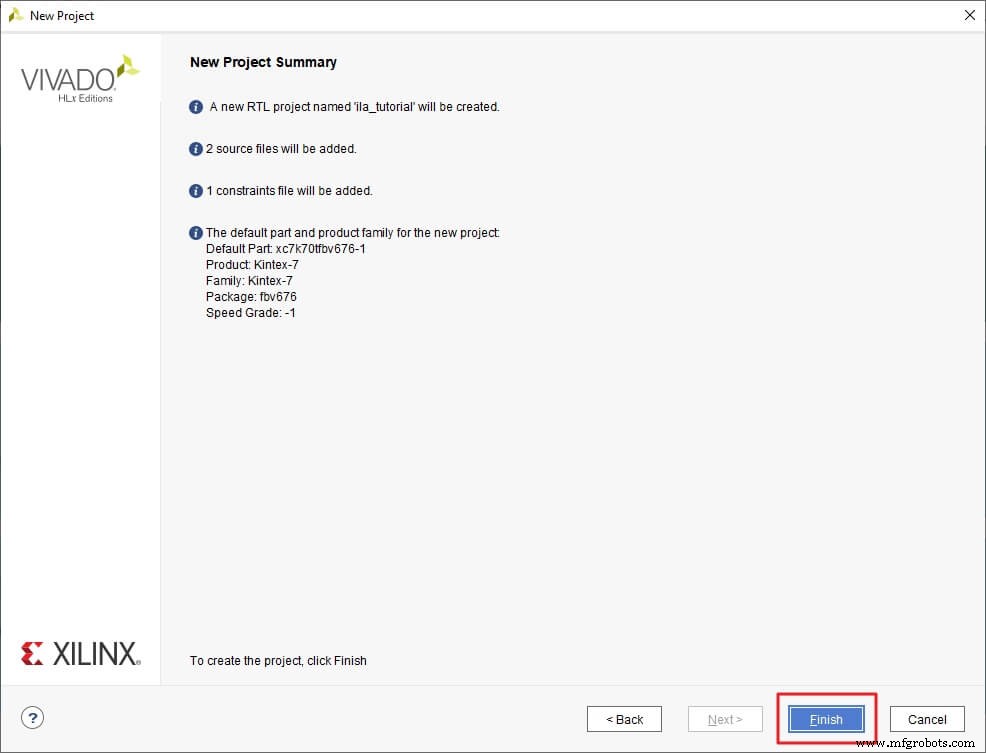

Il s'agit du dernier écran de l'assistant Nouveau projet. Cliquez sur Terminer pour ouvrir votre projet.

L'explication de l'exemple de conception

Nous utiliserons un exemple simple de chaîne à deux compteurs pour ce didacticiel.

Le counter.vhdl contient le code RTL pour un compteur trivial de 4 bits qui compte de 0 à 15 lorsqu'il est activé. Il affirme la sortie 1 bit lorsque le nombre est compris entre 12 et 15. Pour toutes les autres valeurs, la sortie reste low '0' .

Voici l'interface d'entité pour le module compteur.

----------------------------------------------------------------------------

-- ENTITY DECLARATION.

----------------------------------------------------------------------------

ENTITY counter IS

PORT(clk : IN STD_LOGIC; -- Main clock

reset : IN STD_LOGIC; -- reset, active_high

enable : IN STD_LOGIC; -- enable the next counter

trigger : OUT STD_LOGIC -- trigger the next counter

);

END ENTITY;

La conception du compteur comporte deux signaux internes :count et trigger_o .

– compter est utilisé pour implémenter la fonctionnalité de comptage.

– et trigger_o est un signal intermédiaire pour connecter le port de sortie trigger .

Ne vous souciez pas de ATTRIBUT , cela sera expliqué plus tard.

----------------------------------------------------------------------------

-- ARCHITECTURE DECLARATION.

----------------------------------------------------------------------------

ARCHITECTURE rtl OF counter IS

-- INTERNAL SIGNALS DECLARATION --

SIGNAL count : UNSIGNED(3 DOWNTO 0) := (OTHERS => '0');

SIGNAL trigger_o : STD_LOGIC := '0';

-- ATTRIBUTE DECLARATION --

ATTRIBUTE MARK_DEBUG : STRING;

ATTRIBUTE MARK_DEBUG OF count : SIGNAL IS "true";

Dans la liste ci-dessous, nous voyons l'implémentation du compteur. Le seq_proc le processus est déclenché sur le front montant du port d'entrée clk et est en mode de réinitialisation lorsque le port d'entrée réinitialise est élevé "1".

Le compte le signal est incrémenté lorsque le port d'entrée active est élevé "1", et le trigger_o le signal est affirmé haut lorsque la valeur du signal compte est compris entre 12 et 15.

seq_proc: PROCESS (reset, clk)

BEGIN -- for seq_proc

IF (reset = '1') THEN

count <= (OTHERS => '0');

trigger_o <= '0';

ELSIF rising_edge(clk) THEN

IF (enable = '1') THEN

count <= count + 1;

IF (count > x"B" AND count <= x"F") THEN

trigger_o <= '1';

ELSE

trigger_o <= '0';

END IF;

END IF;

END IF;

END PROCESS;

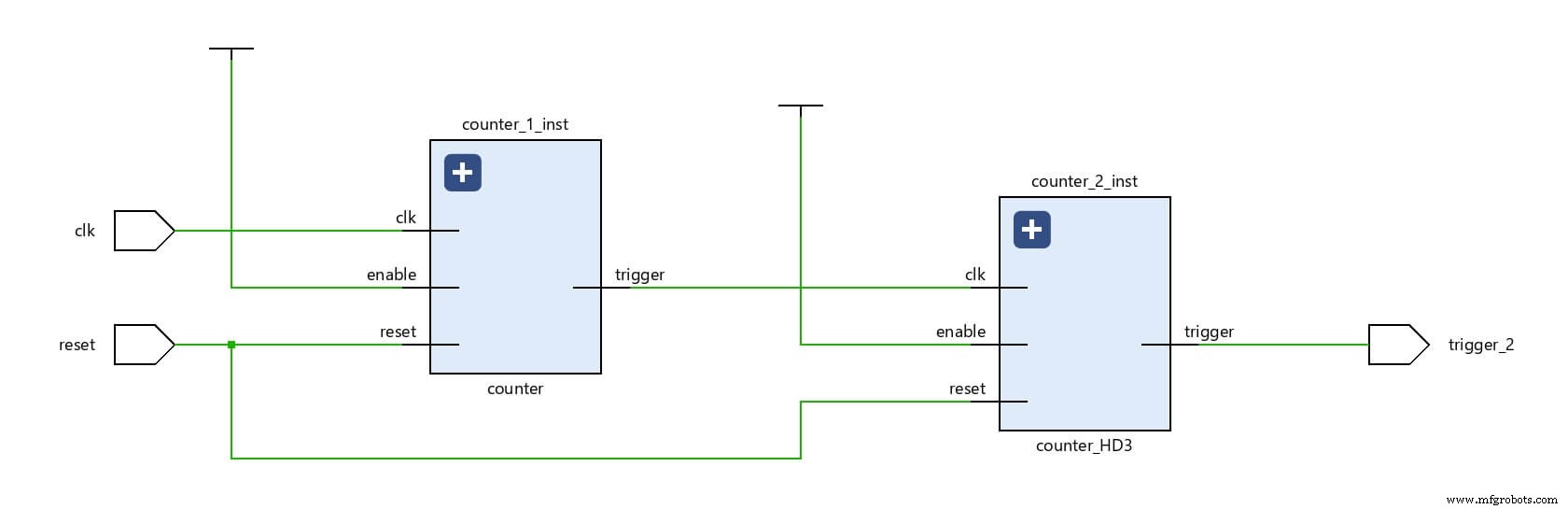

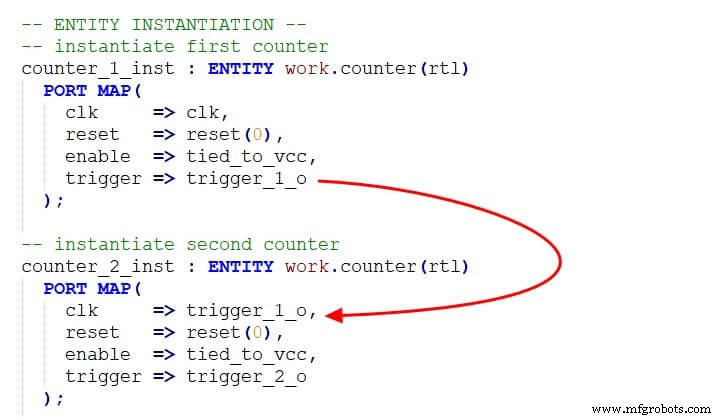

Le fichier counter_top.vhdl contient deux instants du compteur connectés séquentiellement.

– Le counter_1_inst est toujours activé et il cadence le counter_2_inst . Autrement dit, le port de sortie déclencheur de counter_1_inst est connecté au port d'entrée clk de counter_2_inst .

– Le comportement résultant est que counter_1_inst active counter_2_inst seulement 4 cycles d'horloge sur 16. Ainsi, counter_2_inst incrémentera son compteur quatre fois tous les 16 comptes.

Création du noyau VIO pour RESET

Maintenant que vous comprenez l'exemple de conception, nous allons créer un VIO pour contrôler le port d'entrée réinitialiser . Cela nous donnera la possibilité de manipuler (basculer) la réinitialisation de Vivado IDE afin que nous puissions contrôler manuellement quand démarrer/arrêter les compteurs.

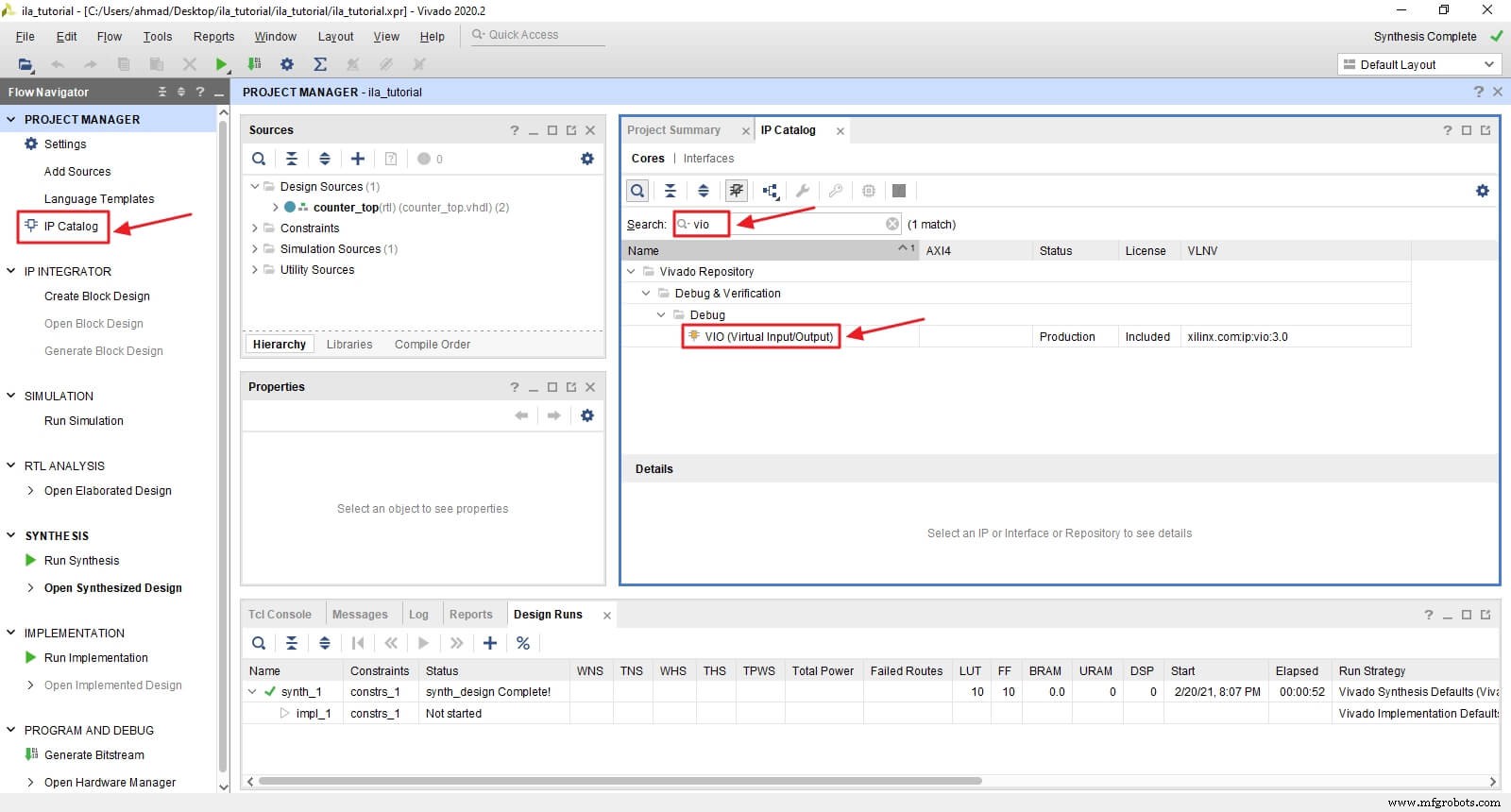

Cliquez sur Catalogue IP , puis recherchez VIO , puis double-cliquez sur VIO (Virtual Input/Output) .

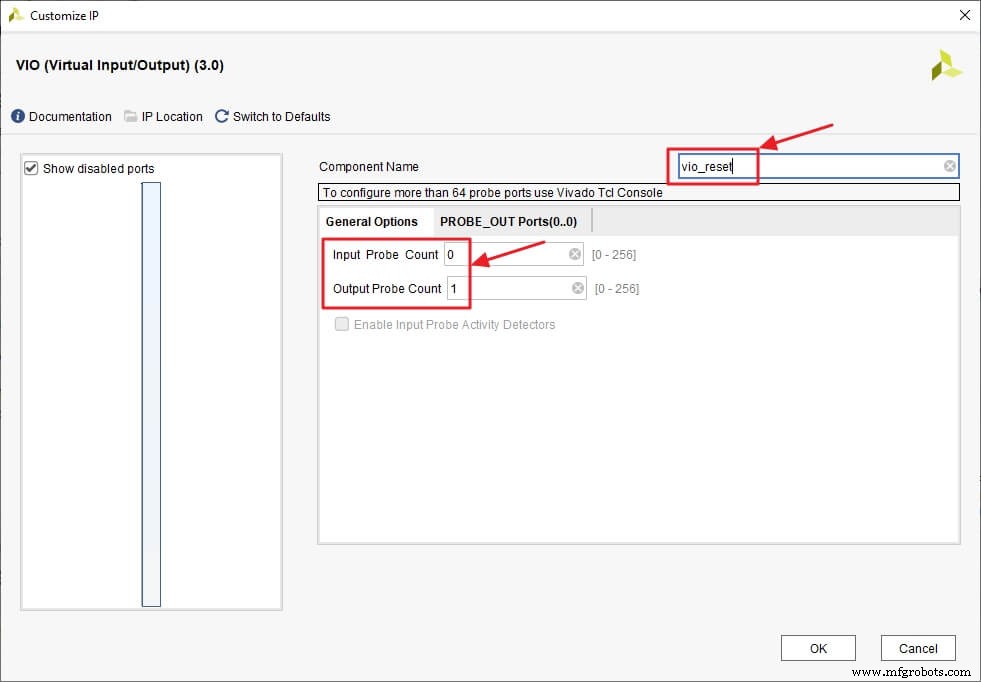

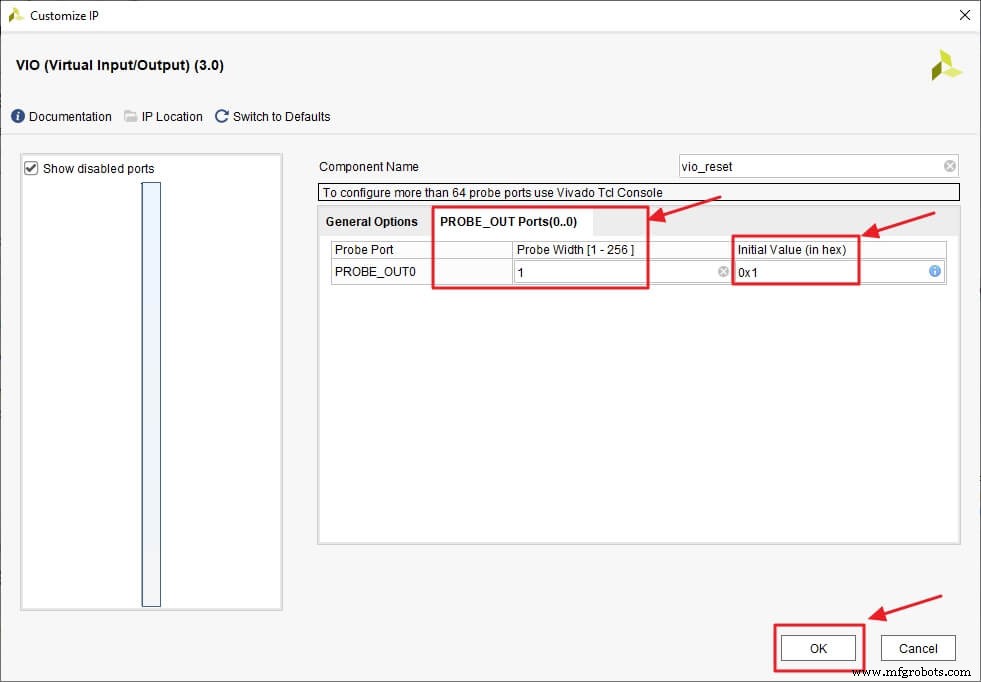

Tout d'abord, nous changeons le nom en vio_reset .

Deuxièmement, nous n'avons besoin que d'un port de sortie pour la réinitialisation, nous mettons donc 0 dans la case du nombre de sondes d'entrée, et nous mettons 1 dans la case du nombre de sondes de sortie .

Cliquez sur PROBE_OUT onglet ports. Comme reset est un signal 1 bit, nous mettons 1 dans la case probe_width, et nous avons également mis 0x1 dans la case de valeur initiale il commence donc par un « 1 » élevé. Cliquez ensuite sur OK et Générer . Vivado va maintenant commencer à synthétiser le VIO.

Une fois que Vivado a fini de synthétiser le VIO, nous devons l'ajouter à notre conception en déclarant un composant pour celui-ci et en l'instanciant dans le counter_top.vhdl fichier comme ci-dessous.

Tout d'abord, ajoutez une déclaration de composant pour le vio_reset dans la section de déclaration de composant dans le counter_top.vhdl fichier.

-- Declare vio_reset

COMPONENT vio_reset

PORT(

clk : IN STD_LOGIC;

probe_out0 : OUT STD_LOGIC_VECTOR(0 DOWNTO 0)

);

END COMPONENT;

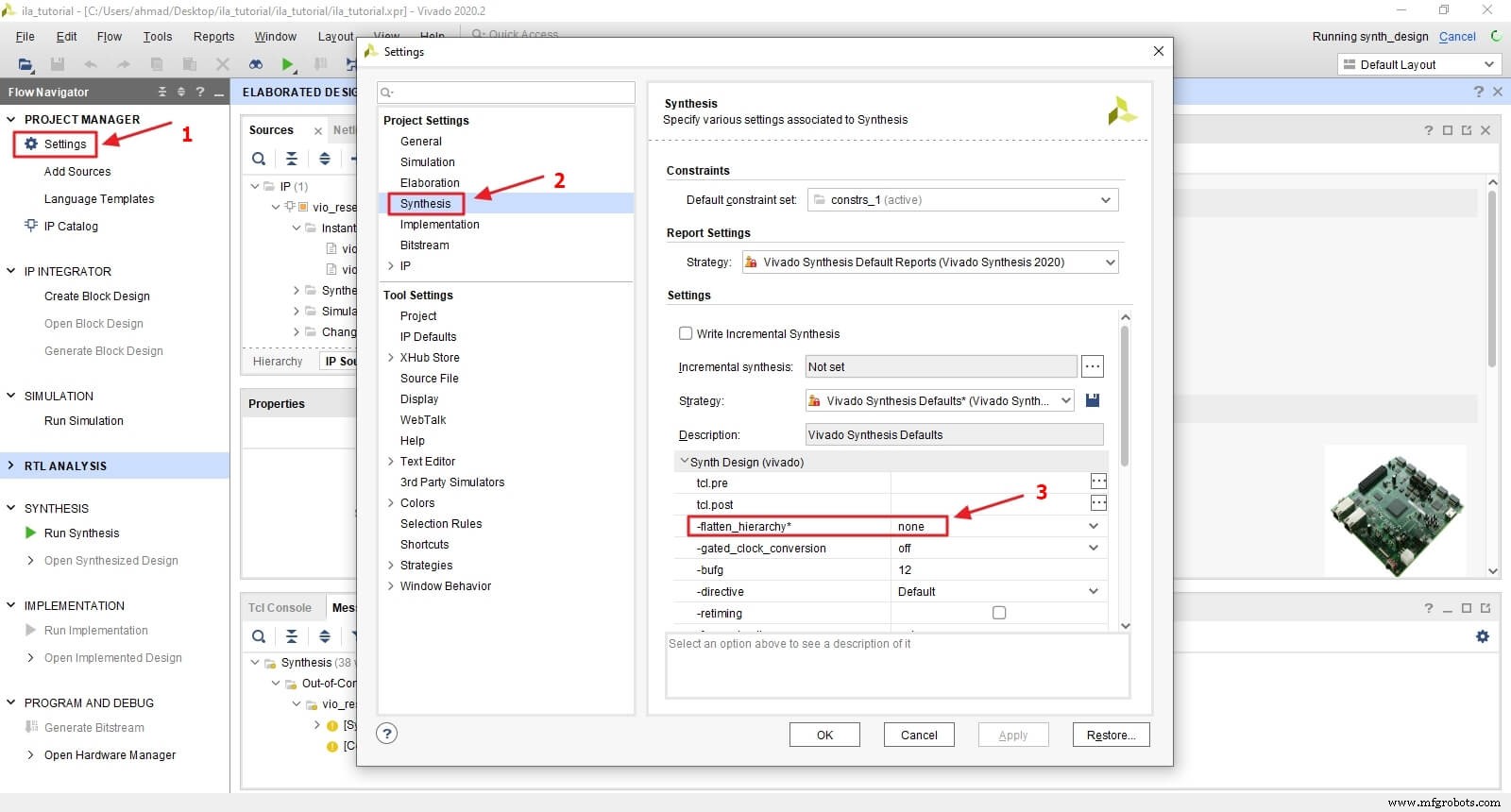

Maintenant, le VIO est terminé et nous sommes prêts à synthétiser la conception. Mais avant cela, nous devons modifier le paramètre de synthèse flatten_hierarchy à Aucun .

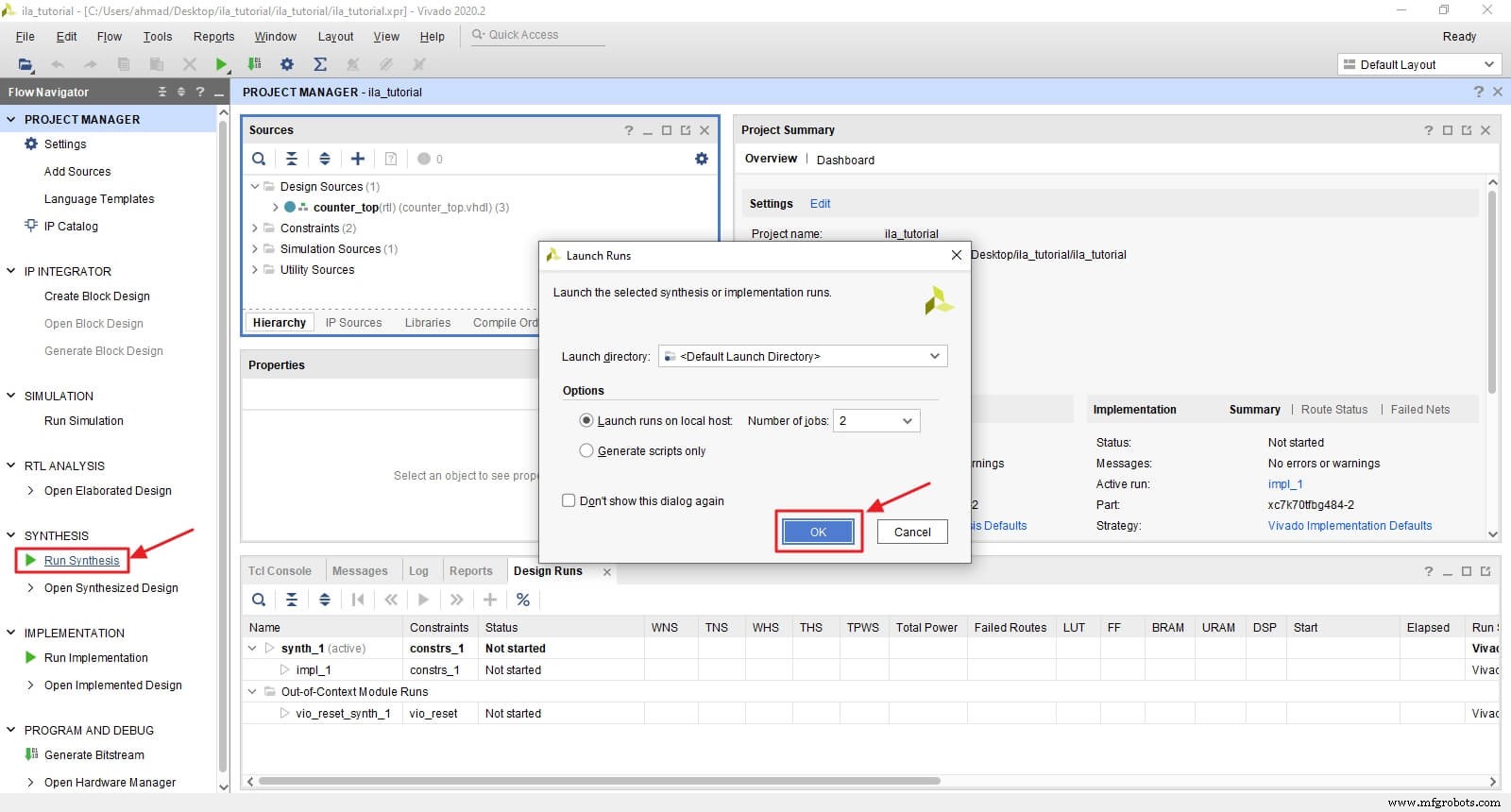

Cliquez sur Exécuter la synthèse puis sur OK .

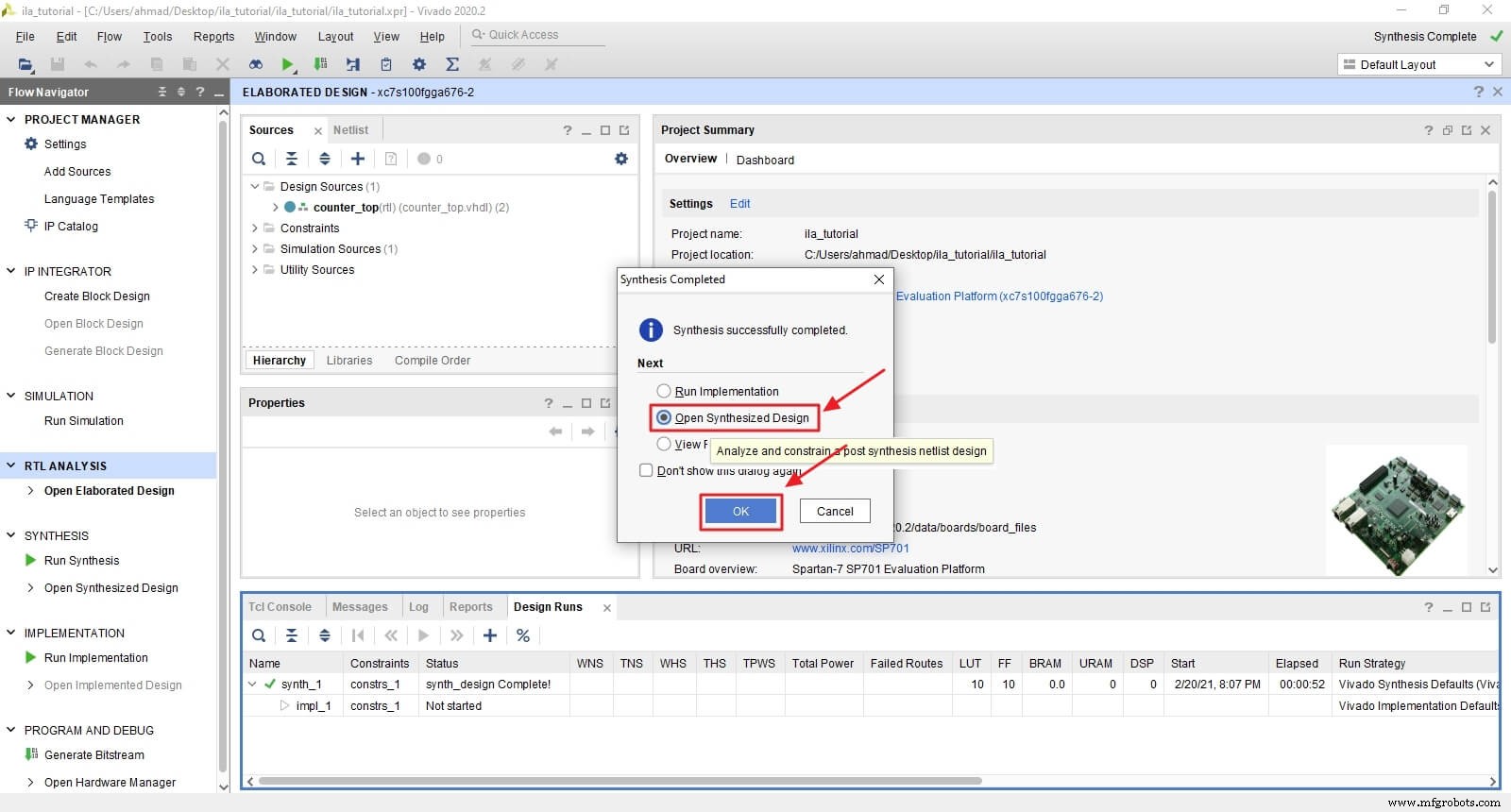

Lorsque Vivado termine la synthèse, cliquez sur Open Synthesized Design .

Changer la mise en page pour déboguer en cliquant sur Mise en page puis Débogage .

Insérer le flux de la sonde de débogage

Notre conception synthétisée contient maintenant le vio_reset exemple, et il est temps de spécifier les signaux que nous voulons sonder. Il existe trois façons de procéder :

- Insertion depuis un fichier VHDL

- Insertion depuis la Netlist

- Insertion à partir du fichier xdc/tcl

Nous utiliserons les deux premières méthodes et laisserons la troisième pour un tutoriel ultérieur.

Insertion depuis un fichier VHDL

Cette méthode est le moyen le plus simple et le plus rapide d'insérer une sonde, en particulier lorsqu'il s'agit d'un type composite (tableau ou enregistrement). Mais cela nécessite d'ajouter du code aux fichiers de conception, du code VHDL qui est redondant dans le produit réel.

Nous pouvons insérer une sonde dans le fichier de conception VHDL en :

- Déclarer un attribut spécial appelé MARK_DEBUG

- Attachez le signal que nous voulons sonder avec cet attribut

- Et activez-le en lui donnant la valeur "true" comme ci-dessous :

-- ATTRIBUTE DECLARATION --

ATTRIBUTE MARK_DEBUG : STRING;

ATTRIBUTE MARK_DEBUG OF count : SIGNAL IS "true";

Remarque : nous n'avons besoin de déclarer l'attribut qu'une seule fois dans chaque fichier de conception VHDL, ce qui nous permet de l'attacher à plusieurs signaux.

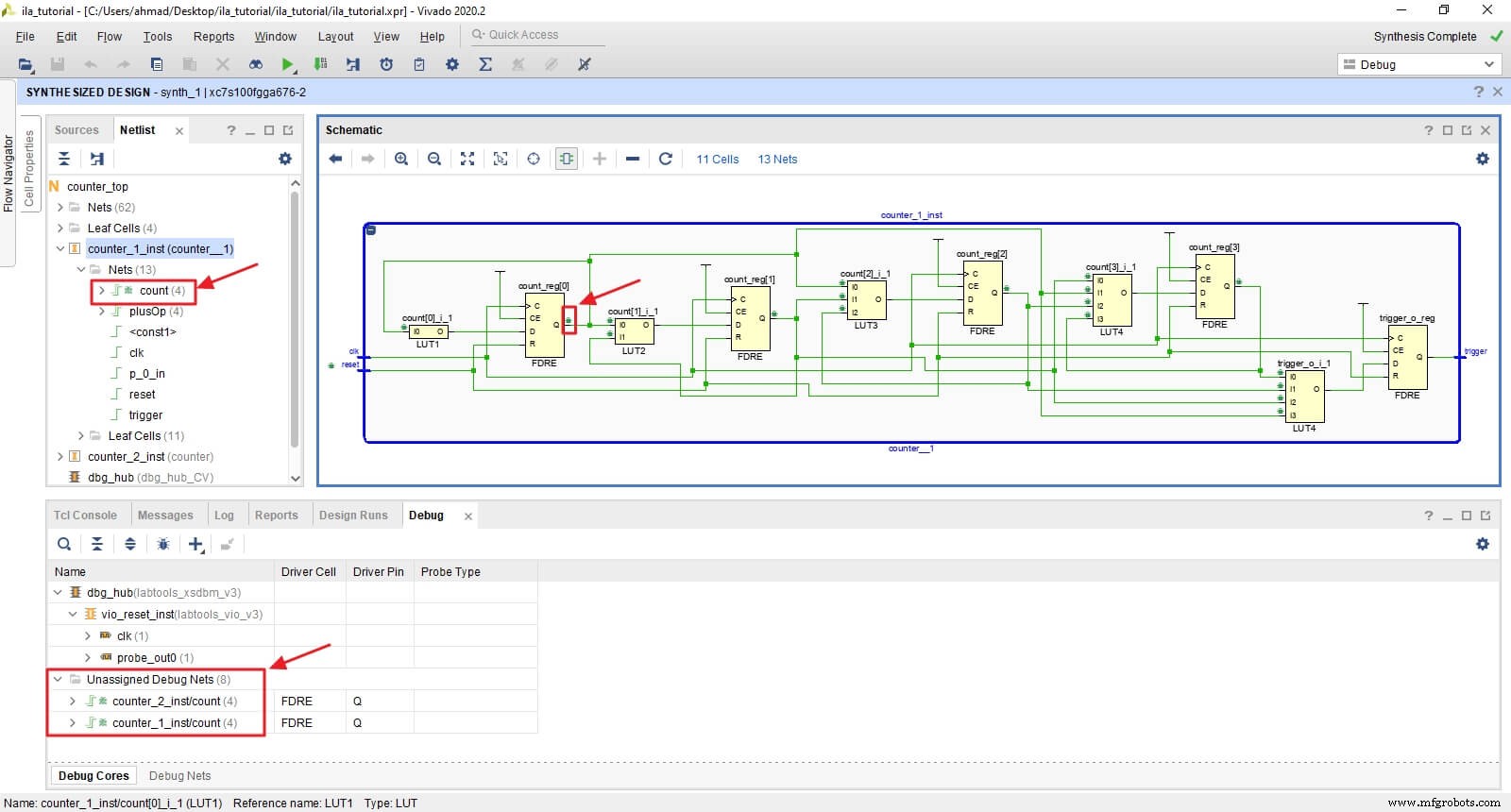

Nous pouvons voir à partir de la conception synthétisée que le signal compte dans les deux counter_1_inst et counter_2_inst sont répertoriés sous Réseaux de débogage non attribués et marqué d'une icône de bogue dans la Netlist et le Schéma .

Insertion depuis la Netlist

Cette méthode d'insertion est également simple, mais elle nécessite que vous synthétisiez d'abord la conception, puis que vous cliquiez manuellement sur chaque signal pour le marquer pour le débogage. Cela peut être épuisant si la conception est grande et que vous souhaitez surveiller de nombreux signaux.

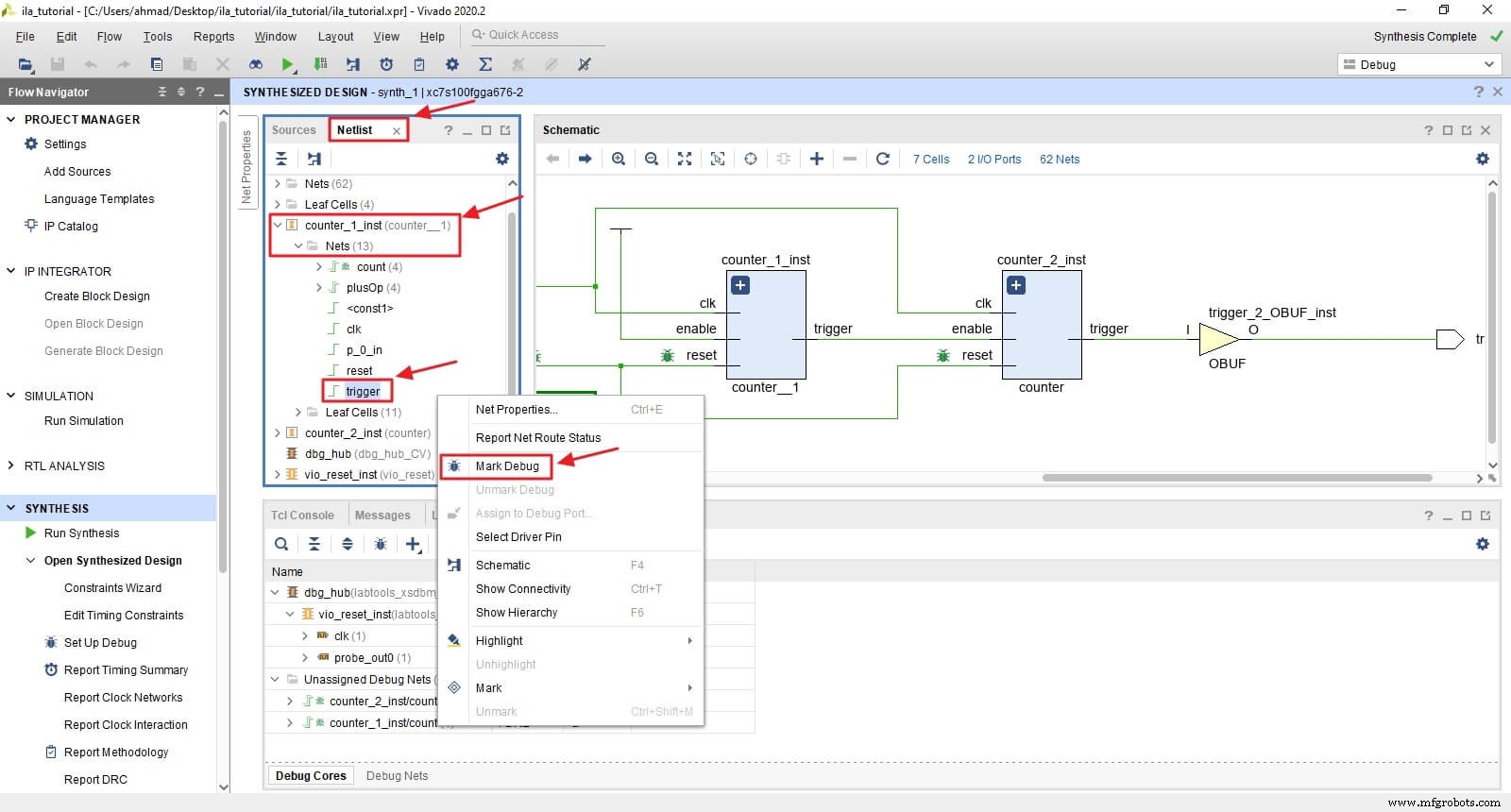

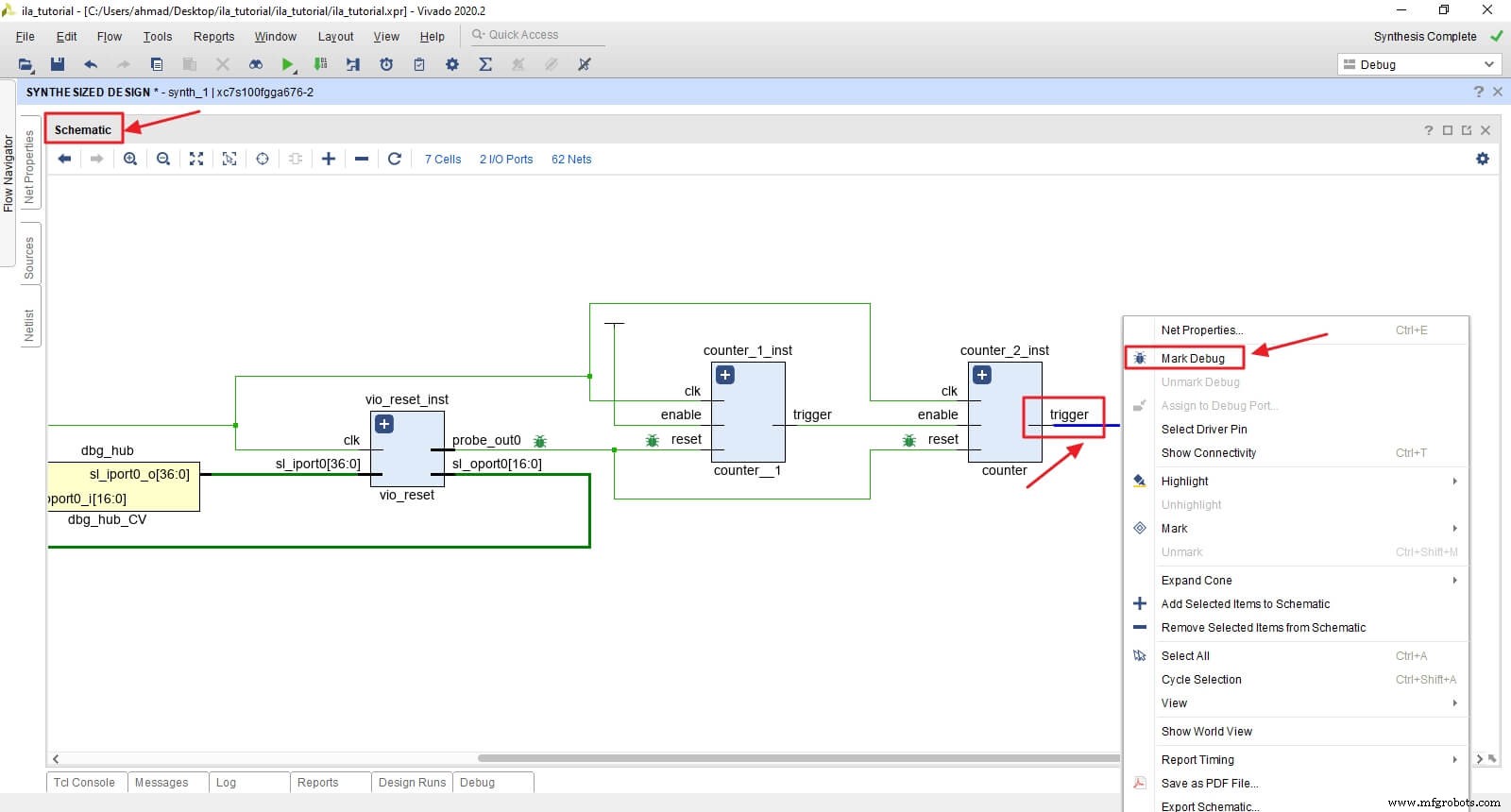

Nous allons sonder le déclencheur du port de sortie dans les deux compteurs en utilisant la Netlist . Nous pouvons le faire soit depuis la fenêtre Netlist ou le Schéma en localisant le réseau de signaux, puis faites un clic droit dessus et choisissez Marquer le débogage .

Dans la fenêtre Netlist, recherchez déclencheur sous counter_1_inst → Réseaux → déclencheur . Ensuite, faites un clic droit dessus et choisissez Marquer le débogage .

Dans la fenêtre Schéma, recherchez déclencheur sortie de counter_2_inst . Ensuite, faites un clic droit dessus et choisissez Marquer le débogage .

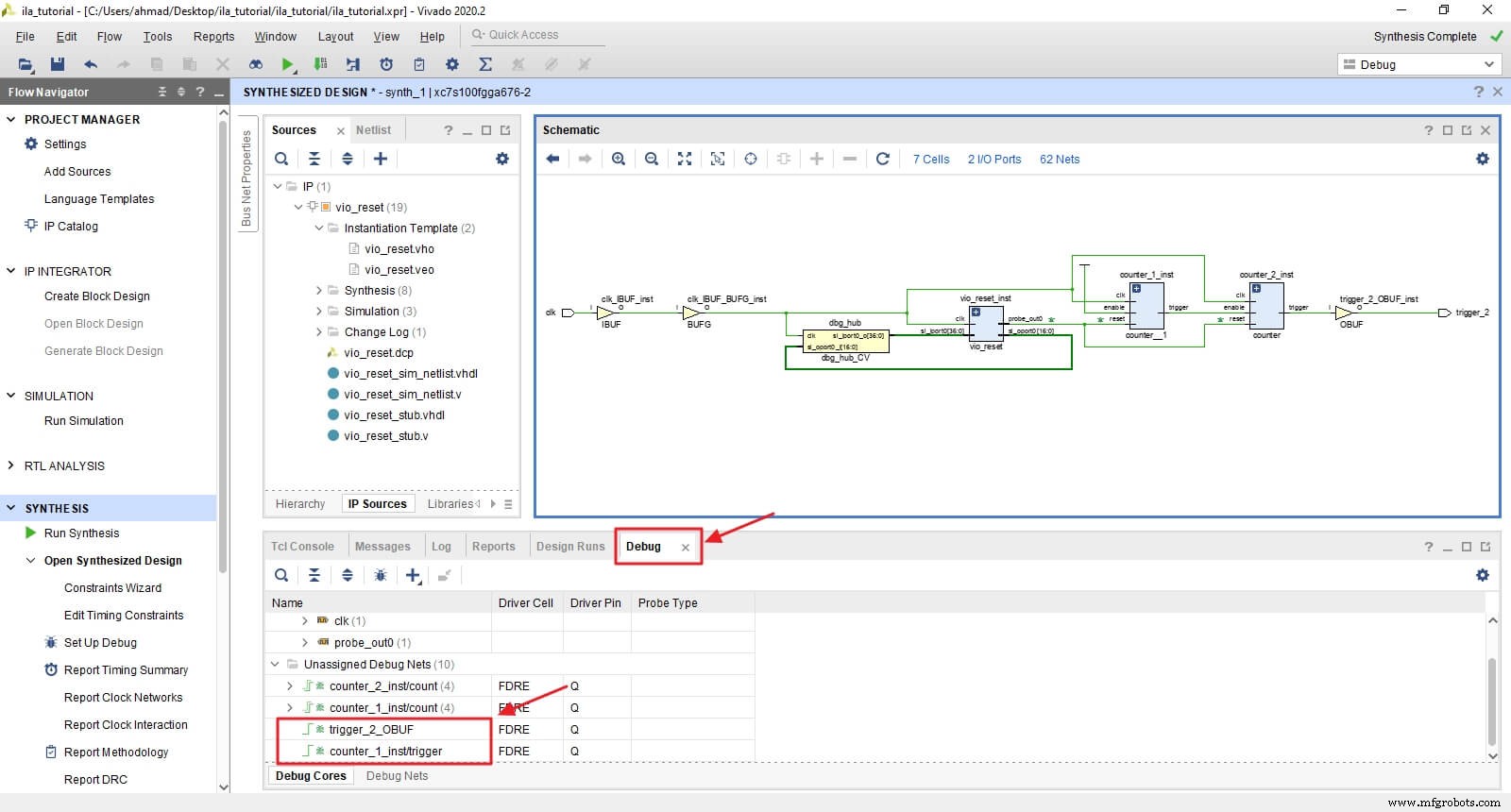

Nous pouvons voir qu'ils sont maintenant répertoriés sous Réseaux de débogage non attribués .

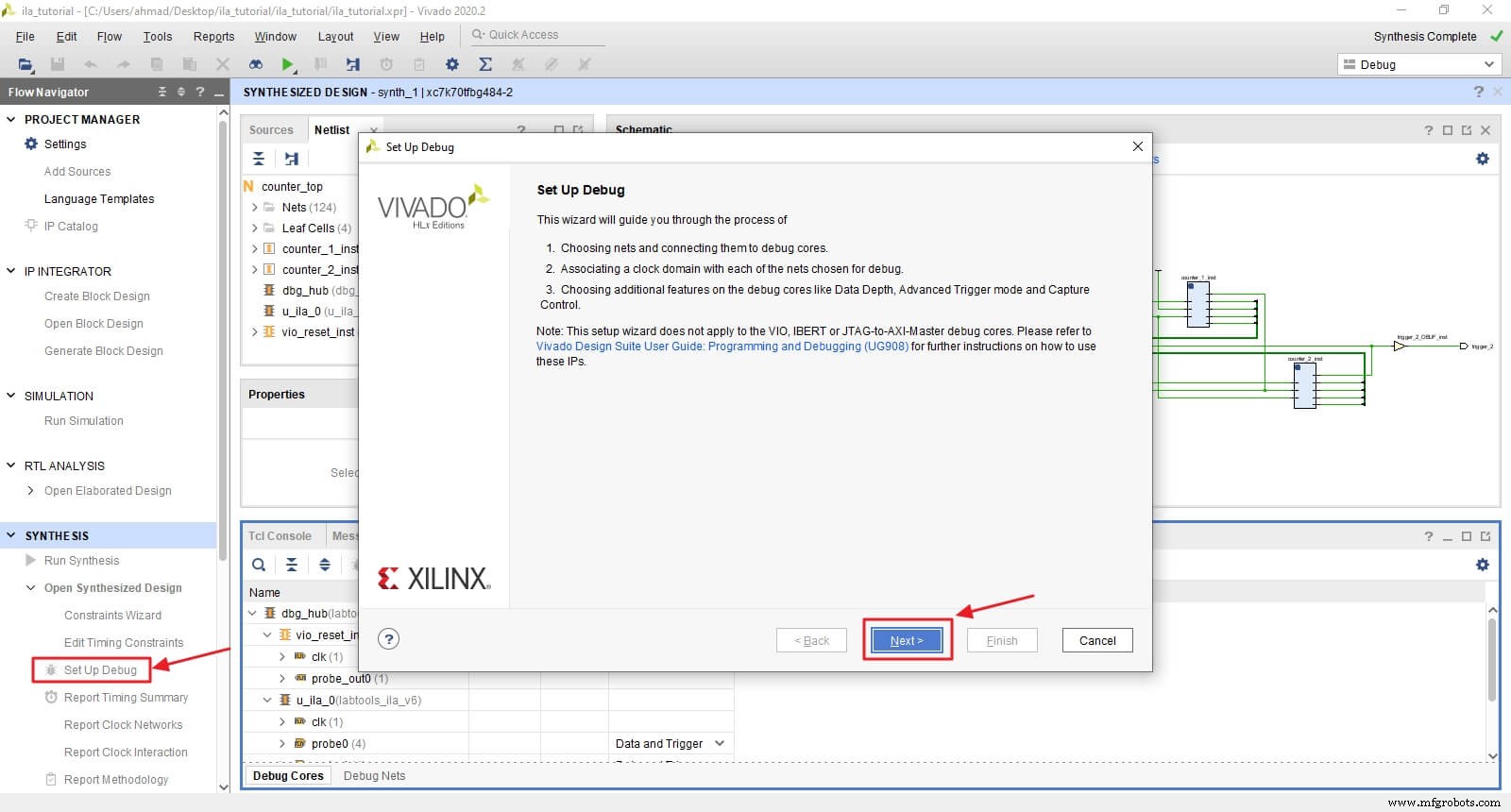

Création du noyau de débogage ILA

Il est maintenant temps de créer le noyau de débogage ILA. Nous devons créer une sonde pour chaque signal que nous voulons analyser. Le moyen le plus simple est de profiter de l'assistant Vivado Configurer le débogage .

Cliquez sur Configurer le débogage puis cliquez sur Suivant .

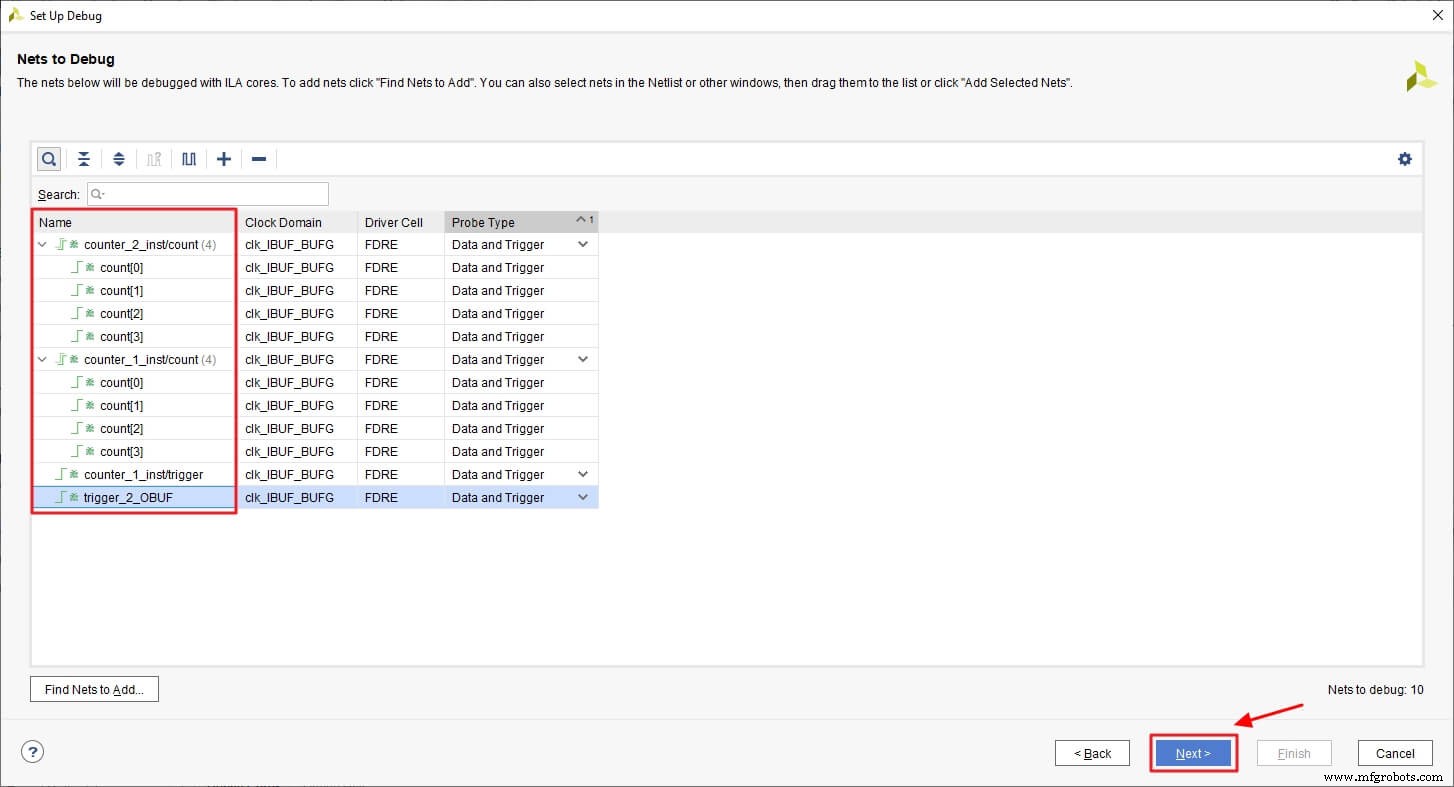

Vivado listera tous les signaux de débogage et capturera automatiquement le domaine d'horloge pour vous. Ici, nous voyons que nos quatre signaux sont répertoriés. Vous pouvez supprimer les signaux qui ne vous intéressent pas ou ajouter des signaux supplémentaires, mais nous les utiliserons tous.

Remarque : nous n'avons pas besoin d'utiliser tous les signaux que nous avons marqués comme Debug.

Cliquez sur Suivant .

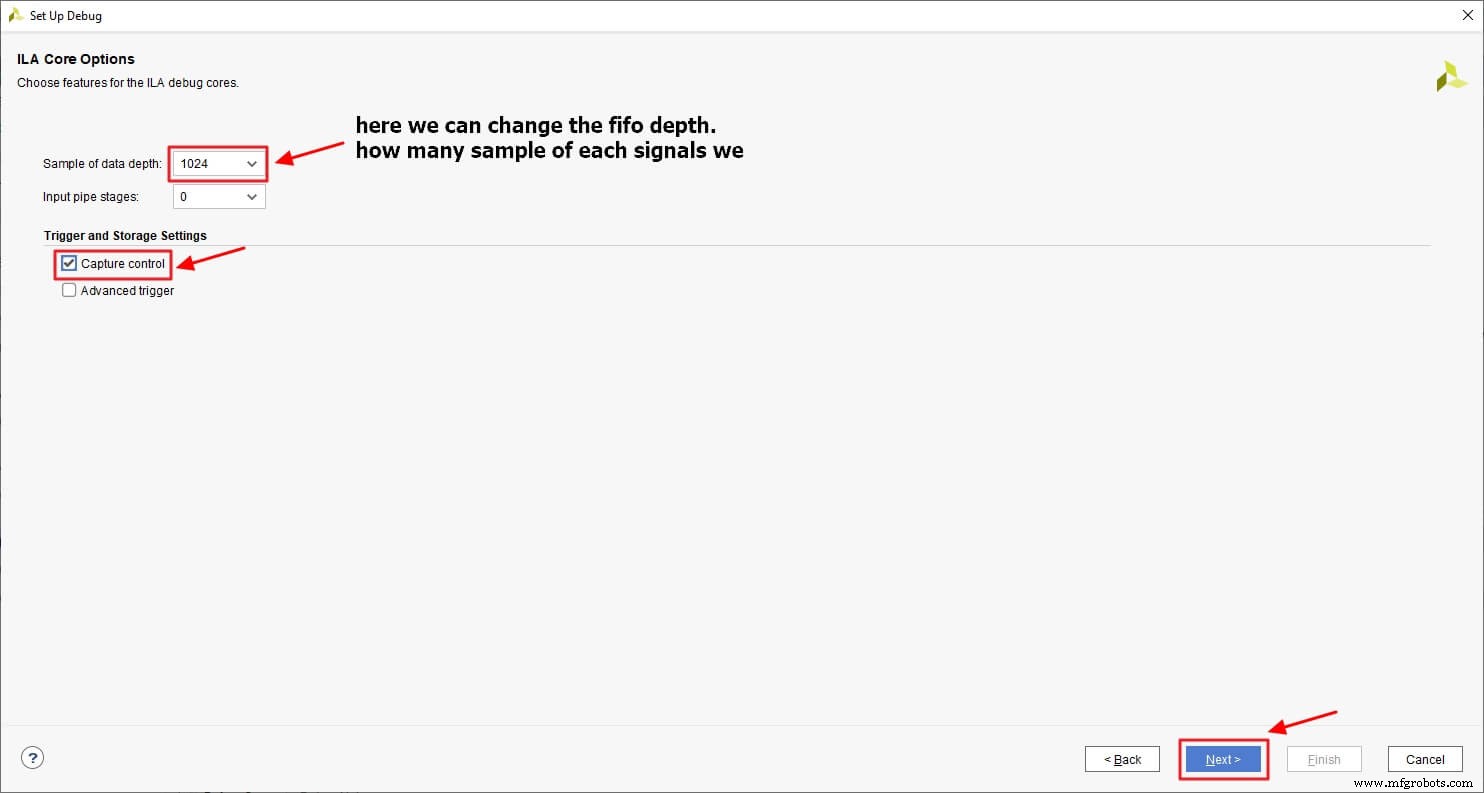

Maintenant, nous configurons l'ILA en choisissant la profondeur FIFO et en vérifiant le contrôle de capture . Nous pouvons laisser le FIFO à 1024 car c'est assez de profondeur pour notre exemple.

Cliquez sur Suivant .

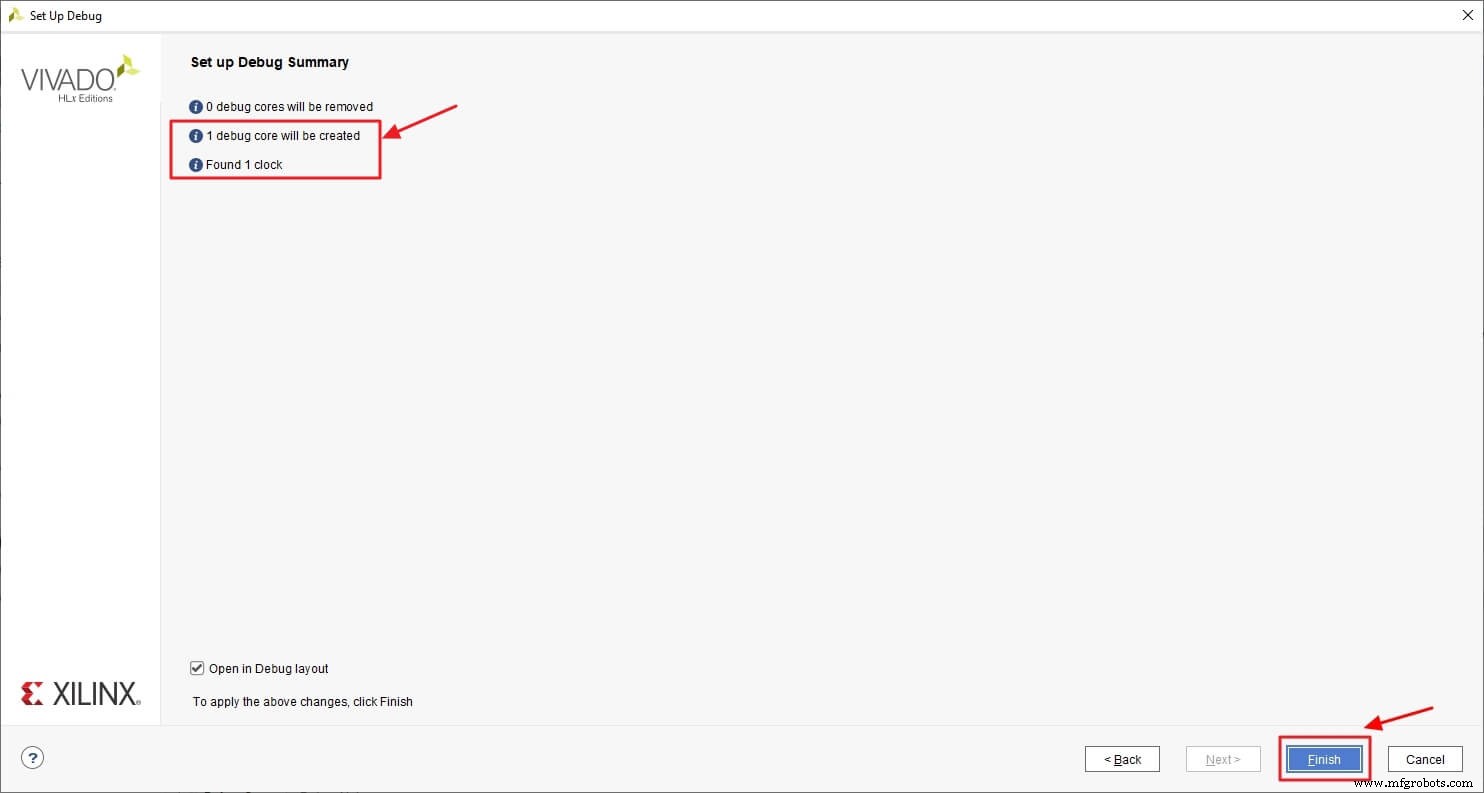

Nous voyons maintenant que Vivado a trouvé une horloge et créera un noyau de débogage.

Cliquez sur Terminer .

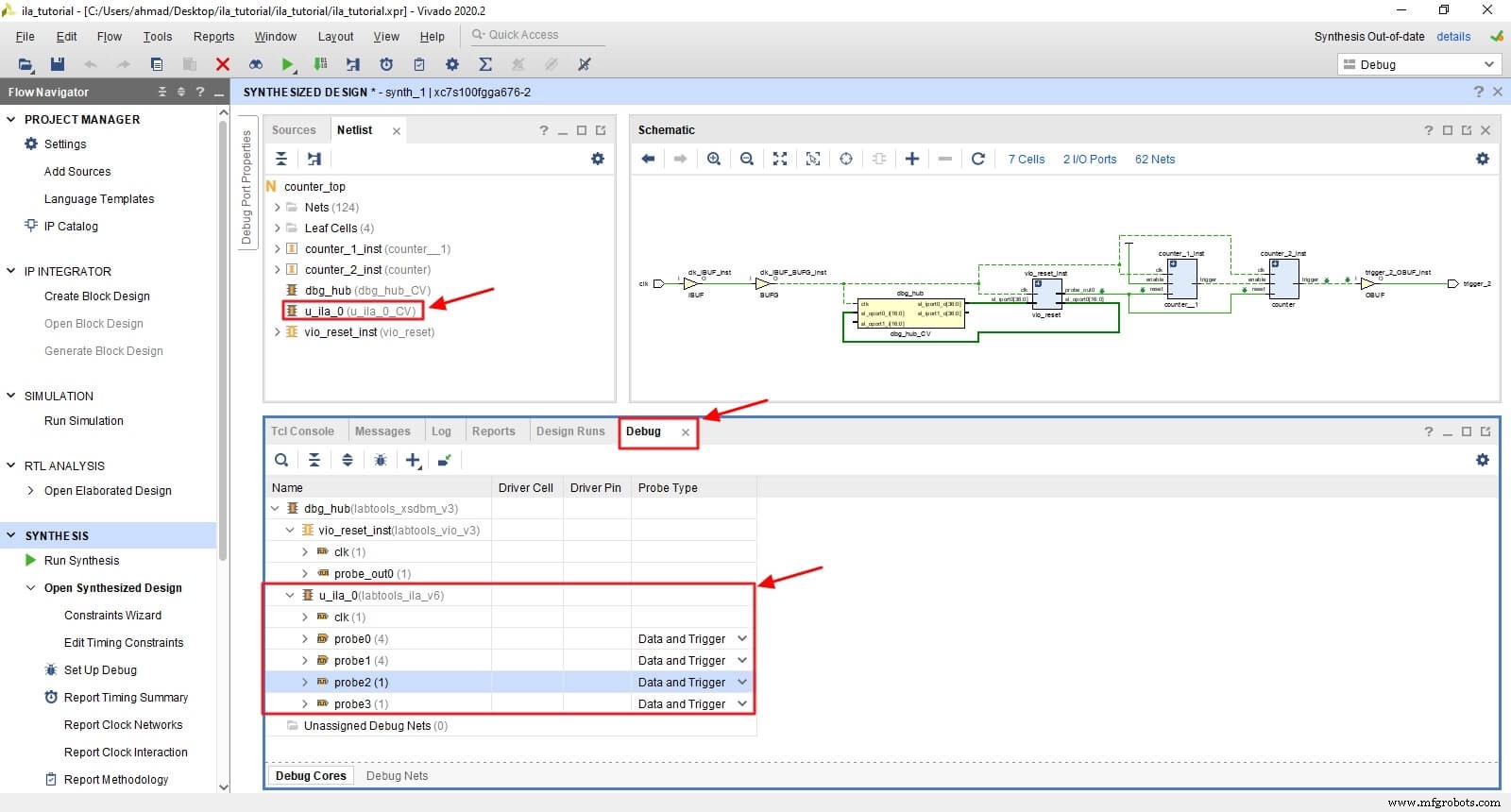

Nous pouvons maintenant voir un noyau de débogage ILA avec quatre sondes ajoutées à l'onglet de débogage et la fenêtre Netlist .

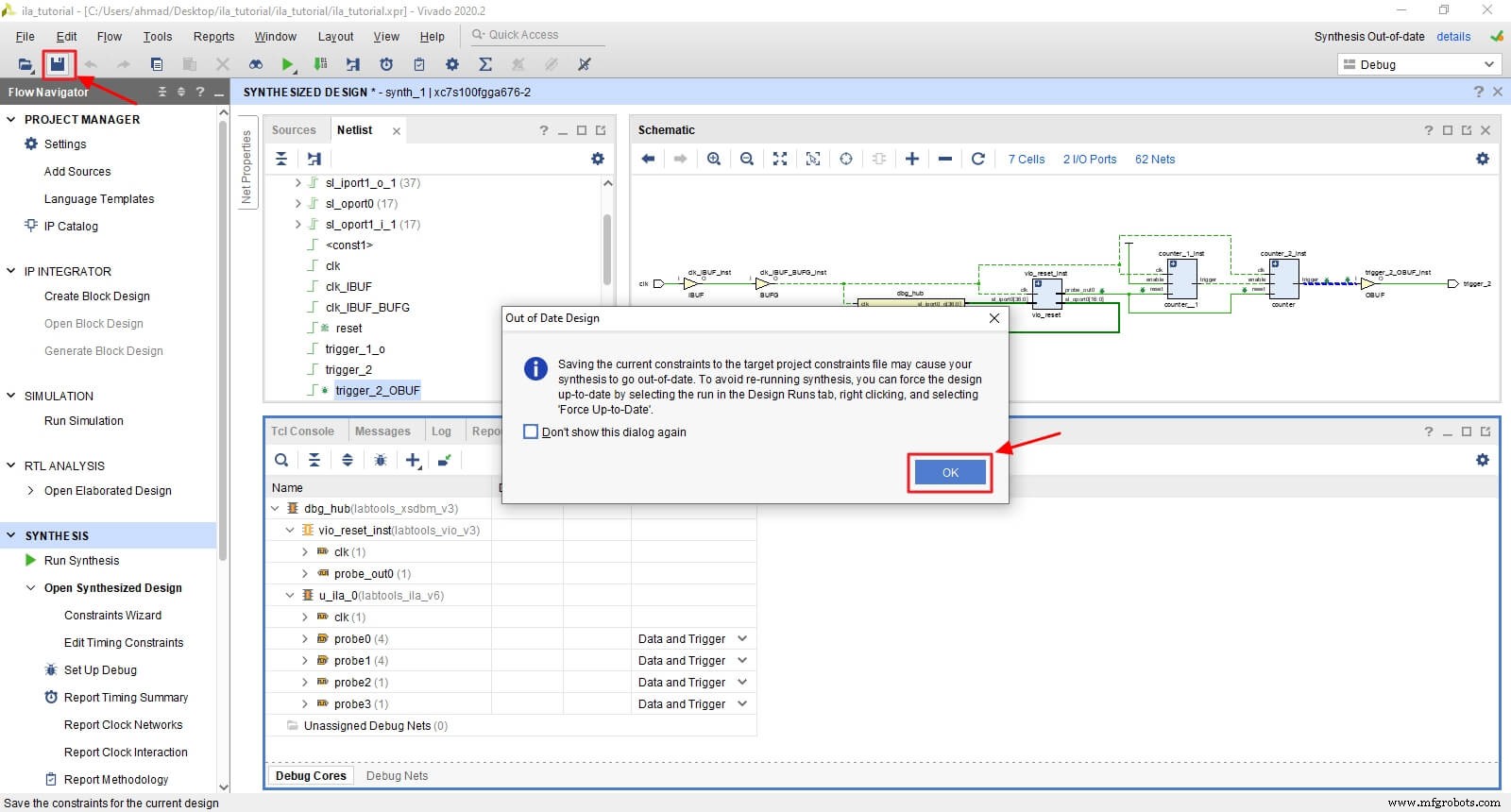

IMPORTANT : Il est très important de sauvegarder la contrainte à ce stade afin qu'elle puisse être ajoutée à la conception. Sinon, nous risquons de perdre notre noyau ILA.

Cliquez sur Enregistrer ou appuyez sur Ctrl+S.

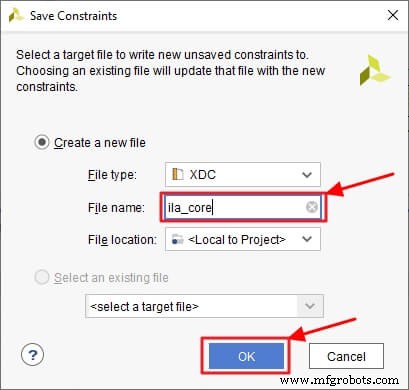

Nommez le fichier ila_core et cliquez sur OK .

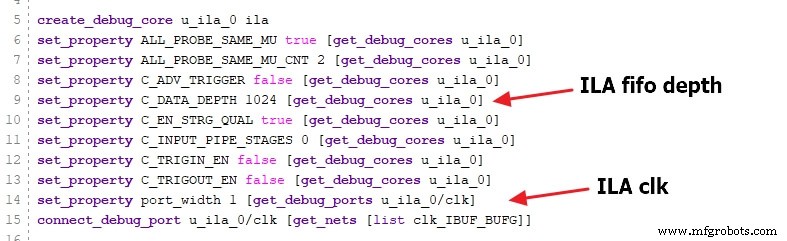

Le fichier ila_core.xdc sera ajouté à la contrainte, et il inclut le code et les paramètres de l'ILA.

Examinons le contenu du fichier. Vous pouvez ouvrir le fichier en allant dans la fenêtre source → développer le dossier de contraintes → développer constr_1 .

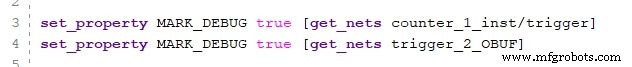

Tout d'abord, nous voyons que le fichier ajoute un attribut de débogage aux signaux que nous avons marqués de débogage à l'aide de l'insertion Netlist.

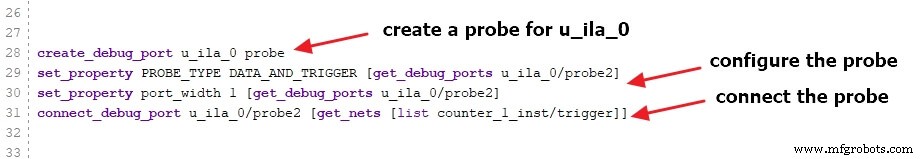

Ensuite, nous voyons la création et la configuration d'un noyau ILA.

Ensuite, nous voyons la création, la configuration et la connexion pour chaque sonde.

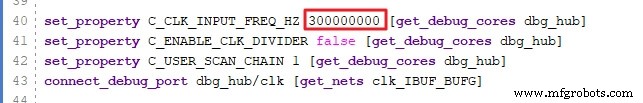

Ensuite, nous voyons la création d'un hub de débogage (dbg_hub ).

Le hub de débogage est responsable de la communication entre Vivado IDE et les cœurs de débogage (ILA et VIO). On voit qu'il définit une fréquence d'horloge (la valeur par défaut est 300 MHz). Vous devez modifier cette horloge pour qu'elle corresponde à votre fréquence d'horloge et enregistrer le fichier.

Remarque : l'horloge connectée à ILA et Debug_hub doit être une horloge autonome.

Maintenant, l'ILA est terminé et enregistré. Nous devons réexécuter la synthèse afin que l'ILA puisse être ajouté à la conception synthétisée.

Cliquez sur Exécuter la synthèse puis sur OK .

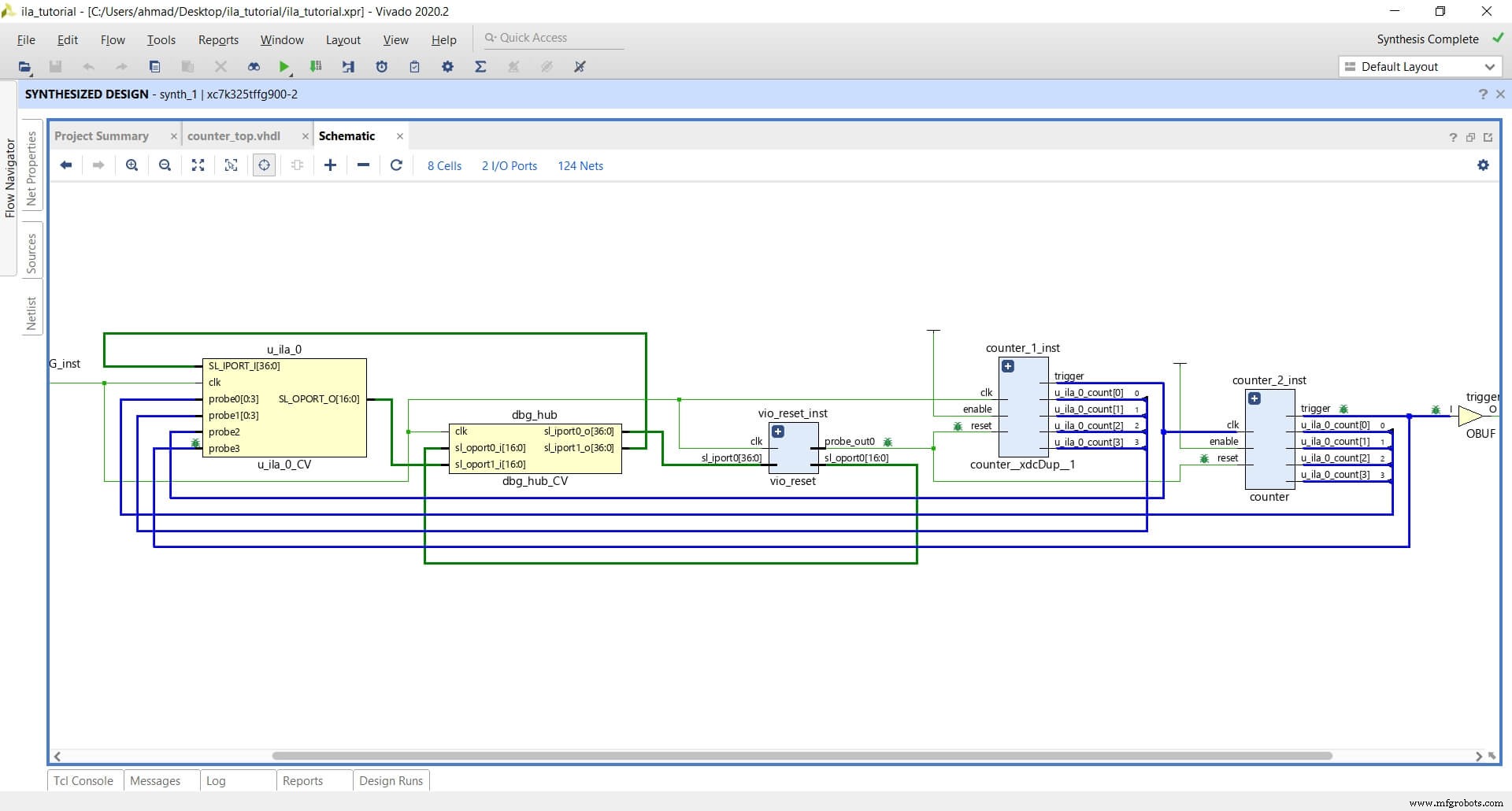

Lorsque Vivado a terminé d'exécuter la synthèse, cliquez sur Ouvrir la conception synthétisée puis sur Schéma .

Nous pouvons voir maintenant que Vivado a ajouté l'ILA et le Debug_Hub à notre conception et a connecté les signaux de débogage aux sondes ILA.

Nous sommes maintenant prêts à mettre en œuvre notre conception et à générer le bitstream afin de pouvoir tester notre conception.

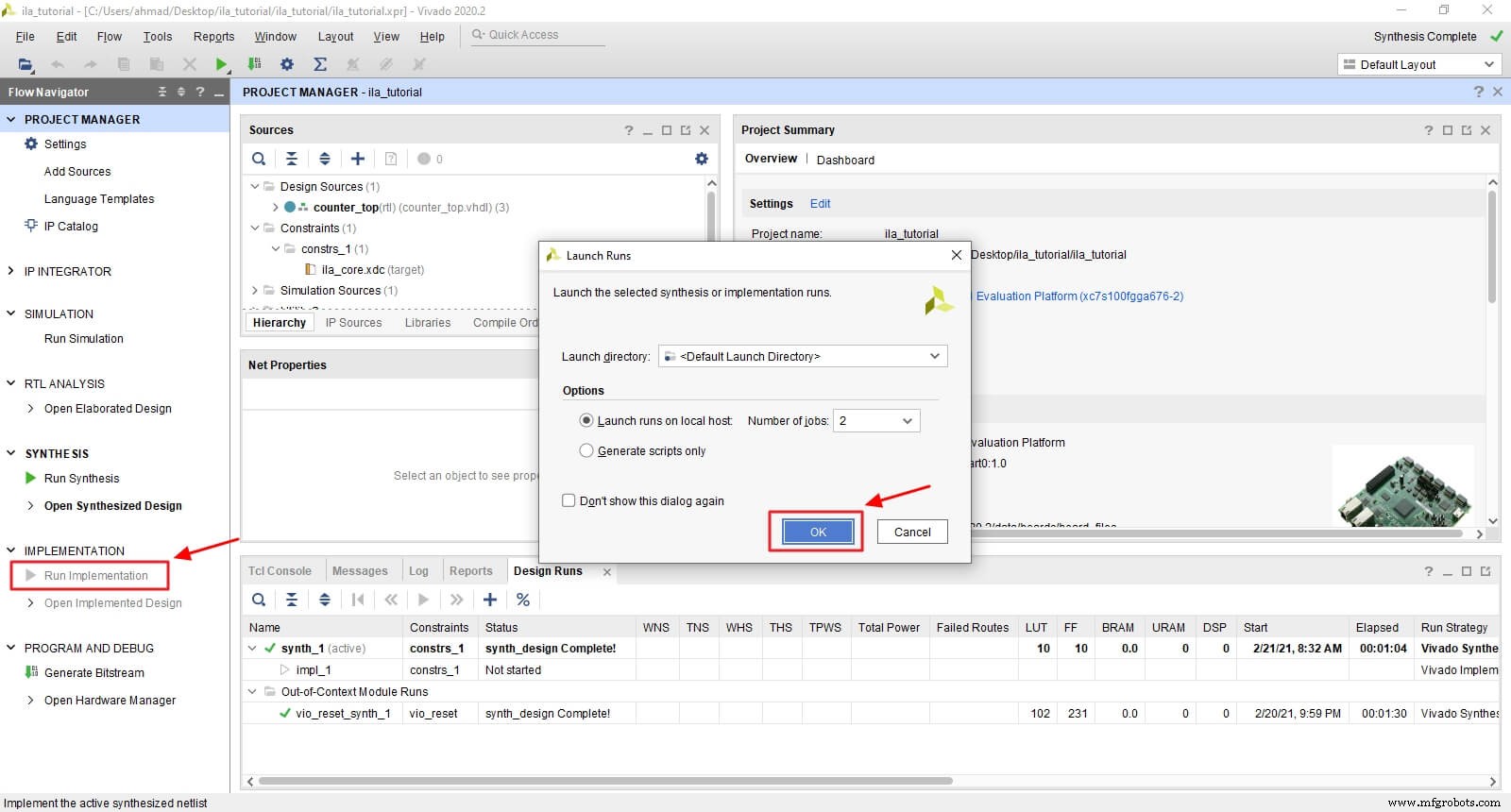

Cliquez sur Exécuter la mise en œuvre puis sur OK .

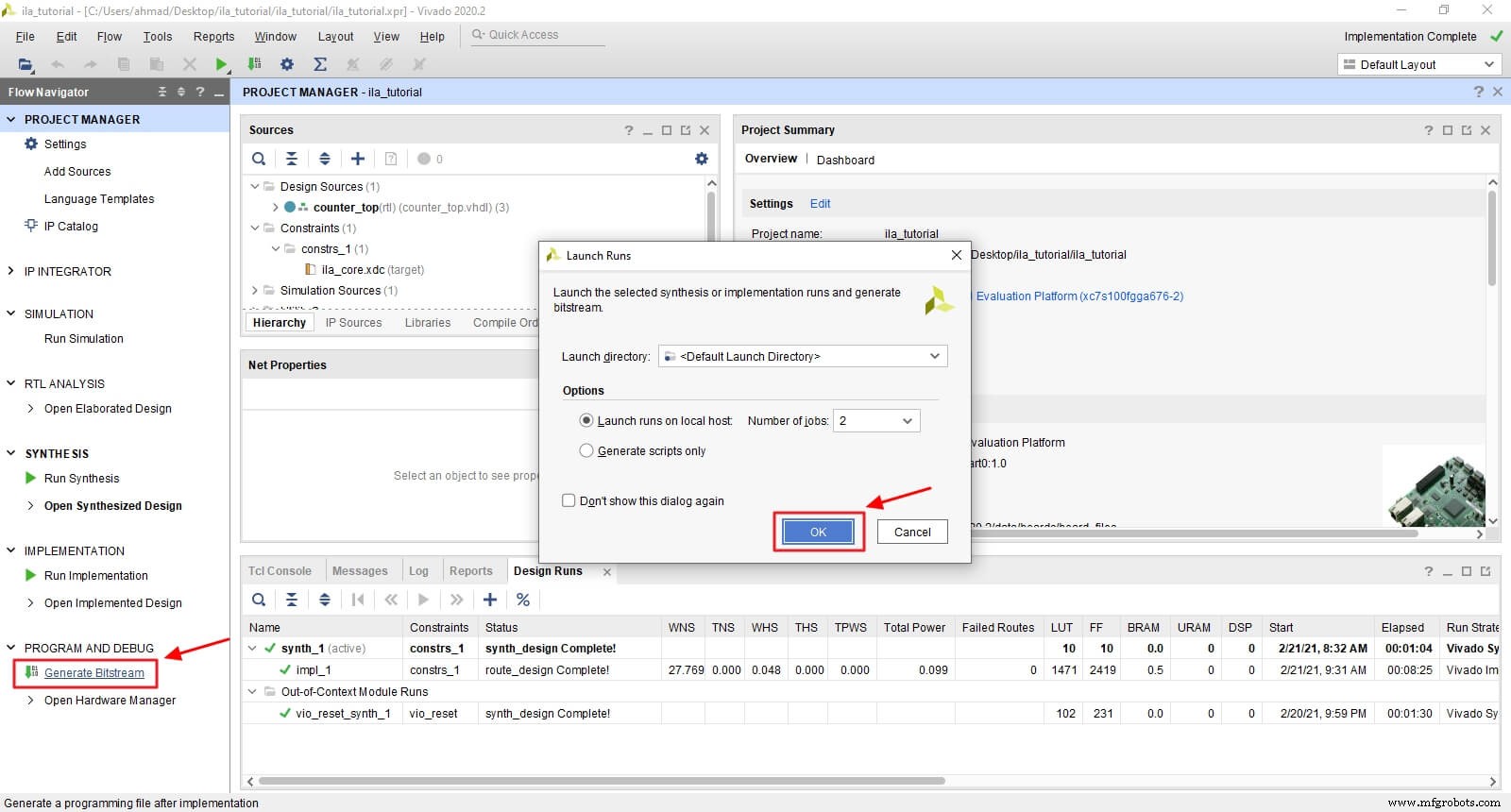

Une fois que Vivado a terminé l'exécution de l'implémentation, cliquez sur Générer Bitstream puis sur OK .

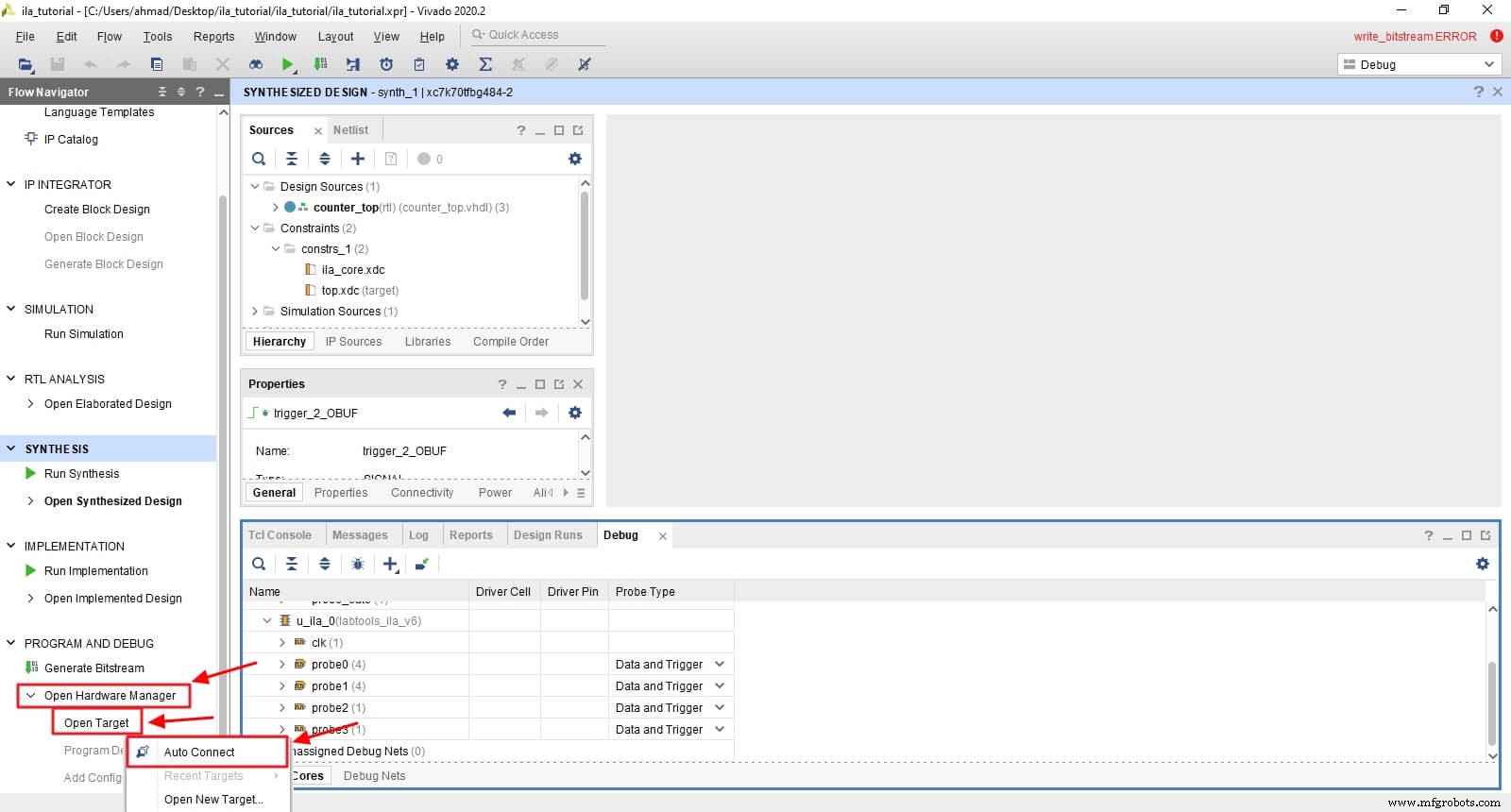

Une fois que Vivado a fini de générer le bitstream, cliquez sur Open Hardware Manager puis sur Open Target, et enfin sur Connexion automatique .

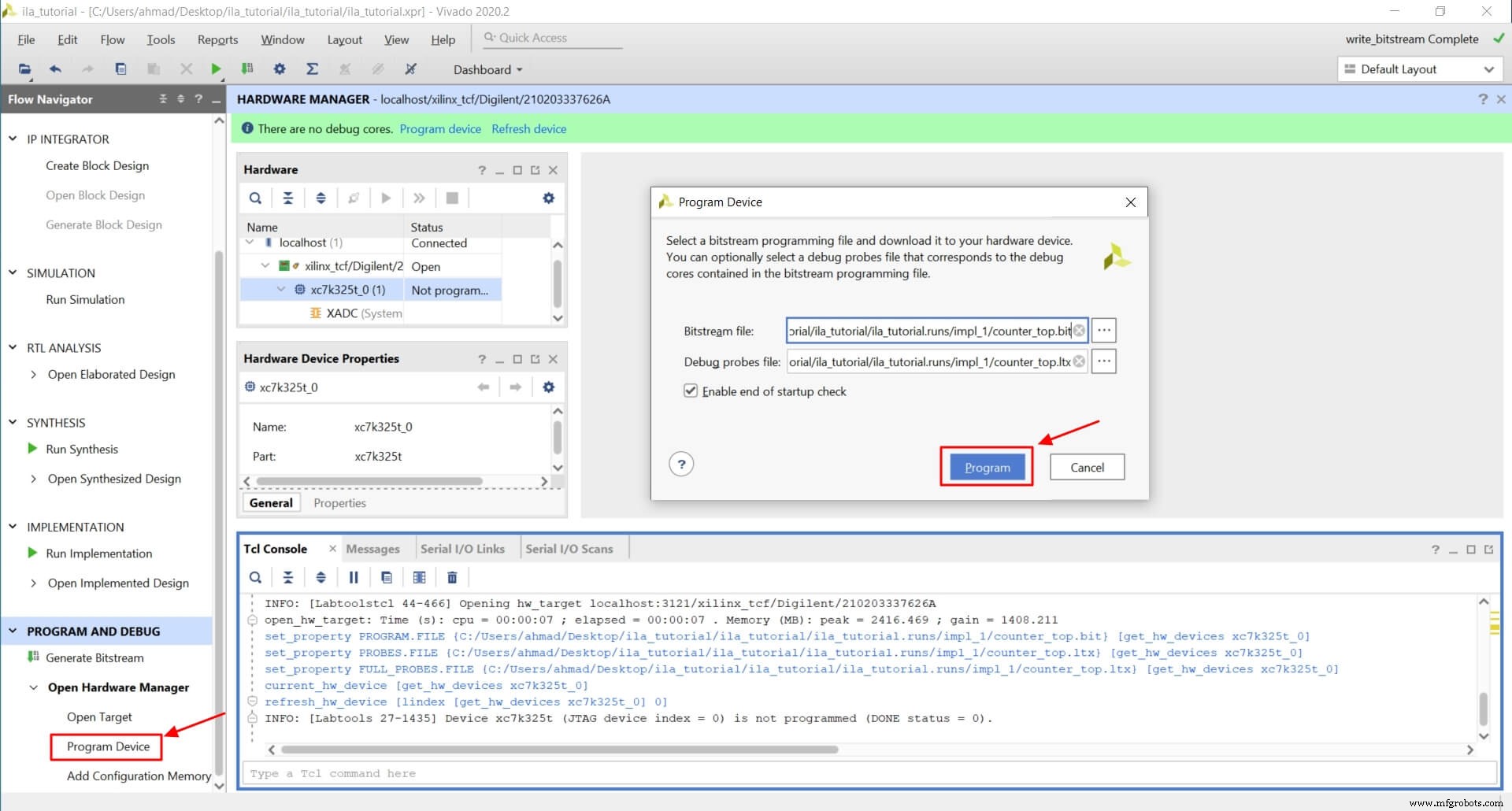

Ensuite, nous devons programmer le FPGA avec le fichier de bits (*.bit) et le fichier de sonde de débogage (*.ltx). Vivado les trouve automatiquement pour vous.

Cliquez sur Programmer l'appareil puis sur Programme .

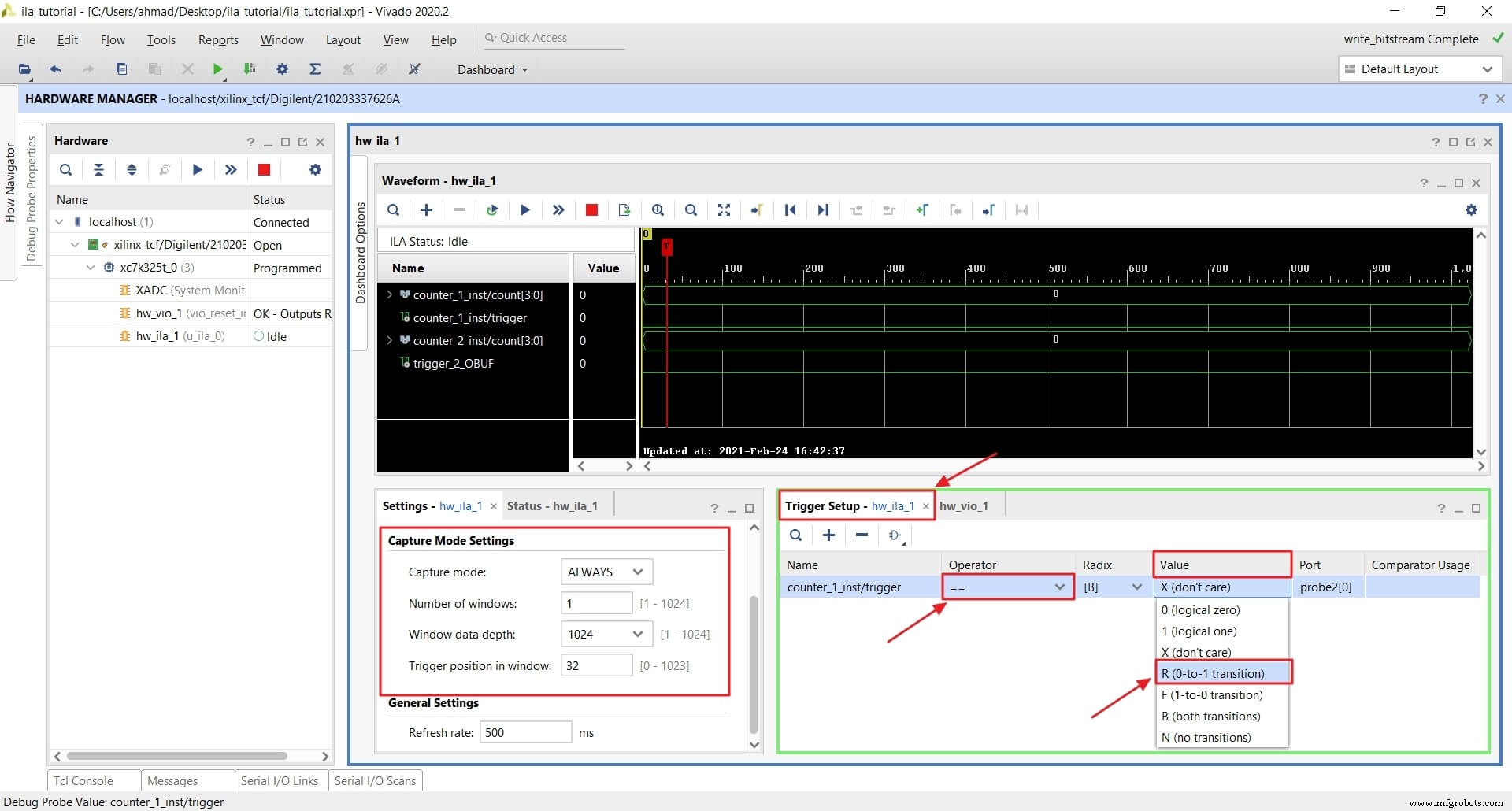

Configuration des déclencheurs ILA

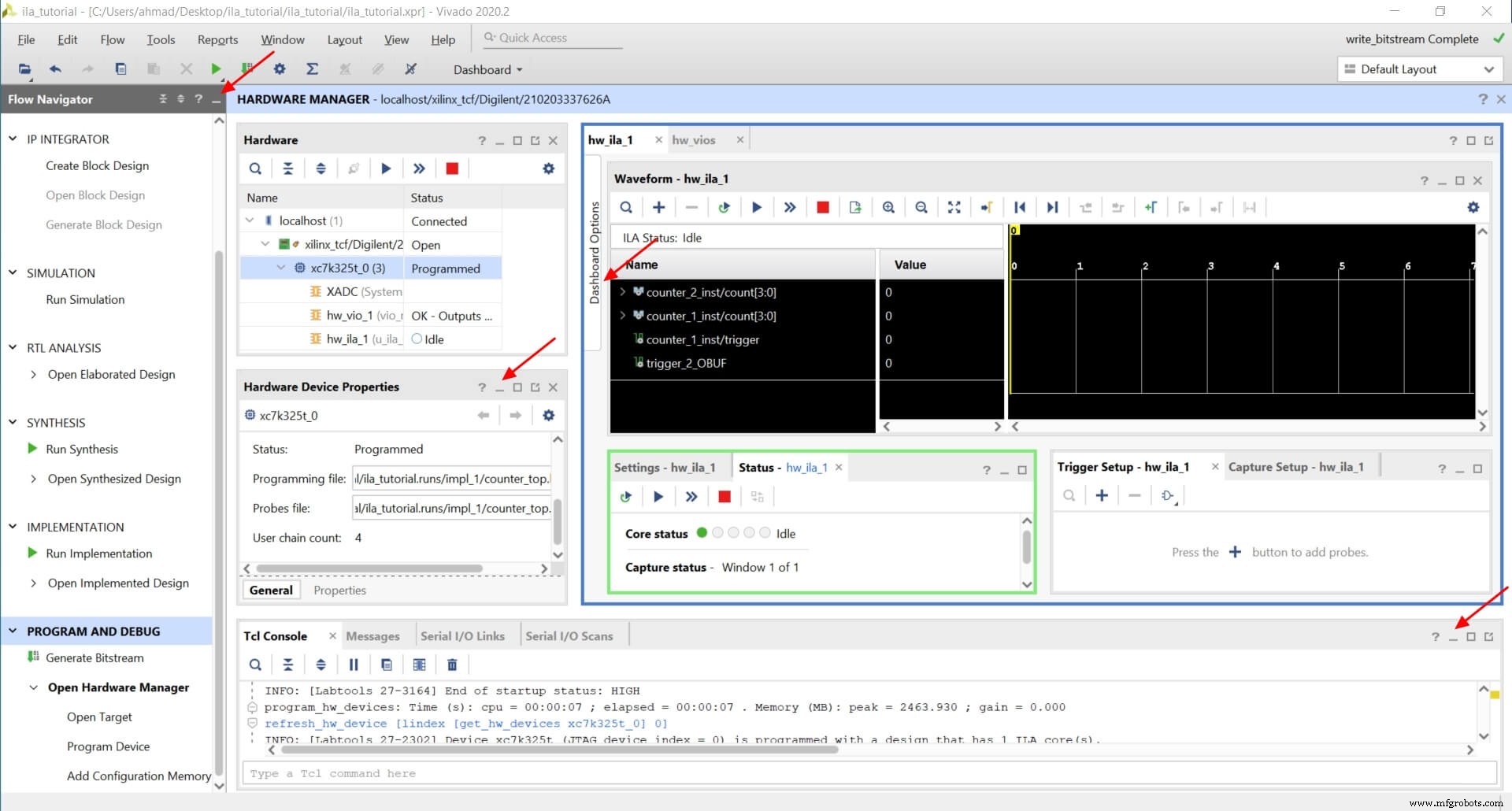

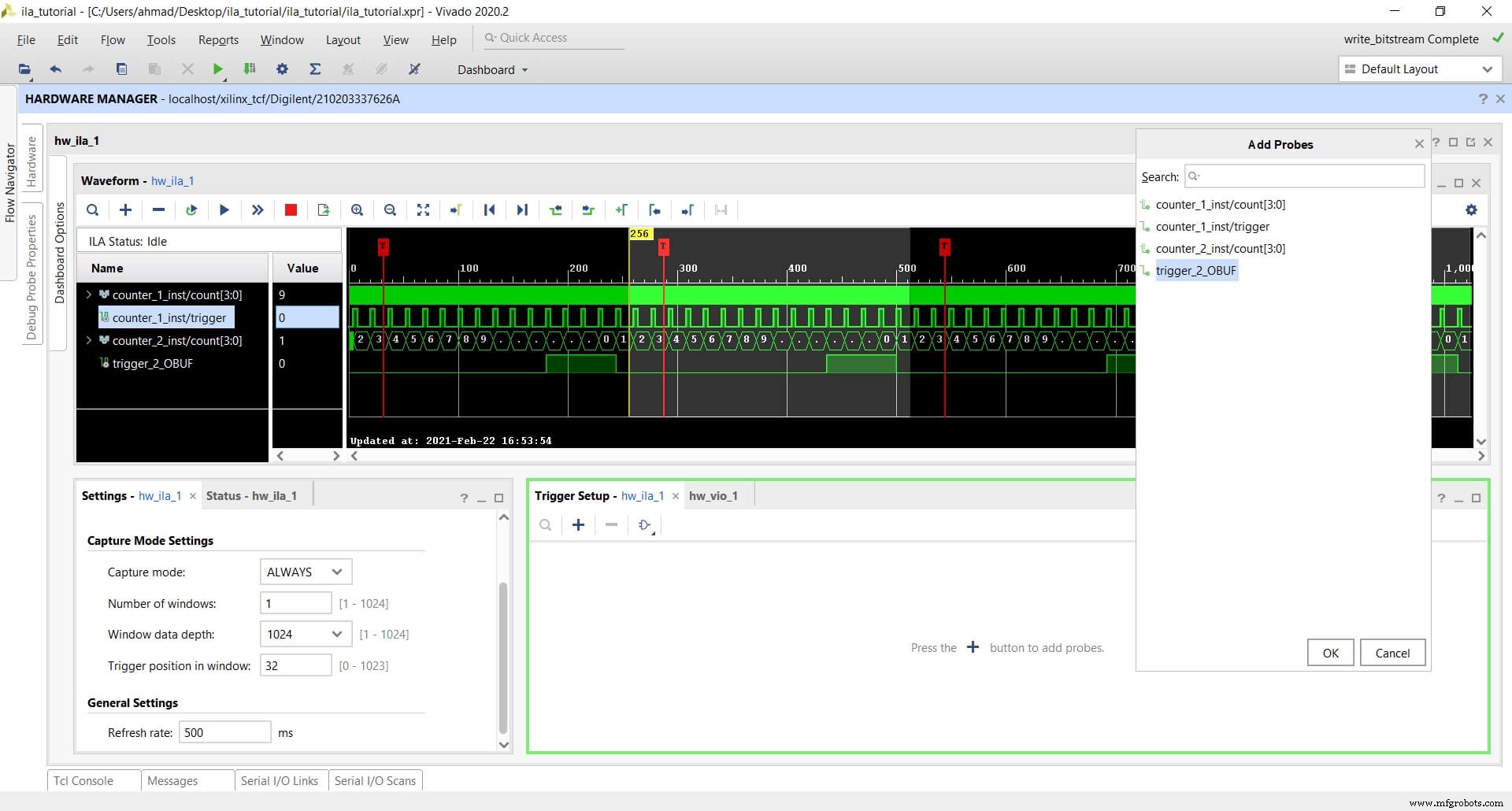

Après avoir programmé l'appareil, nous pouvons voir que la disposition de l'interface graphique de Vivado a changé, et un nouveau hw_ila_1 tableau de bord s'est ouvert, contenant plusieurs fenêtres.

Nous allons minimiser certaines fenêtres dont nous n'avons pas besoin pour pouvoir travailler confortablement.

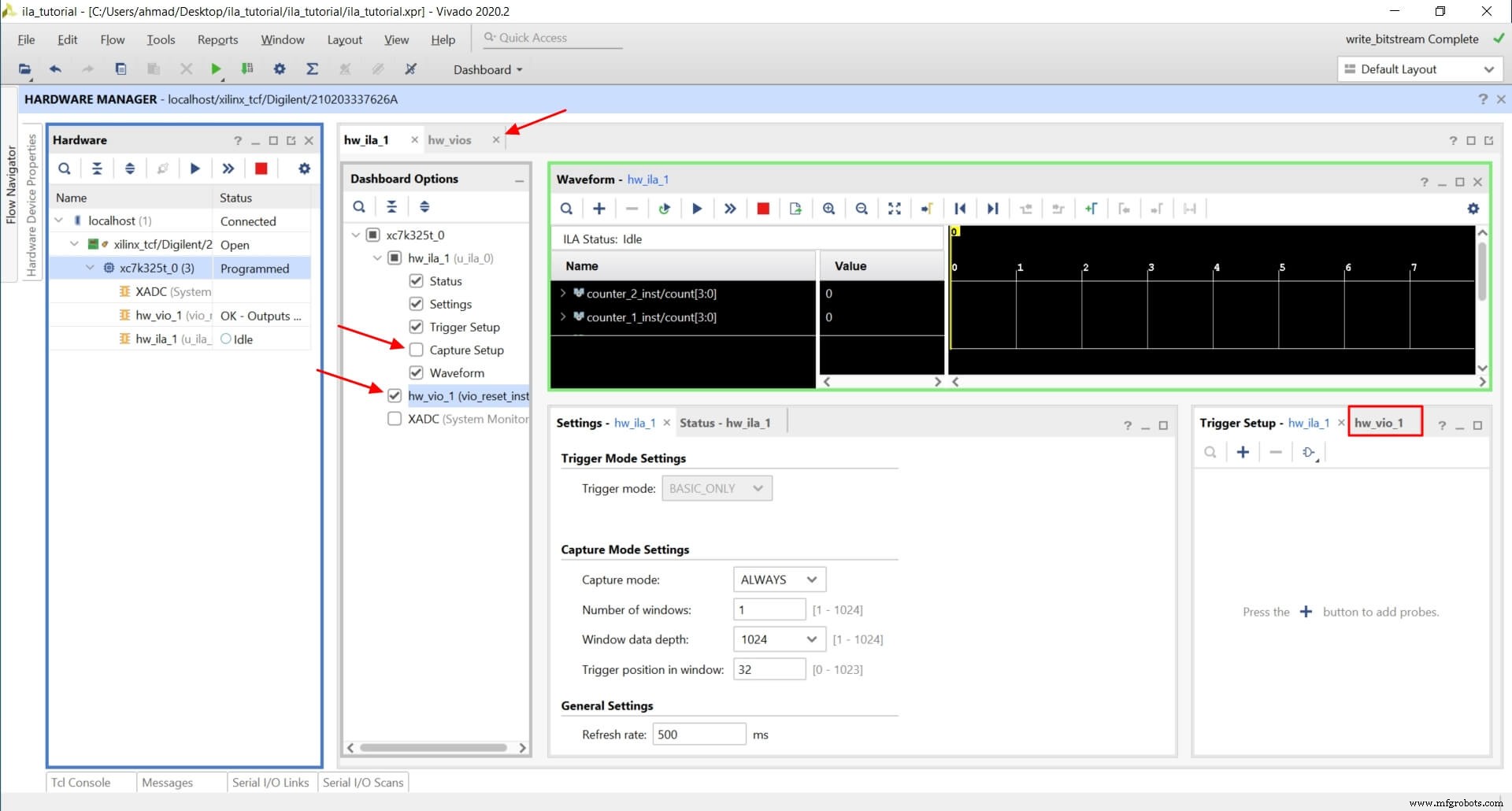

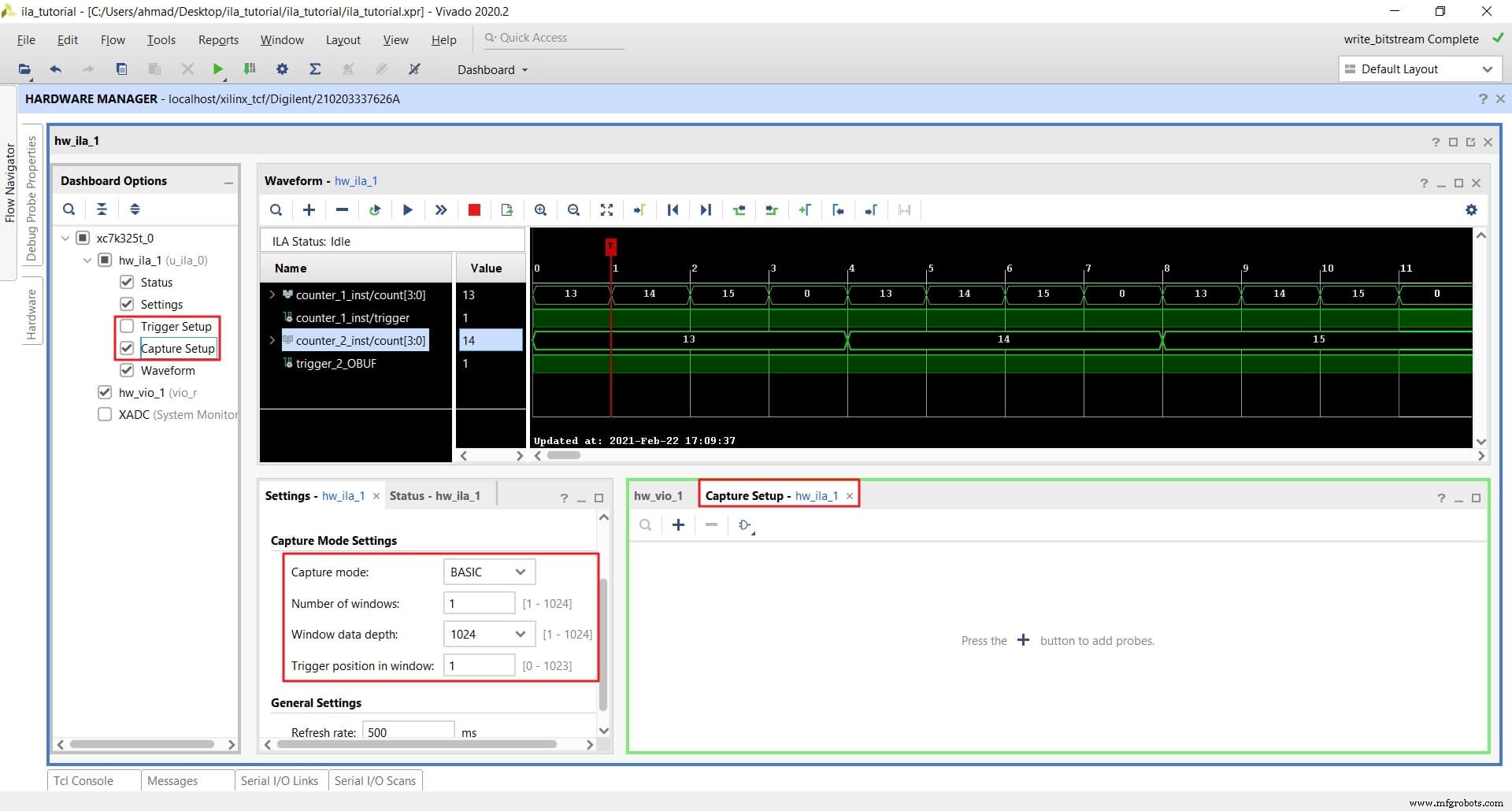

Dans les options du tableau de bord, cochez hw_vio_1 et décochez Configuration de la capture .

Fermez également le hw_vios car lorsque nous avons coché hw_vio_1 , il a été ajouté à la configuration du déclencheur fenêtre.

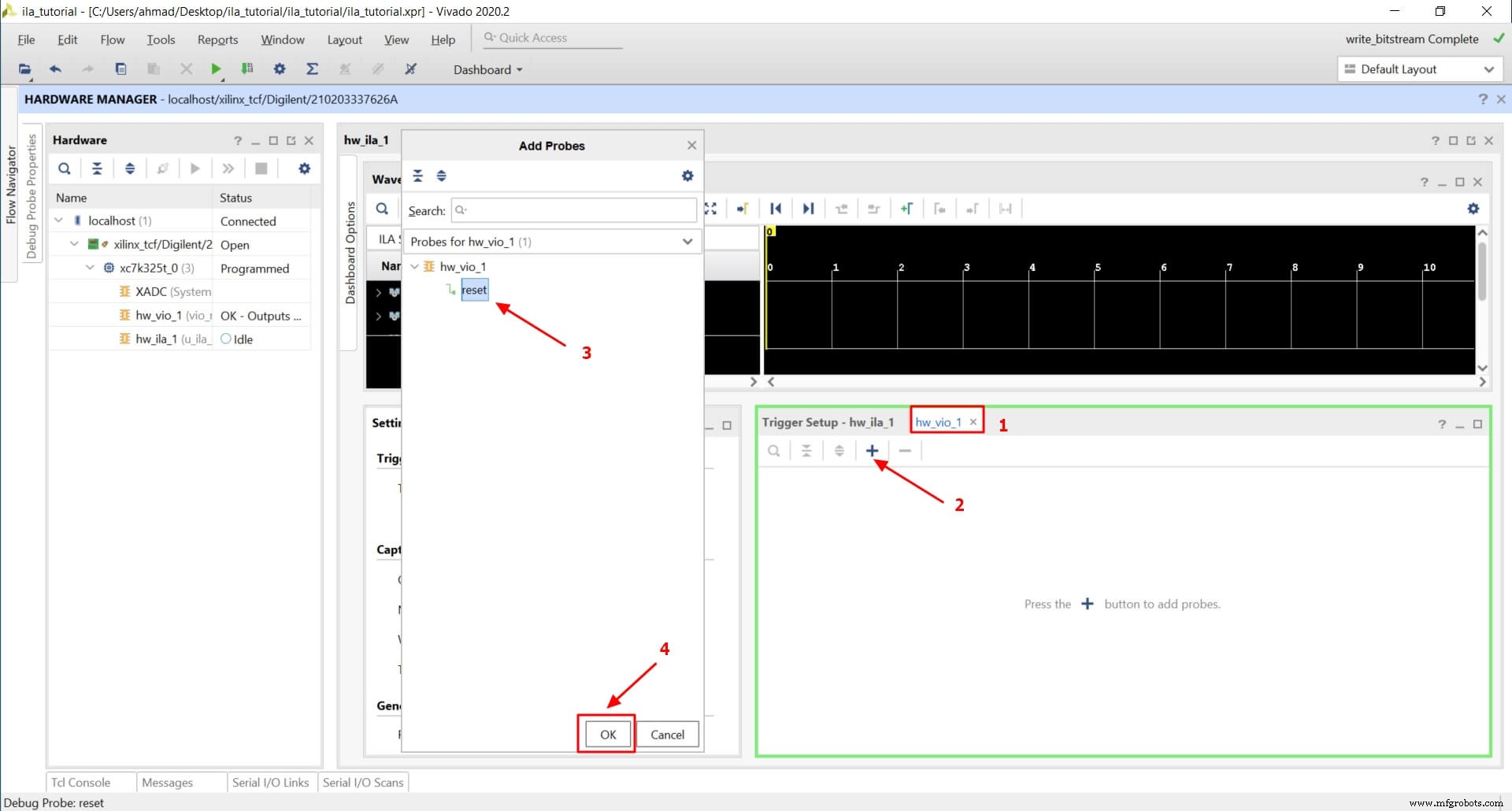

Maintenant, nous devons ajouter la réinitialisation bouton au VIO afin que nous puissions contrôler la réinitialisation .

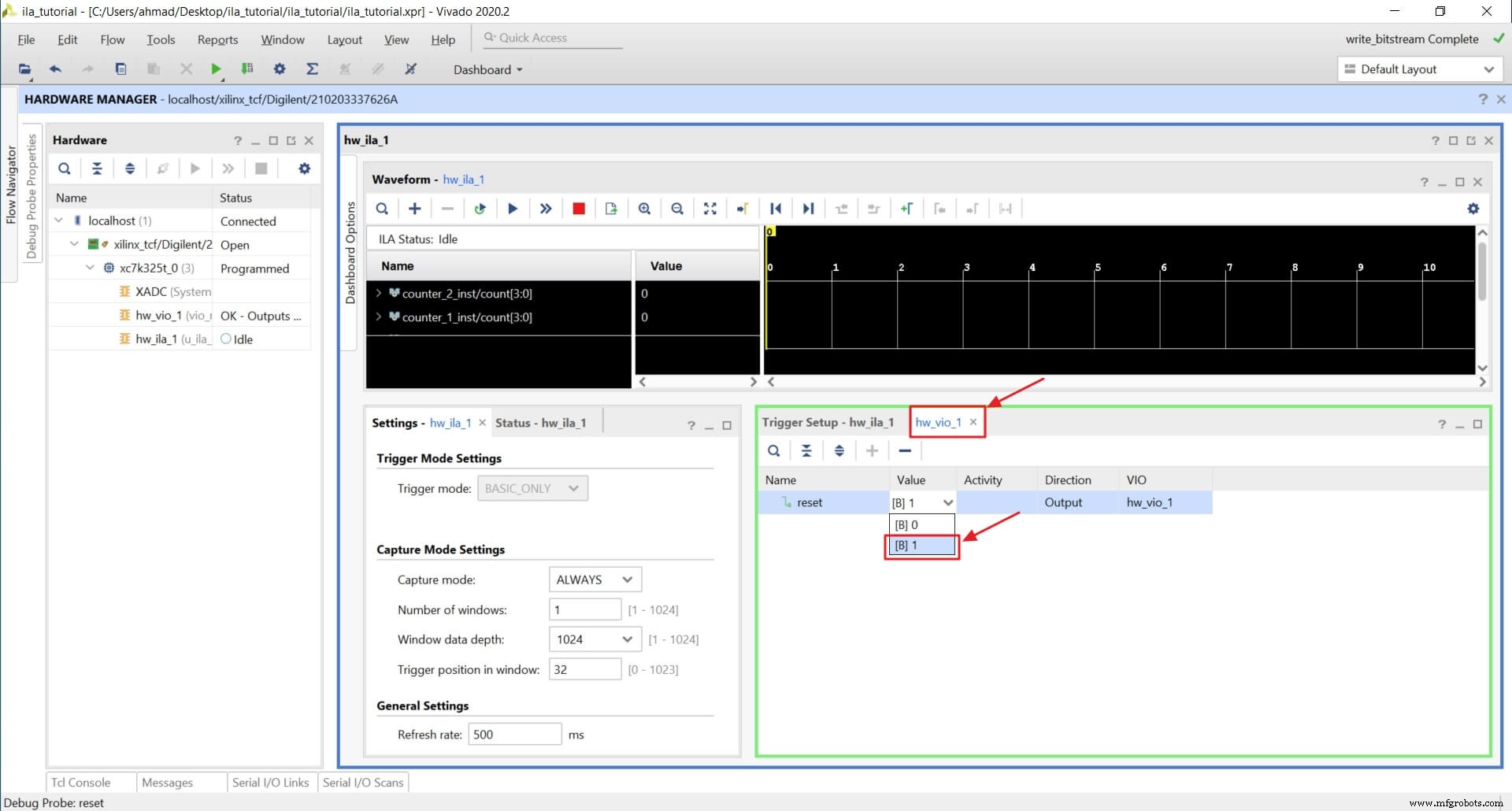

Cliquez sur hw_vio_1 puis ajoutez réinitialiser comme indiqué dans l'image ci-dessous.

Nous pouvons voir que hw_vio_1 contient maintenant la réinitialisation sonde.

Modifier la valeur de la réinitialisation dans vio_reset à 1 si ce n'est pas 1.

Maintenant, nous allons ajouter les déclencheurs que nous utiliserons. Un changement de valeur sur un signal de déclenchement entraînera l'ILA pour commencer à enregistrer les signaux sondés.

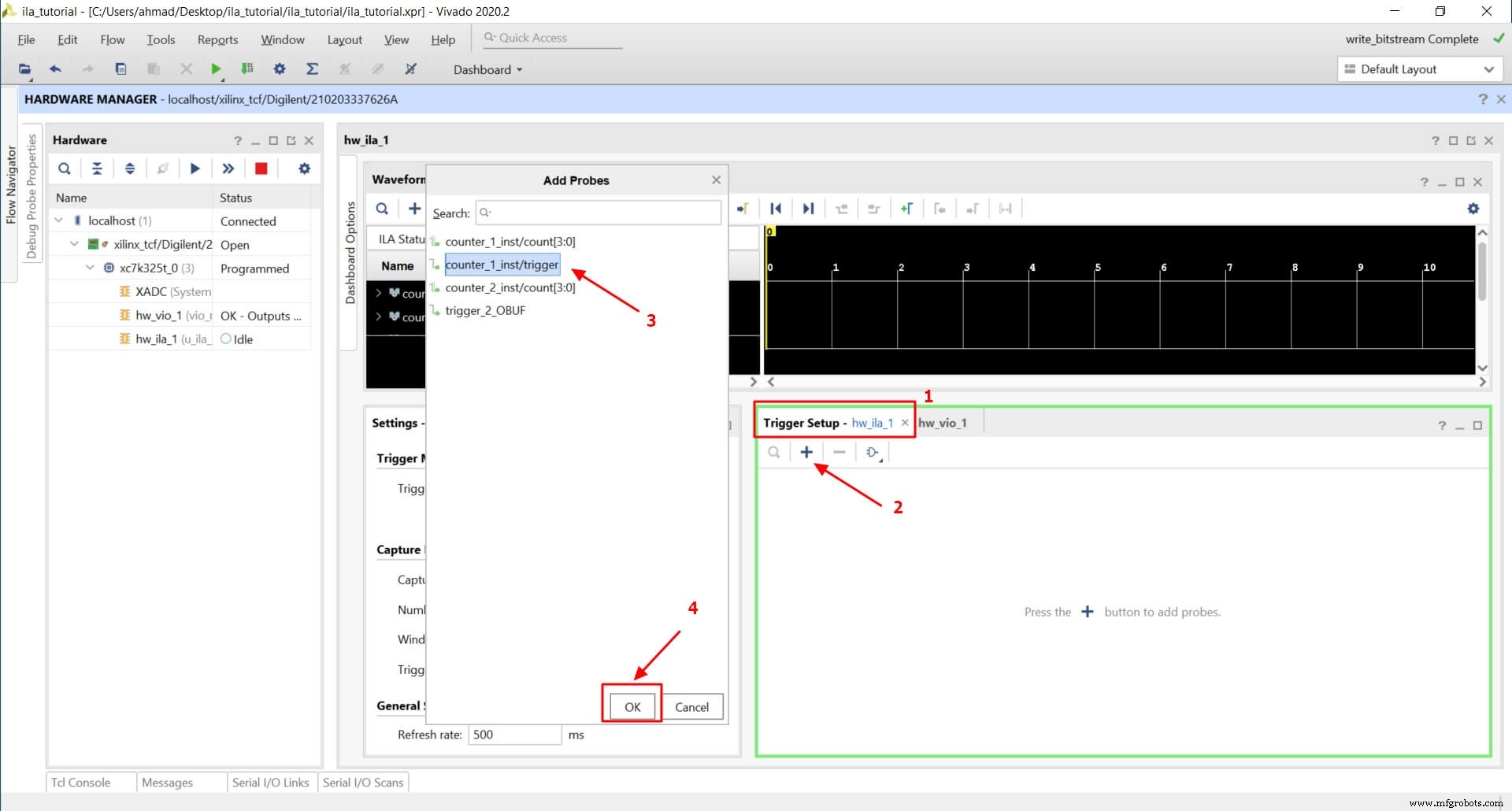

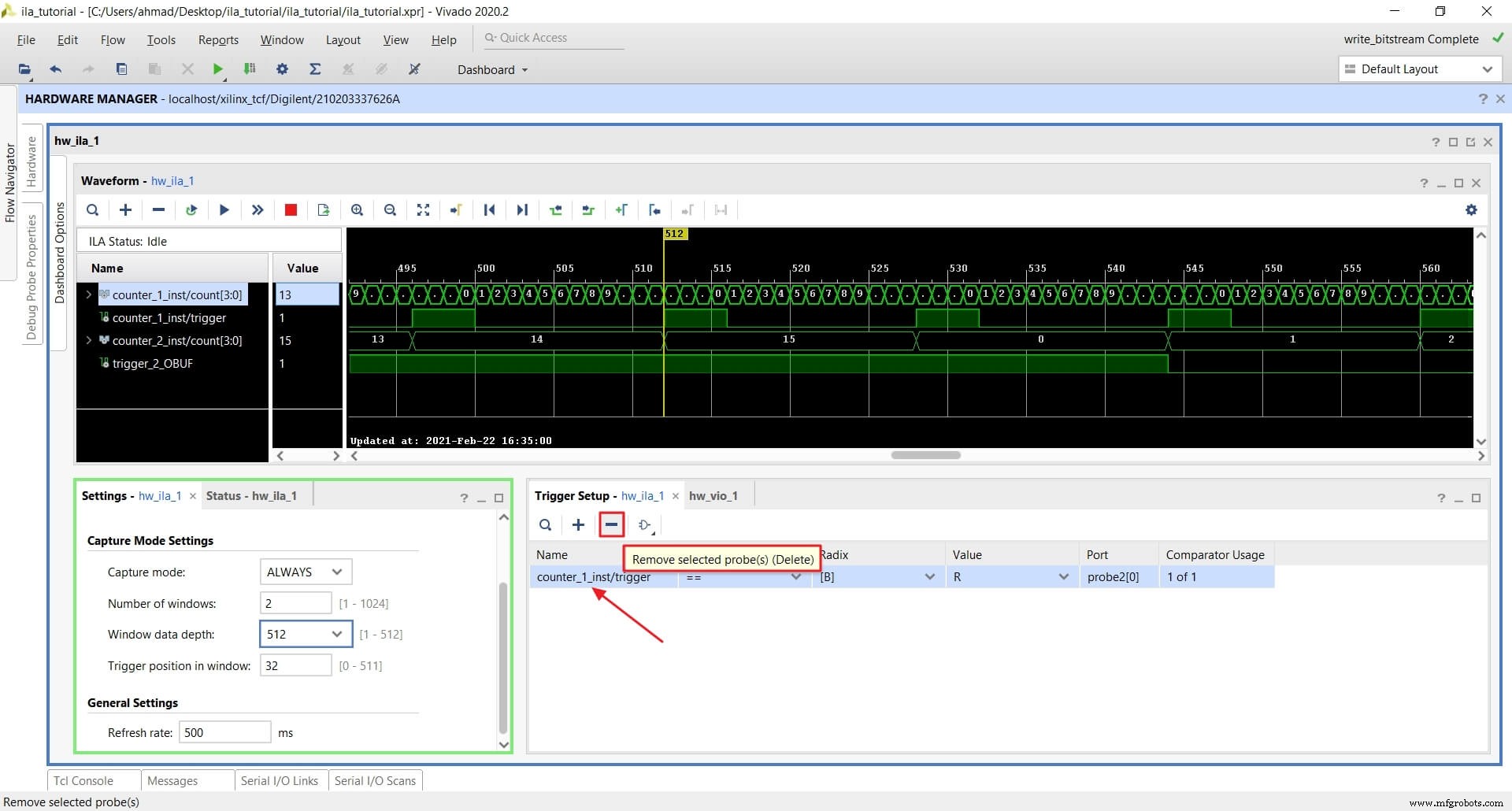

Disons que nous voulons déclencher (démarrer l'enregistrement) sur le front montant du port de sortie trigger de counter_1_inst . Pour ce faire, suivez ces étapes :

- Accédez à Configuration du déclencheur - hw_ila_1 fenêtre

- Cliquez sur le + icône pour ajouter un nouveau déclencheur et choisissez counter_1_inst/trigger et cliquez sur OK.

- Nous pouvons voir que le déclencheur a été ajouté, et maintenant nous devons configurer la condition. Cliquez sur la case Valeur et choisissez R(transition de 0 à 1) . Cliquez sur la case Opérateur et choisissez ==(égal)

Nous allons également changer la position de déclenchement à 32, ce qui signifie qu'il enregistrera 32 échantillons avant l'événement de déclenchement en plus de ce qui vient après.

Maintenant, le déclencheur est configuré et prêt à être armé.

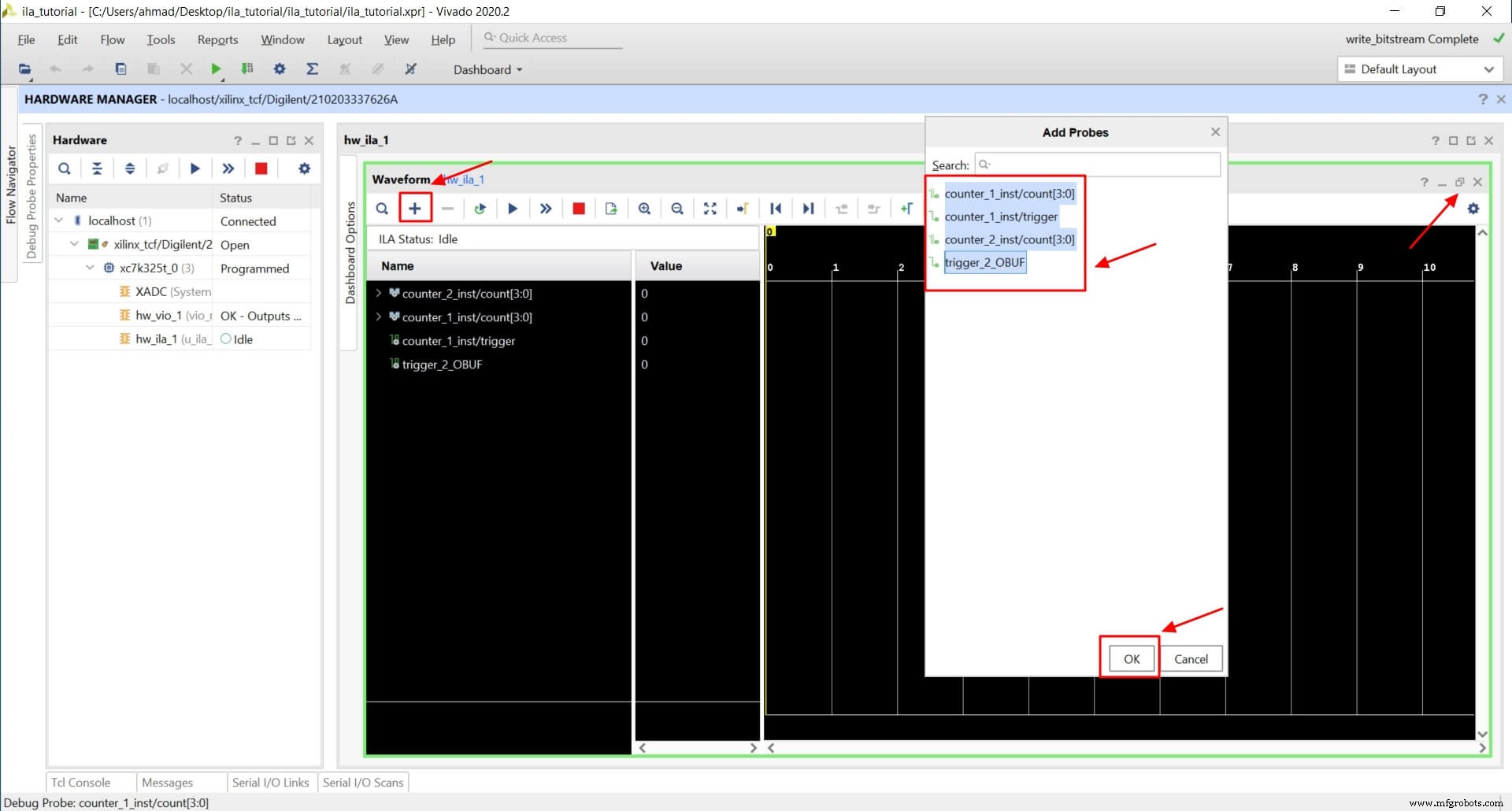

Passons maintenant à la fenêtre de forme d'onde pour ajouter les signaux que nous voulons voir. Tout d'abord, maximisons la fenêtre intérieure pour obtenir une meilleure vue.

Deuxièmement, nous devons ajouter des signaux manquants à la sonde. Vivado ajoute généralement tous les signaux attribués automatiquement, mais dans ce cas, ce n'est pas le cas.

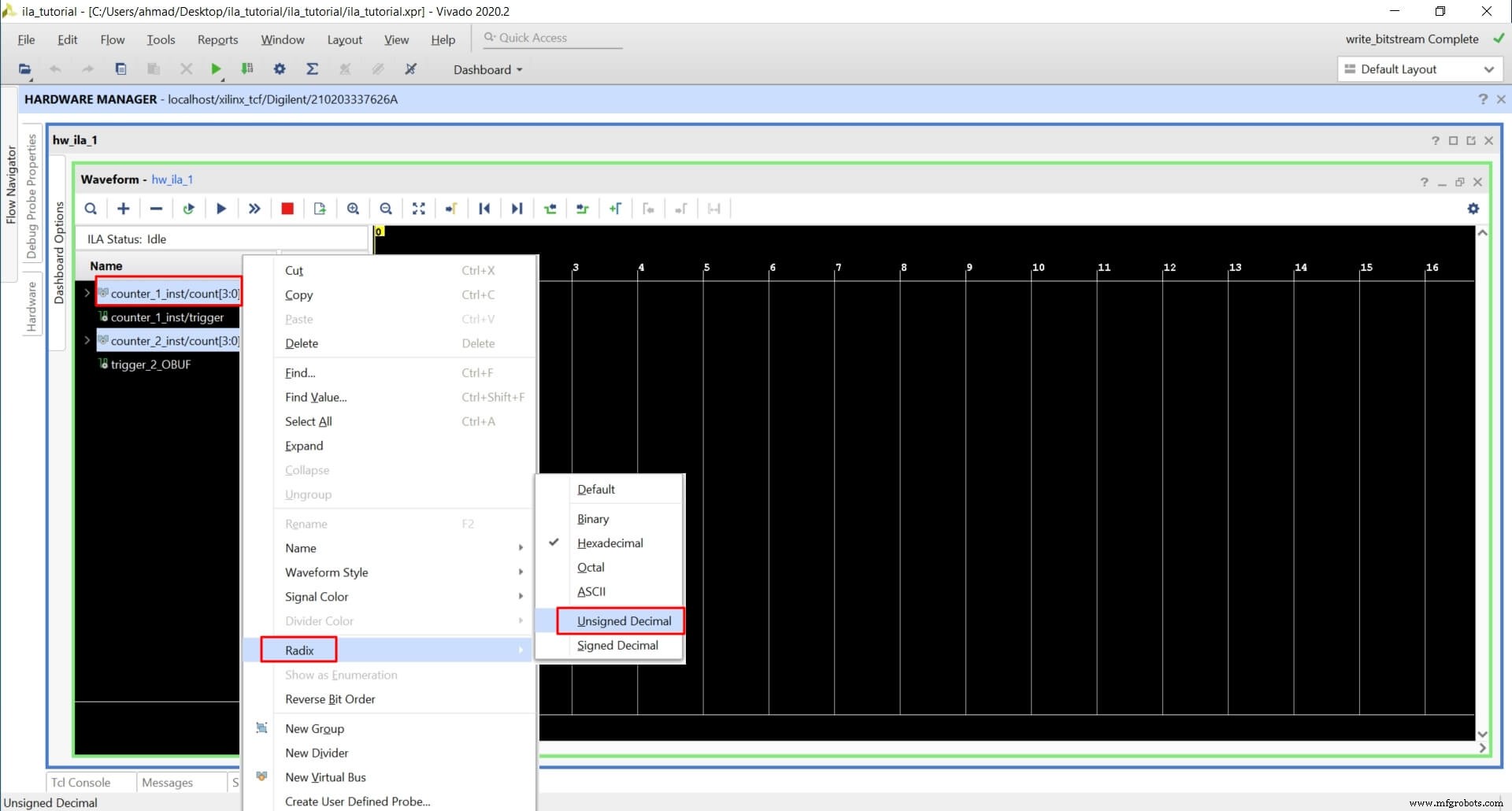

Maintenant, nous changeons la base du compte signaler à Non signé car il est plus facile à suivre.

Faites un clic droit sur le compte nom du signal, puis choisissez radix puis Non signé .

Exécution de l'ILA et du VIO

Maintenant, nous avons terminé la configuration et la personnalisation de l'ILA, et nous sommes prêts à l'exécuter.

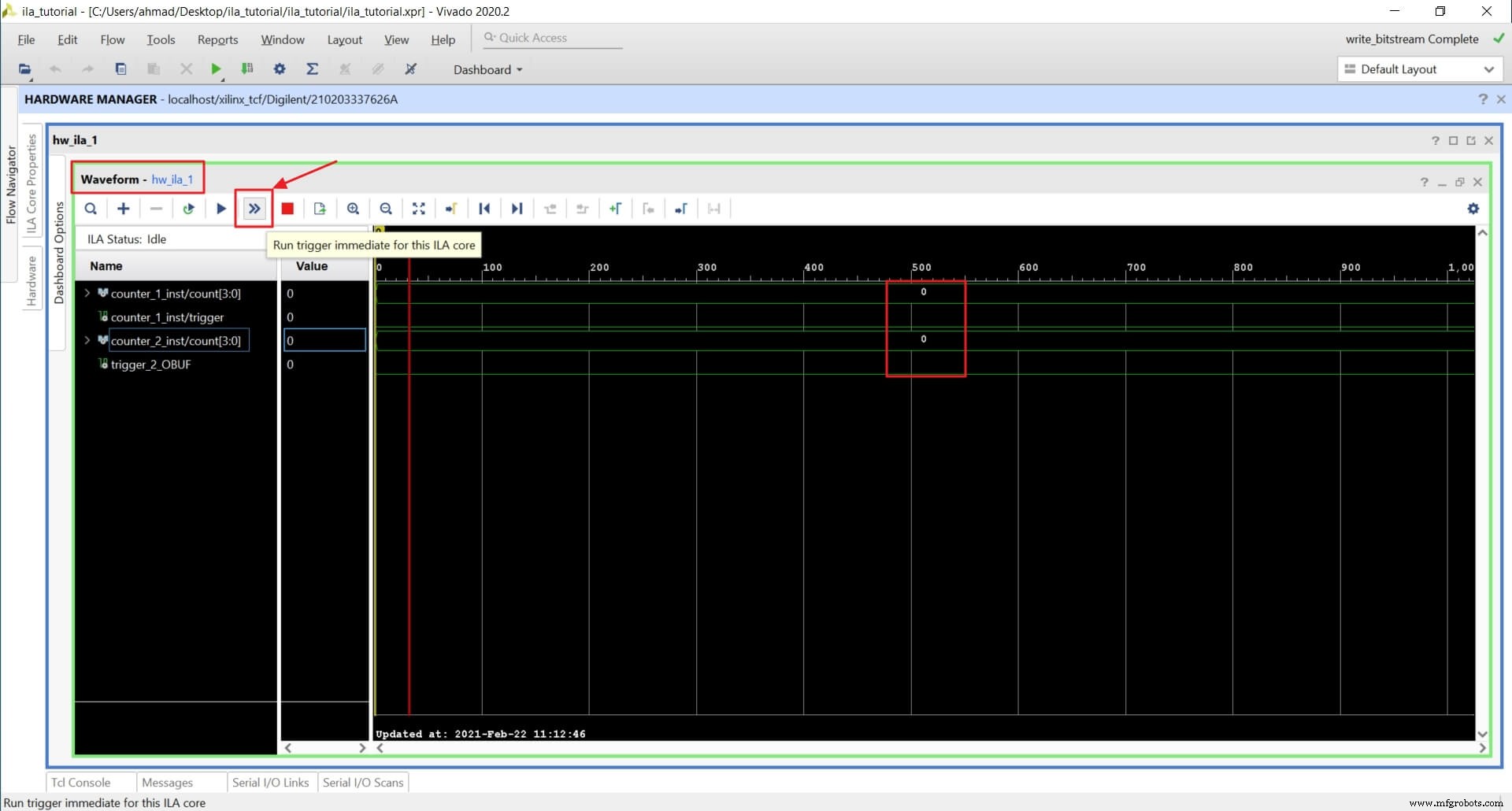

ILA a deux modes d'exécution :Immédiat et déclencheur .

Mode immédiat

Le mode immédiat déclenche immédiatement l'ILA et commence à enregistrer les échantillons directement jusqu'à ce que le FIFO soit plein.

Cliquez sur Exécuter le déclencheur immédiatement bouton.

Nous pouvons maintenant voir les échantillons enregistrés dans la fenêtre de forme d'onde. Nous voyons que les deux comptent les signaux sont 0, et les deux déclenchent les signaux sont bas '0' car la réinitialisation est actif.

Mode de déclenchement

Le mode déclencheur nécessite que nous définissions une condition pour au moins un déclencheur et que nous l'armions. L'ILA continuera d'attendre que la condition du déclencheur armé devienne vraie, puis il commencera à enregistrer les échantillons directement jusqu'à ce que le FIFO soit plein.

Nous avons déjà ajouté le déclencheur et l'avons configuré sur R (transition de 0 à 1) .

Exécuter ILA avec un déclencheur

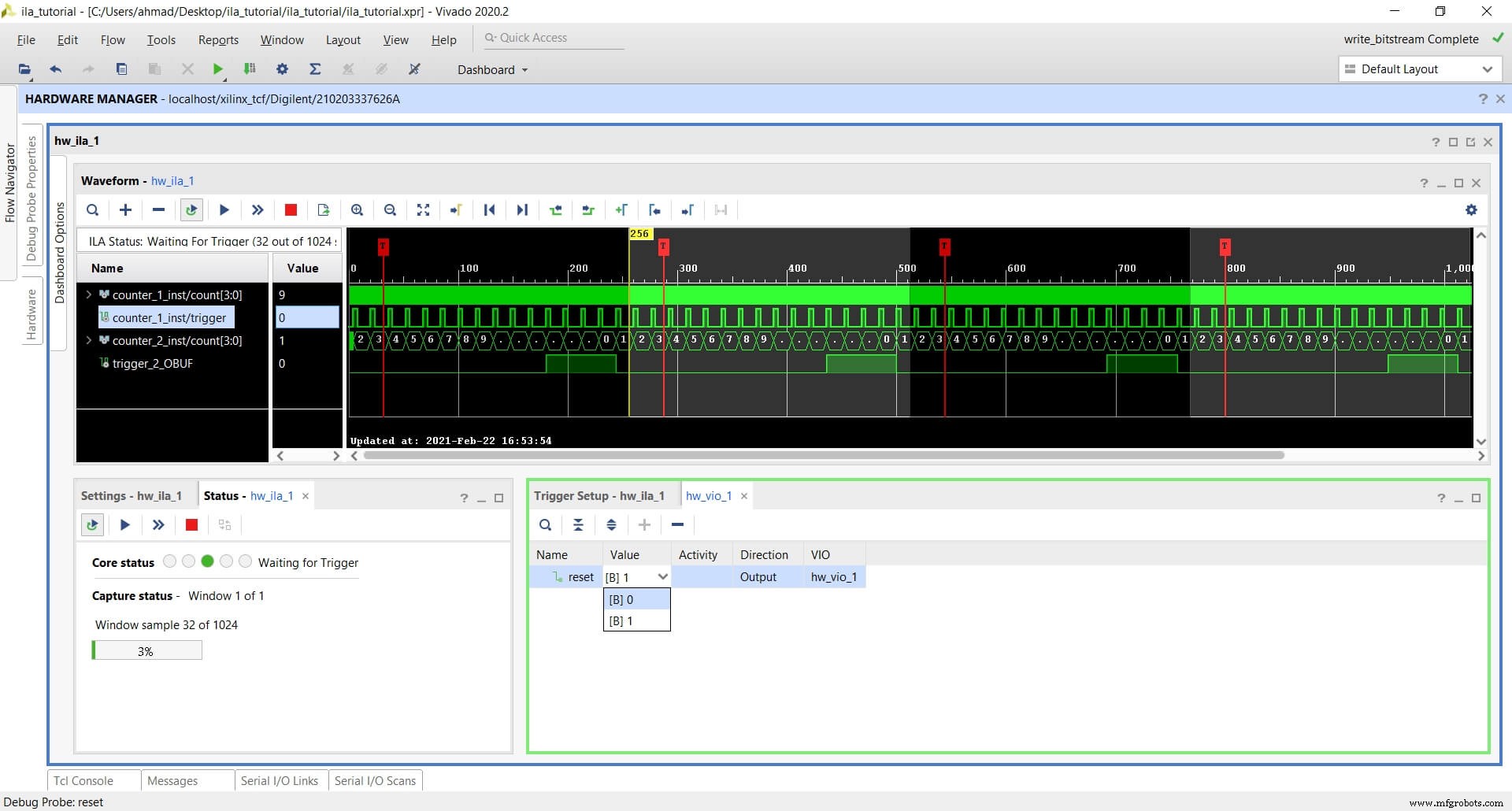

Modifier réinitialiser retour à 1 depuis vio_reset .

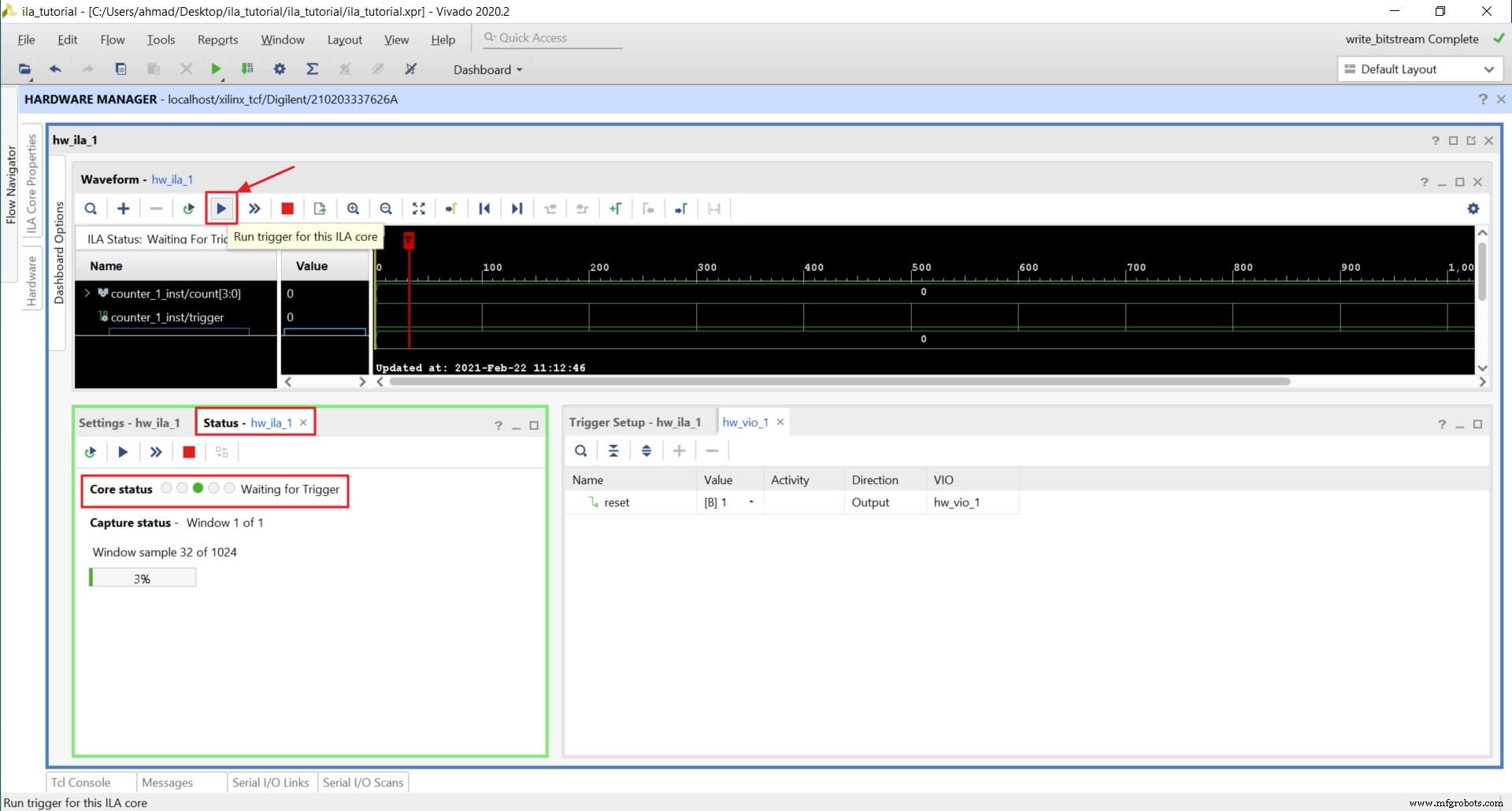

Cliquez sur la fenêtre Statut hw_ila_1 . Nous voyons que l'état du noyau est Idle car il n'y a pas de déclencheurs armés. Cliquez sur le déclencheur Exécuter bouton, et cela armera la gâchette.

Nous voyons maintenant que le statut du noyau est passé à en attente de déclencheur . Comme la réinitialisation est élevé, il n'y a aucune activité sur notre signal de déclenchement (port trigger de counter_1_inst ), et ILA attend.

Maintenant, changeons le reset à 0 pour que les compteurs commencent à fonctionner.

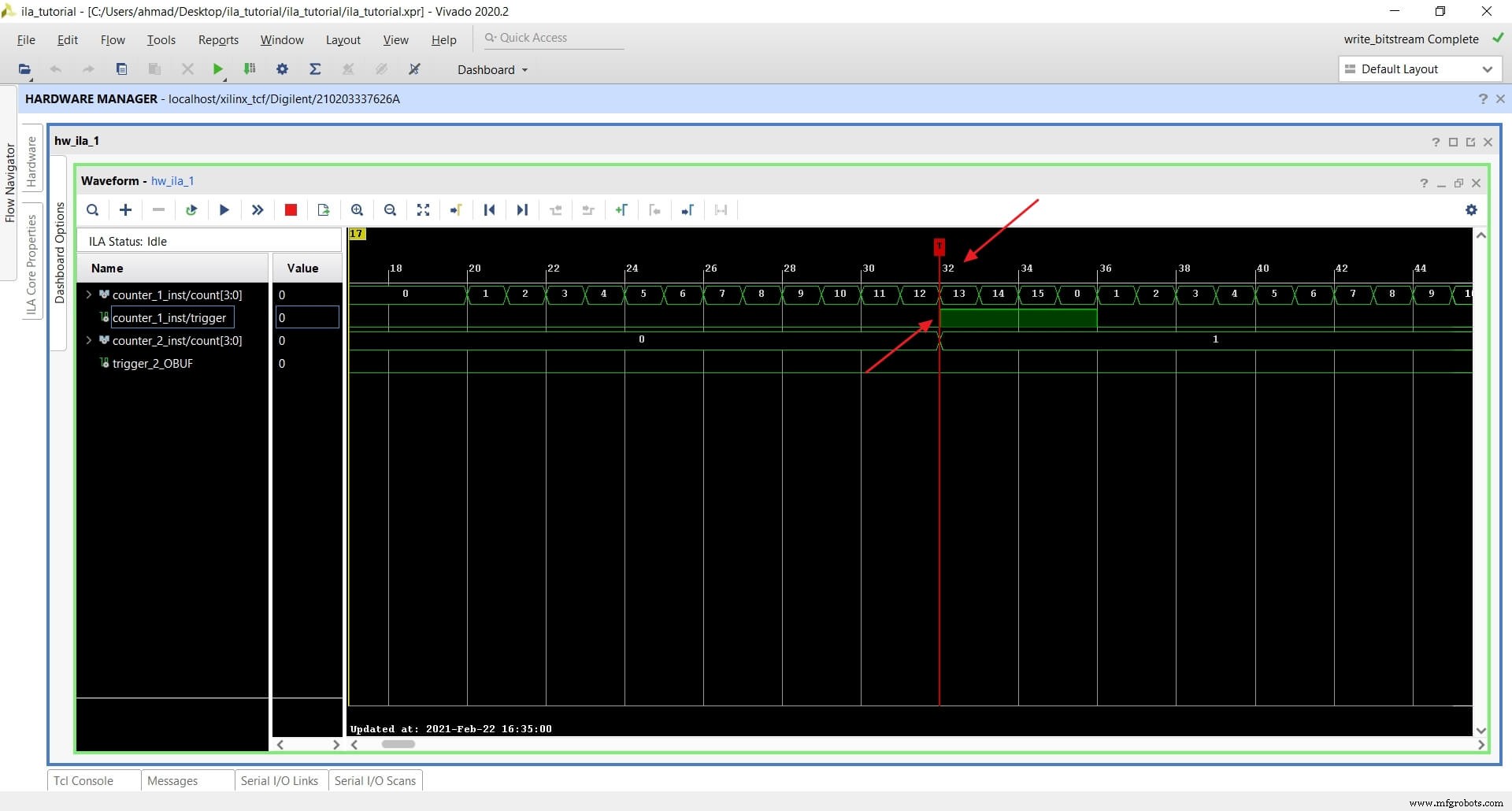

Nous voyons maintenant que l'ILA s'est déclenchée et a enregistré les échantillons, et l'état du cœur est redevenu Idle .

Nous voyons la ligne verticale rouge (marqueur) sur le front montant de notre signal de déclenchement (port trigger de counter_1_inst ), et il est en position 32 . Nous pouvons également vérifier que le signal compte se comporte correctement et le signal counter_1_inst/trigger est haut pendant quatre cycles d'horloge entre 12 et 15 (la sortie est retardée d'un cycle d'horloge).

Si nous dézoomons un peu, nous pouvons également vérifier le comportement de count et déclencheur signaux pour counter_2_inst .

Exécuter ILA avec plusieurs déclencheurs

Nous pouvons utiliser une combinaison de déclencheurs pour des conditions complexes ou avancées. Pour capturer plusieurs périodes disjointes dans la même forme d'onde, nous pouvons utiliser plusieurs déclencheurs qui se déclenchent à plusieurs reprises.

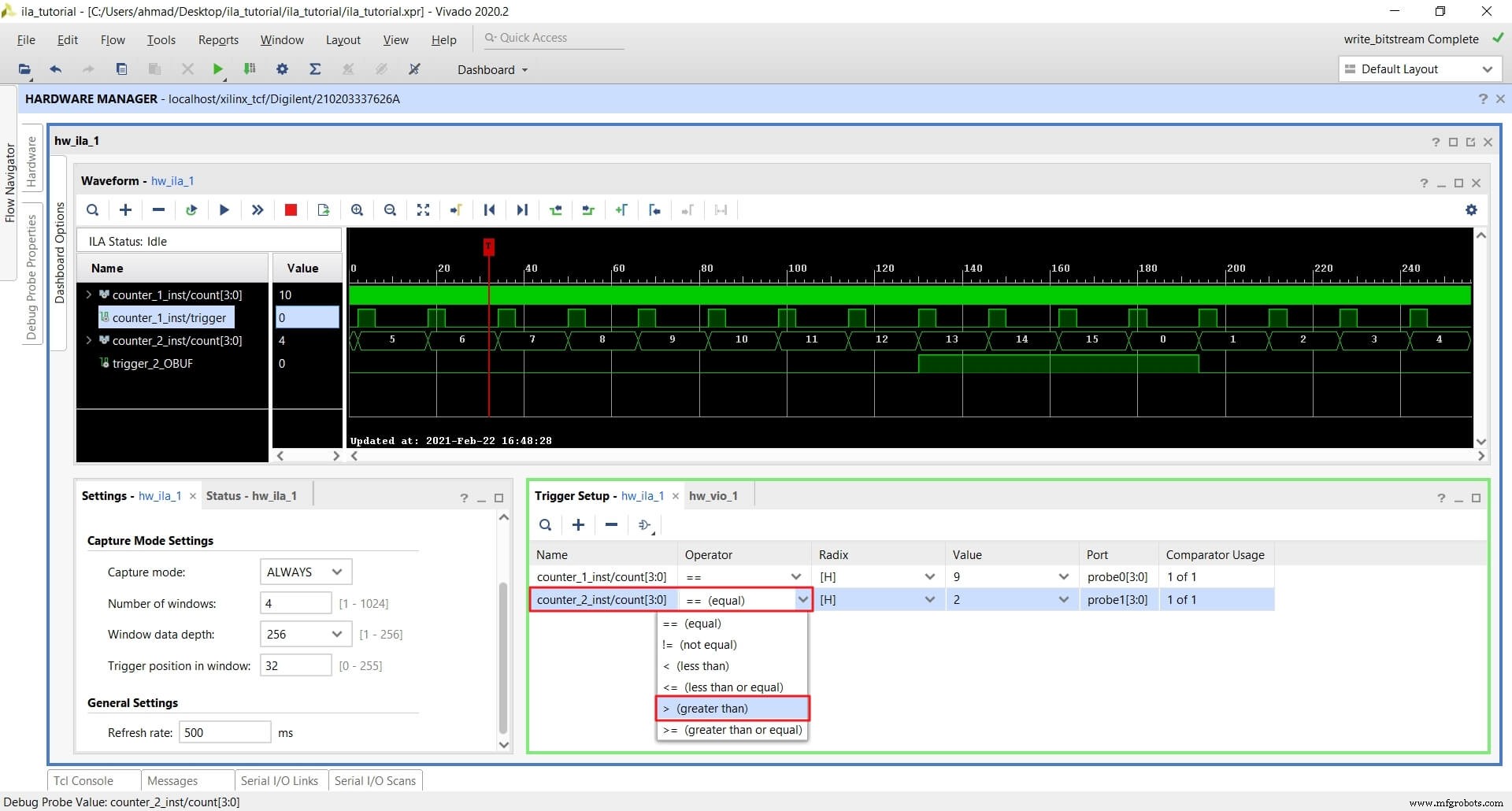

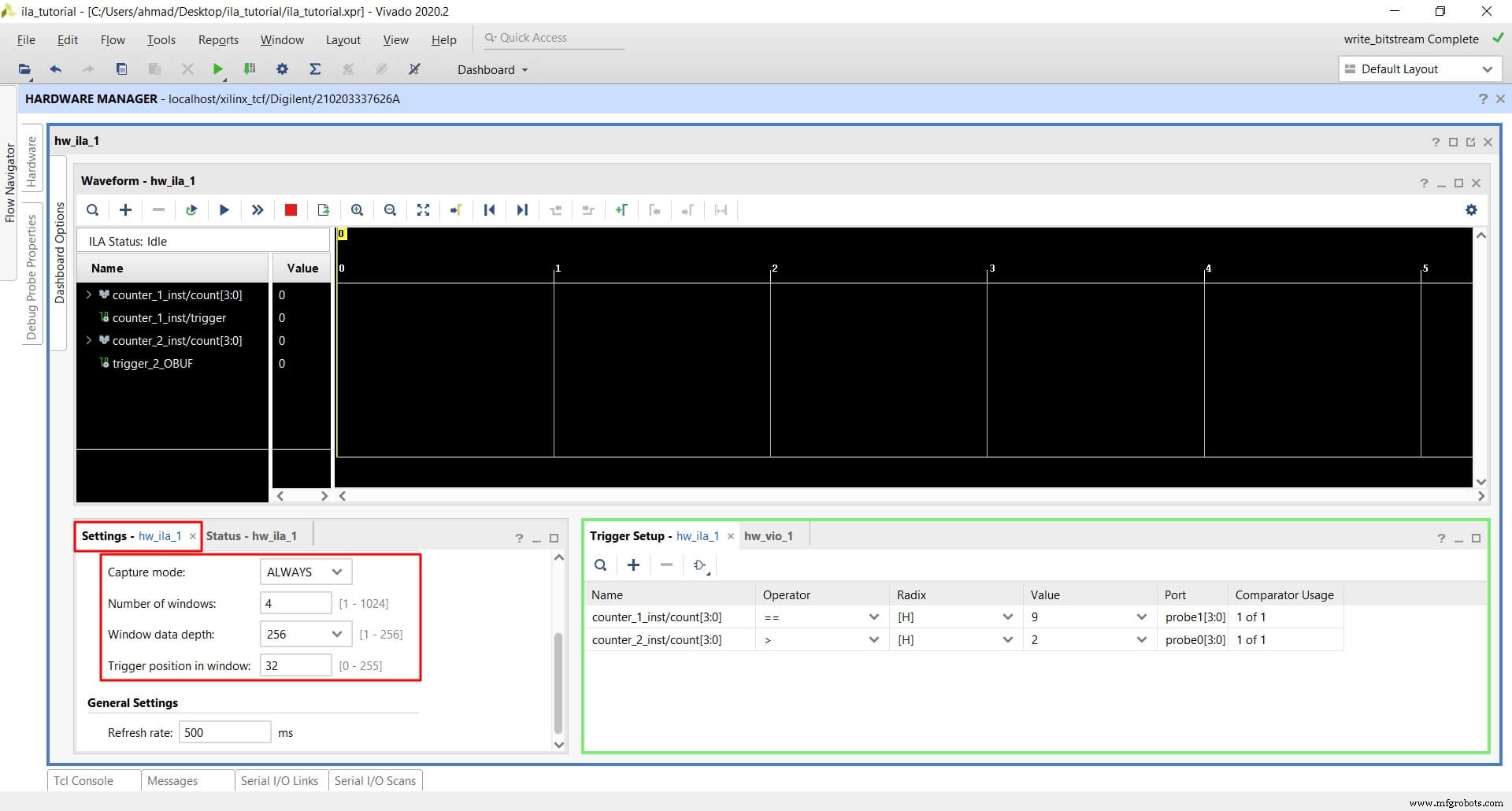

Par exemple, disons que nous voulons déclencher lorsque le compte signal de counter_1_inst est égal à 9 (count ==9) et lorsque le count signal de counter_2_inst est supérieur à 2 (compte> 2). Pour ce faire et diviser le FIFO en quatre fenêtres temporelles, procédez comme suit :

- Modifier réinitialiser retour à 1 depuis vio_reset

- Supprimez la sonde de déclenchement précédente :

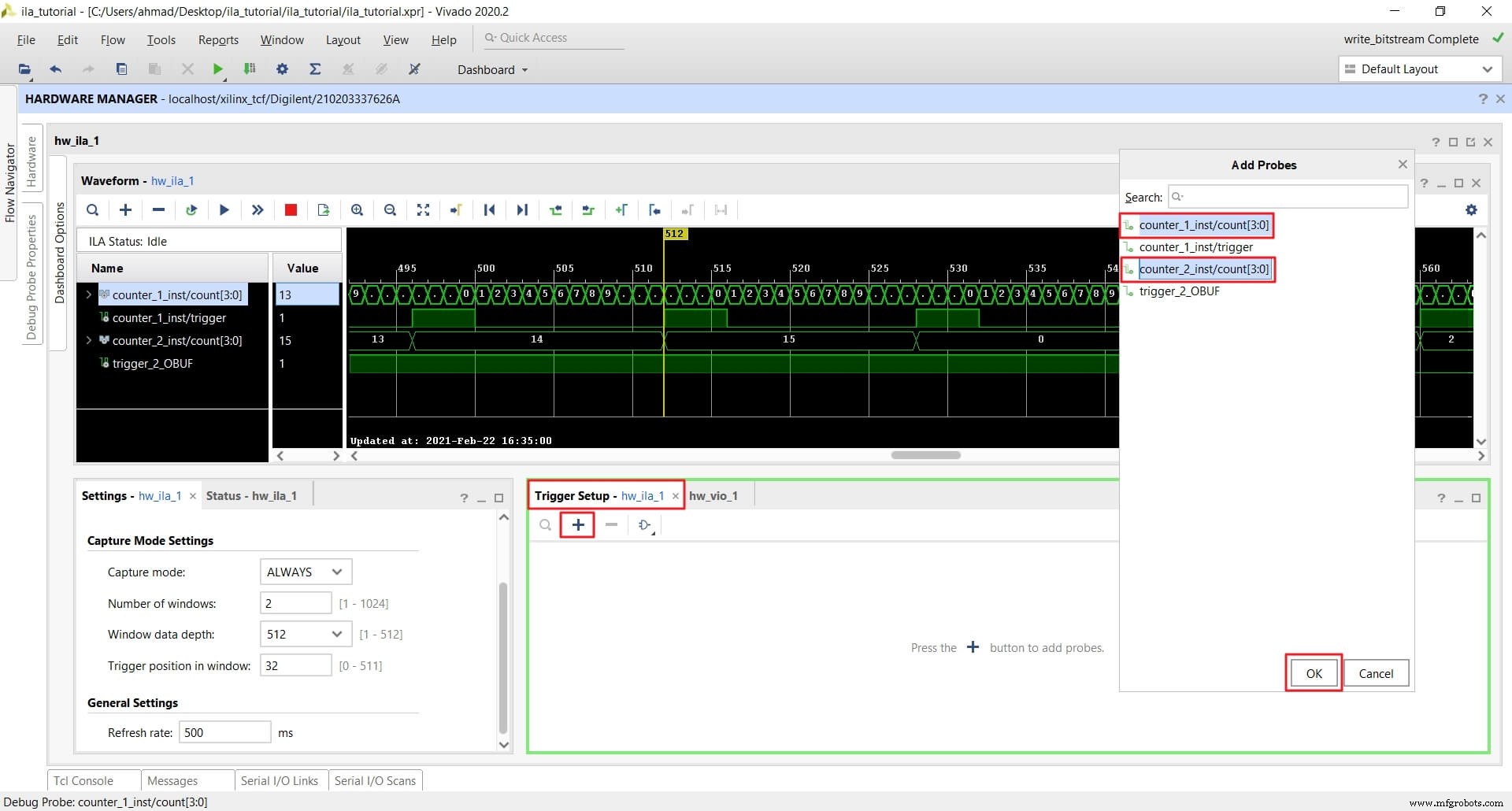

- Ajouter les deux compter signaux comme déclencheurs :

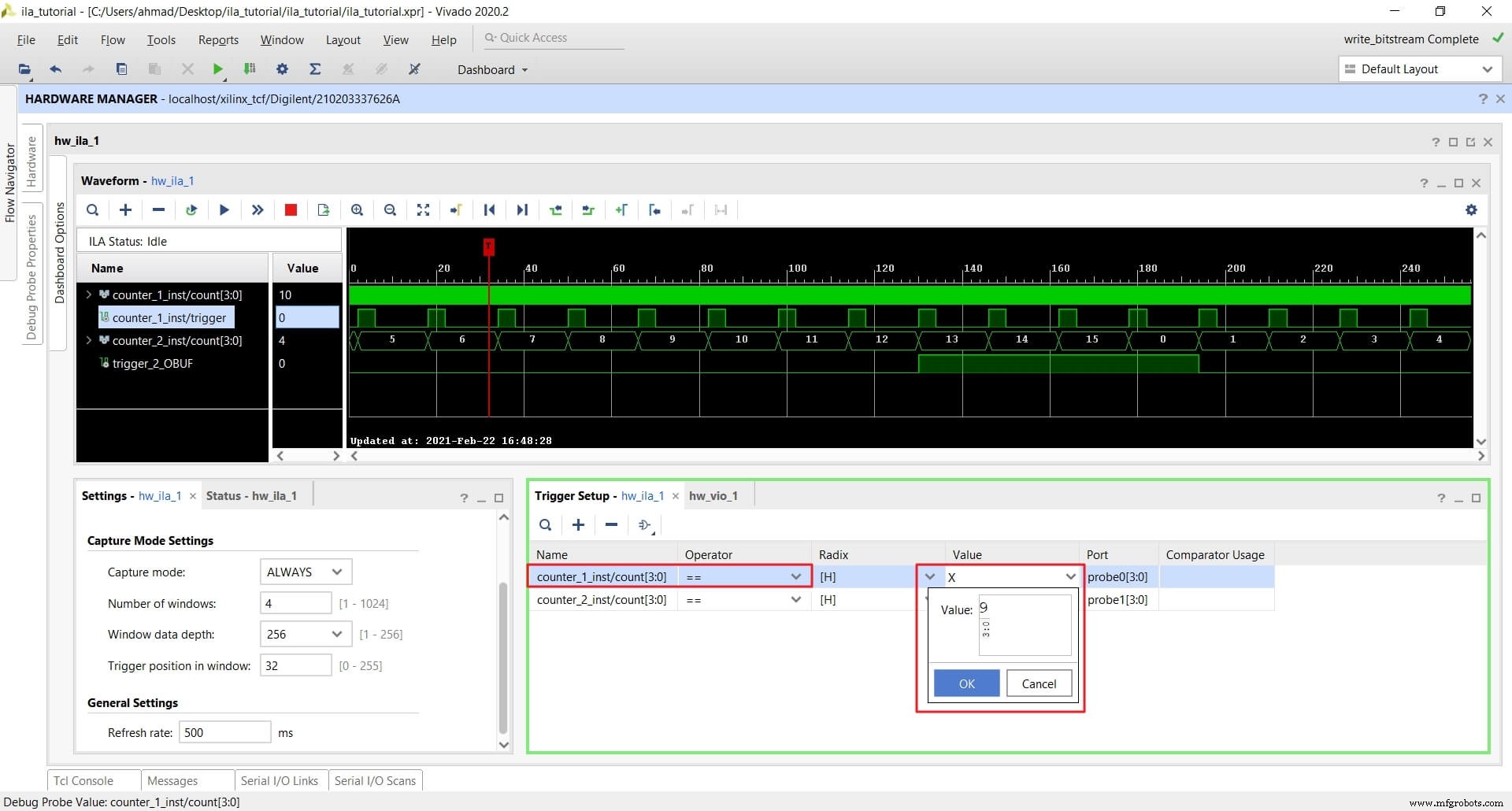

- Configurer le signal compter pour counter_1_inst à (compter ==9):

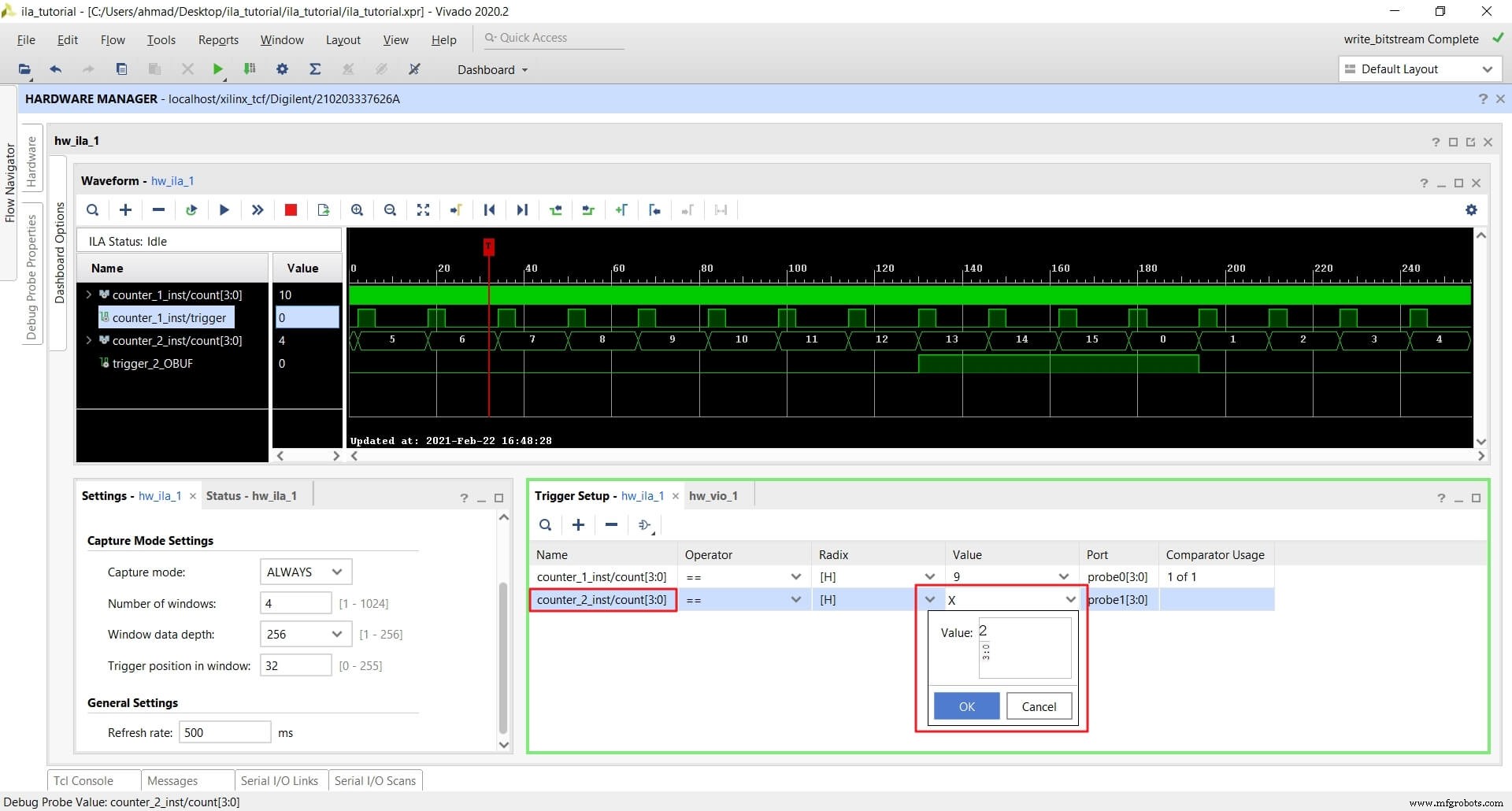

- Configurer le signal compter pour counter_2_inst à (compter> 2):

- Configurer le nombre de fenêtres sur 4 et profondeur FIFO à 256, et placez-vous sur 32 .

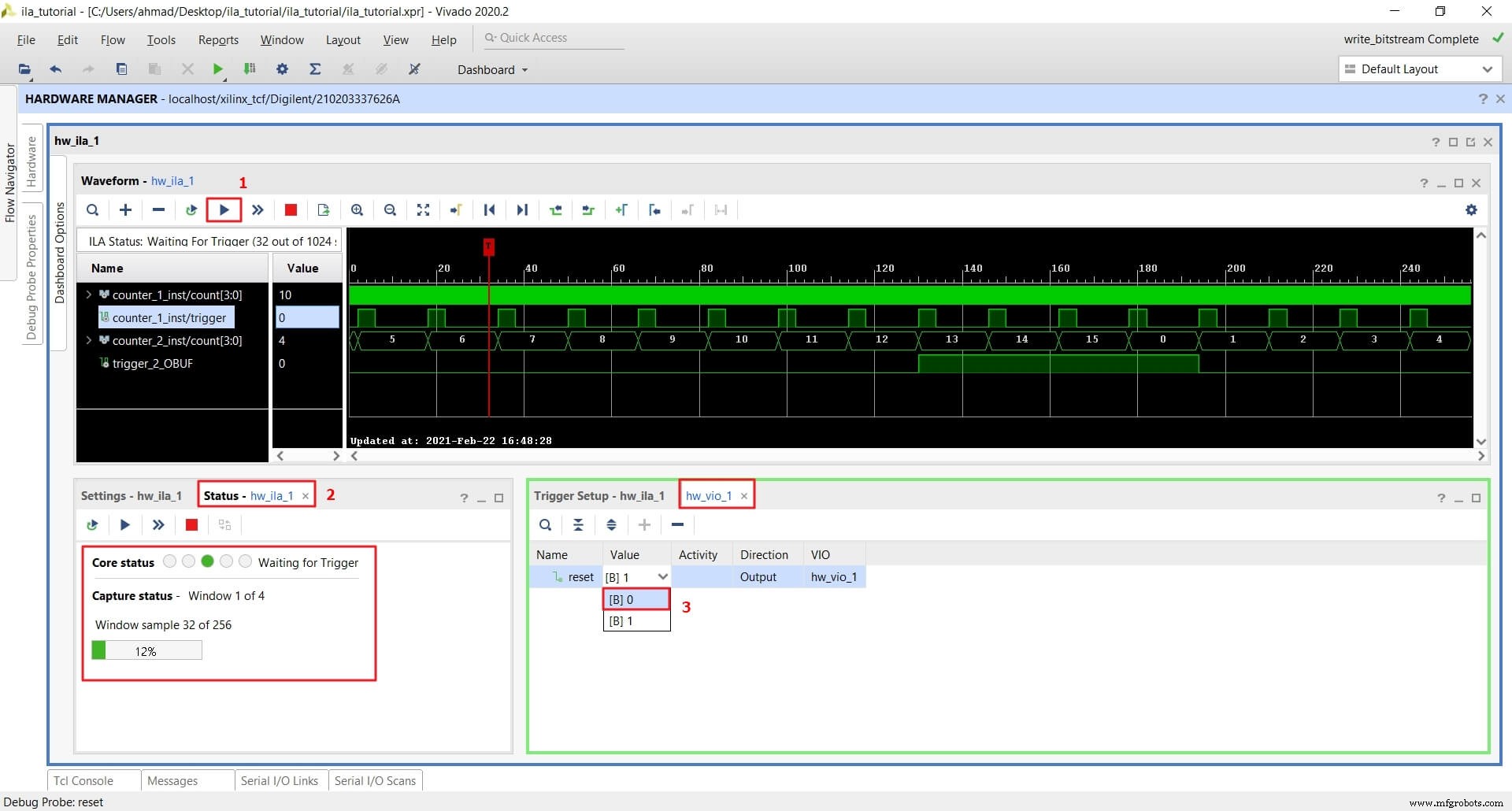

- Cliquez sur le Déclencheur d'exécution bouton, et cela armera la gâchette. Notez que dans la fenêtre Statut hw_ila_1 , l'état de la capture est désormais fenêtre 1 sur 4 car nous avons quatre fenêtres.

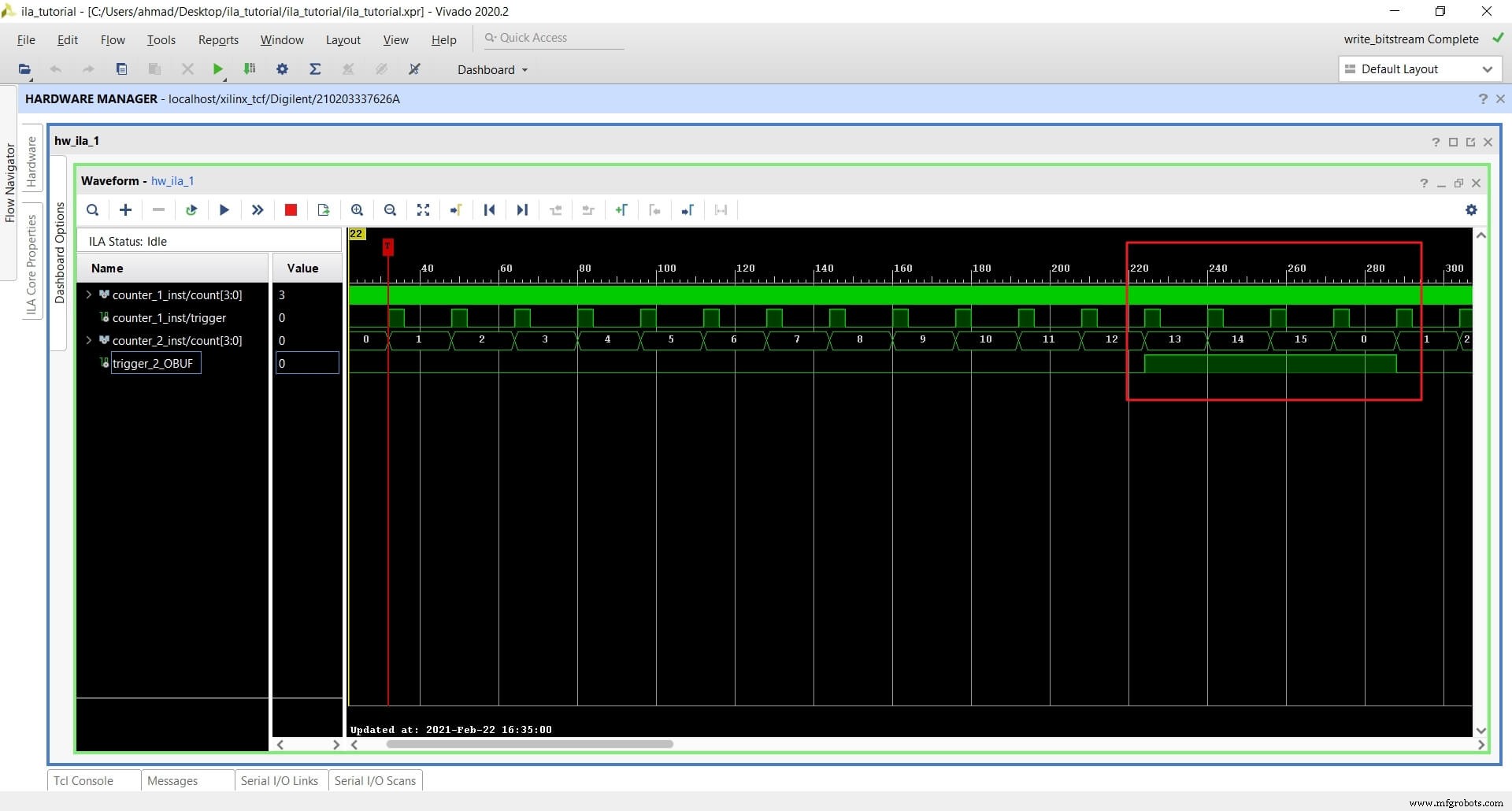

Modifier réinitialiser retour à 0 depuis vio_reset .

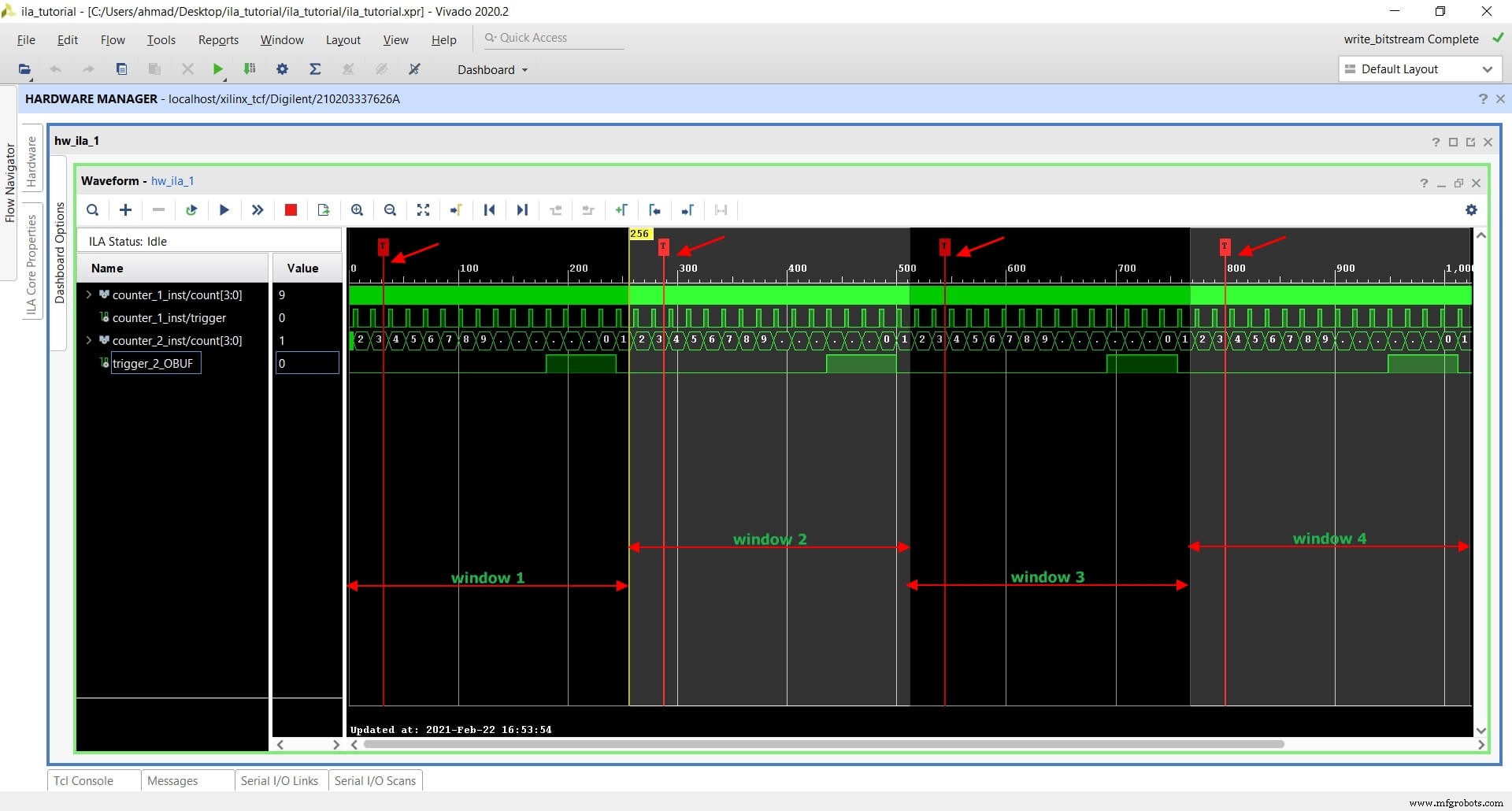

Maximisez la fenêtre de forme d'onde. Nous voyons maintenant que nous avons quatre fenêtres et un déclencheur associé à chaque fenêtre. Notez que ces fenêtres sont indépendantes et non continues.

L'ILA attend que l'événement déclencheur se produise, et lorsqu'il se produit, l'ILA utilise la première fenêtre pour enregistrer 256 échantillons. It then immediately waits for the next trigger until all the windows are full.

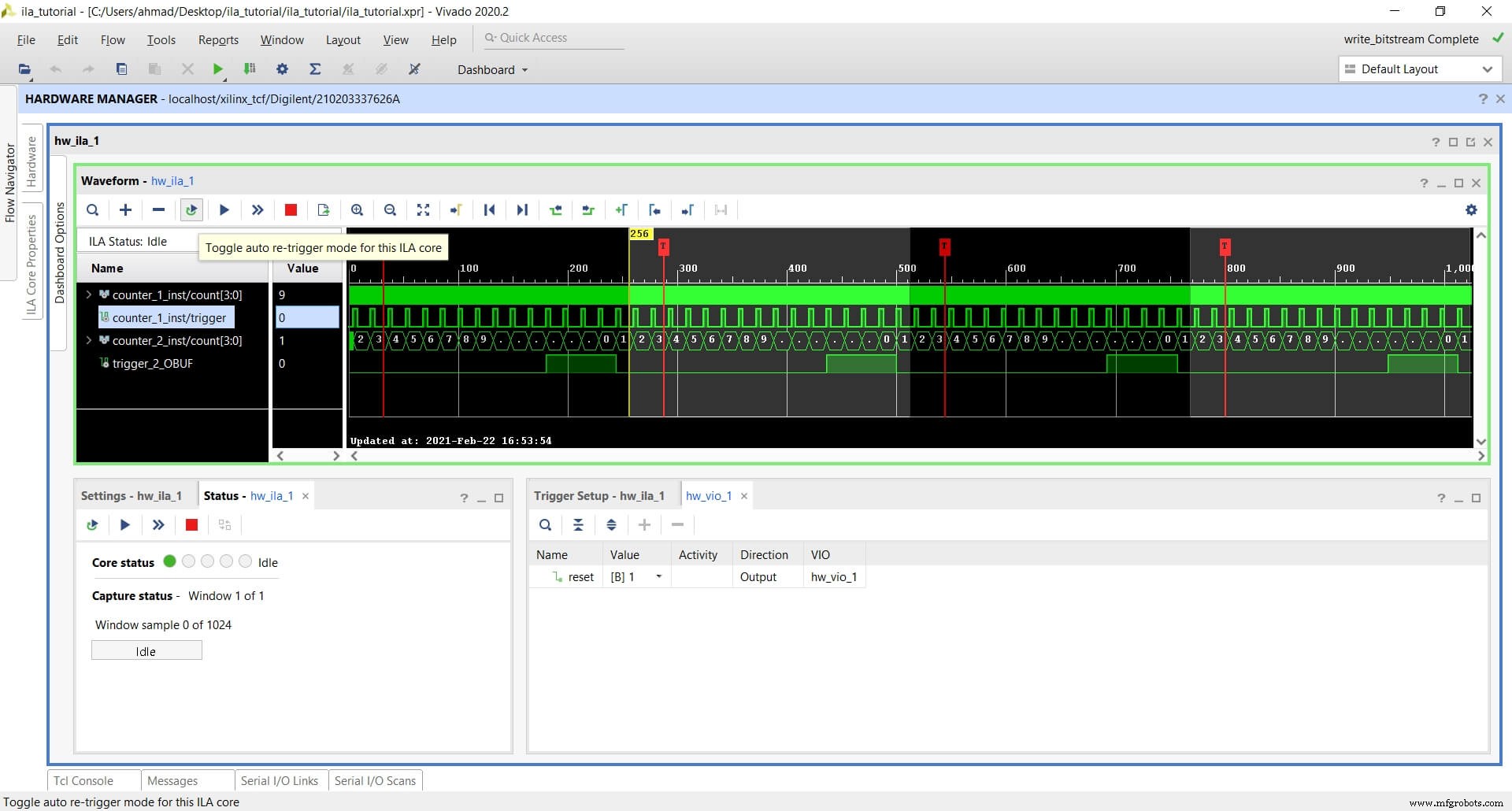

Running ILA with Auto re-trigger mode

ILA has a nice feature called Auto re-trigger that will automatically arm the trigger after it gets triggered. It is useful when monitoring events that occur seldom and you want to run a test overnight. Or you can use it when the trigger happens so often and fast that you cannot arm the trigger manually to capture the samples repeatedly.

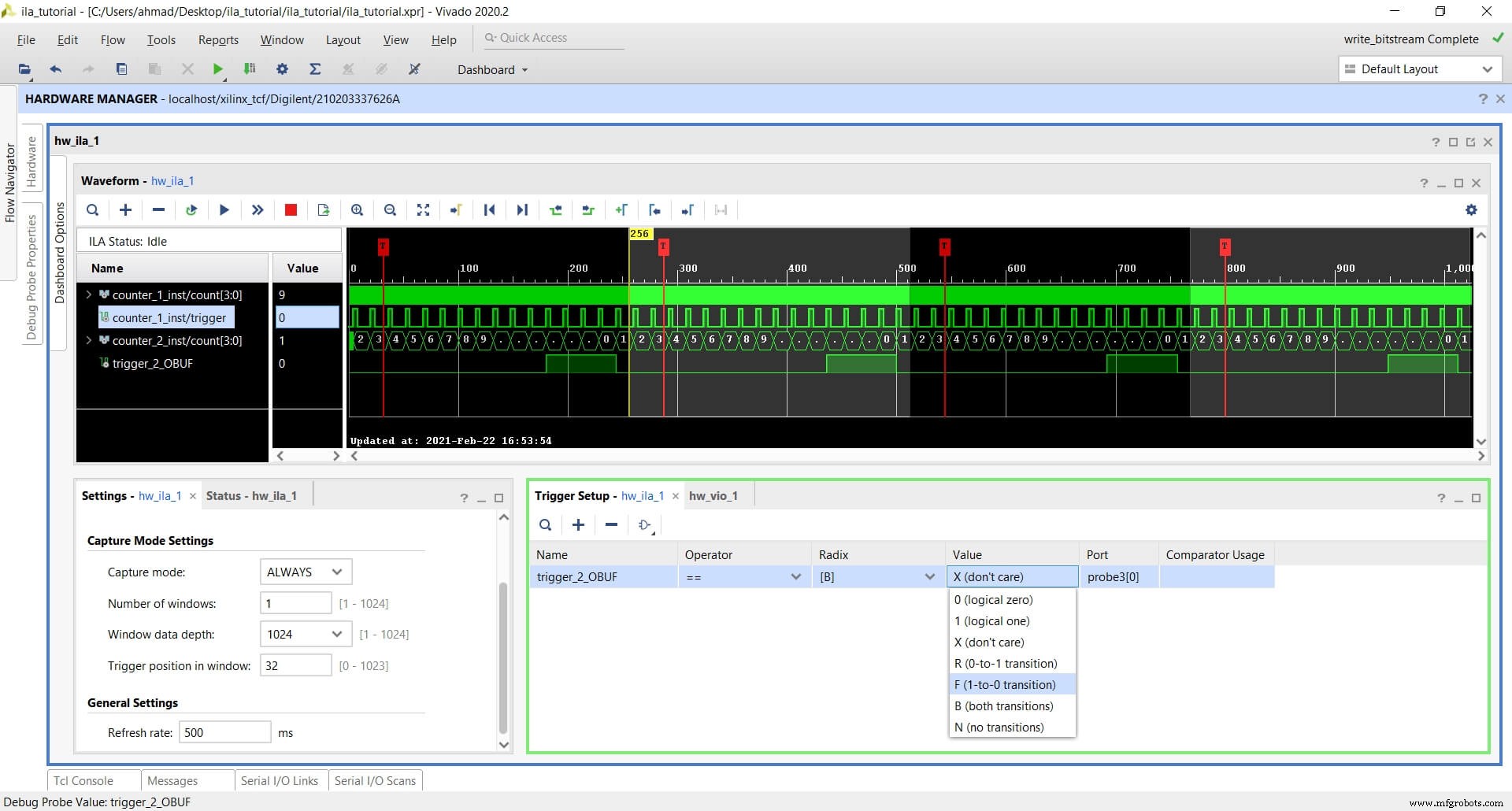

Let us assume that the output port trigger of counter_2_inst gets asserted every 3 hours, and you want to record the data each time it happens. To use the Auto trigger, follow these steps:

- Change reset back to 1 from vio_reset

- Remove the previous trigger probe

- Add trigger_2_OBUF signal as trigger:

- Configure the trigger to the condition to equal (==) and falling edge F(1-to-0 transition)

- Configure the number of windows to 1 and FIFO depth to 1024, and position to 32:

- Click on Auto re-trigger button:

- Finally, change reset back to 0 from vio_reset:

We can see now that the waveform window is getting refreshed and updated as the trigger happen. It is fast, but the behavior is noticeable.

Click on Stop trigger and toggle Auto re-trigger .

Running ILA with Capture mode

Another feature of ILA is the Capture mode . In some cases, you are not interested in recording all the data but rather capture a specific sample. Capture mode helps you filter out data and record only the samples you are interested in.

Let’s say we are only interested in sampling when the output port trigger of counter_1_inst is ‘1’ AND the output port trigger of counter_2_inst is ‘0’.

To use Capture mode to achieve this, follow these steps:

- Change reset back to 1 from vio_reset

- Remove the previous trigger probe

- From the dashboard, Uncheck Trigger Setup and check Capture Setup . Notice that a Capture Setup window will appear. From the Settings – hw_ila_1 window, Change Capture mode to BASIC , the window to 1, the FIFO depth to 1024, and position to 1:

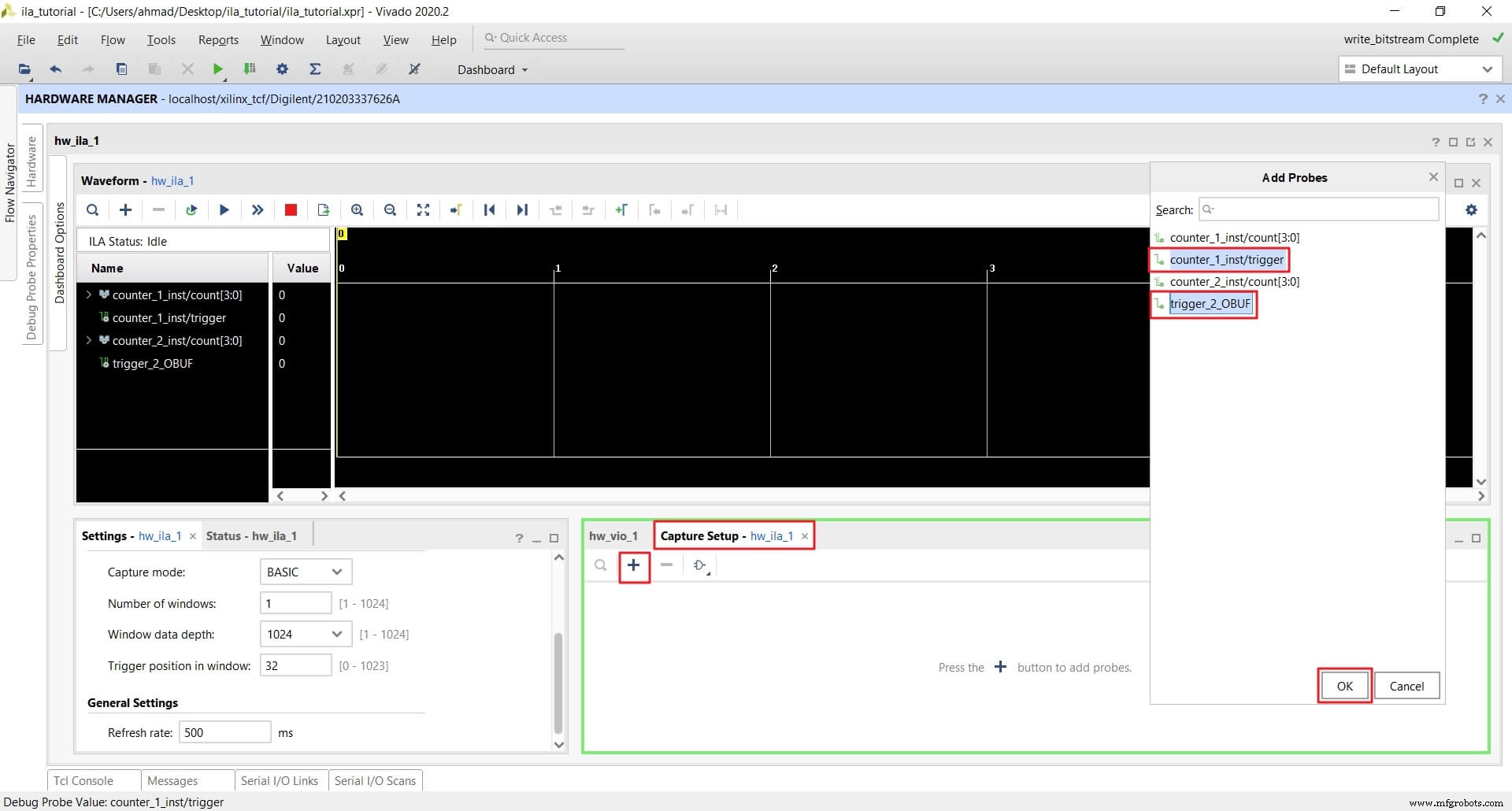

- Add trigger_2_OBUF , and counter_1_inst/trigger from the Capture Setup window:

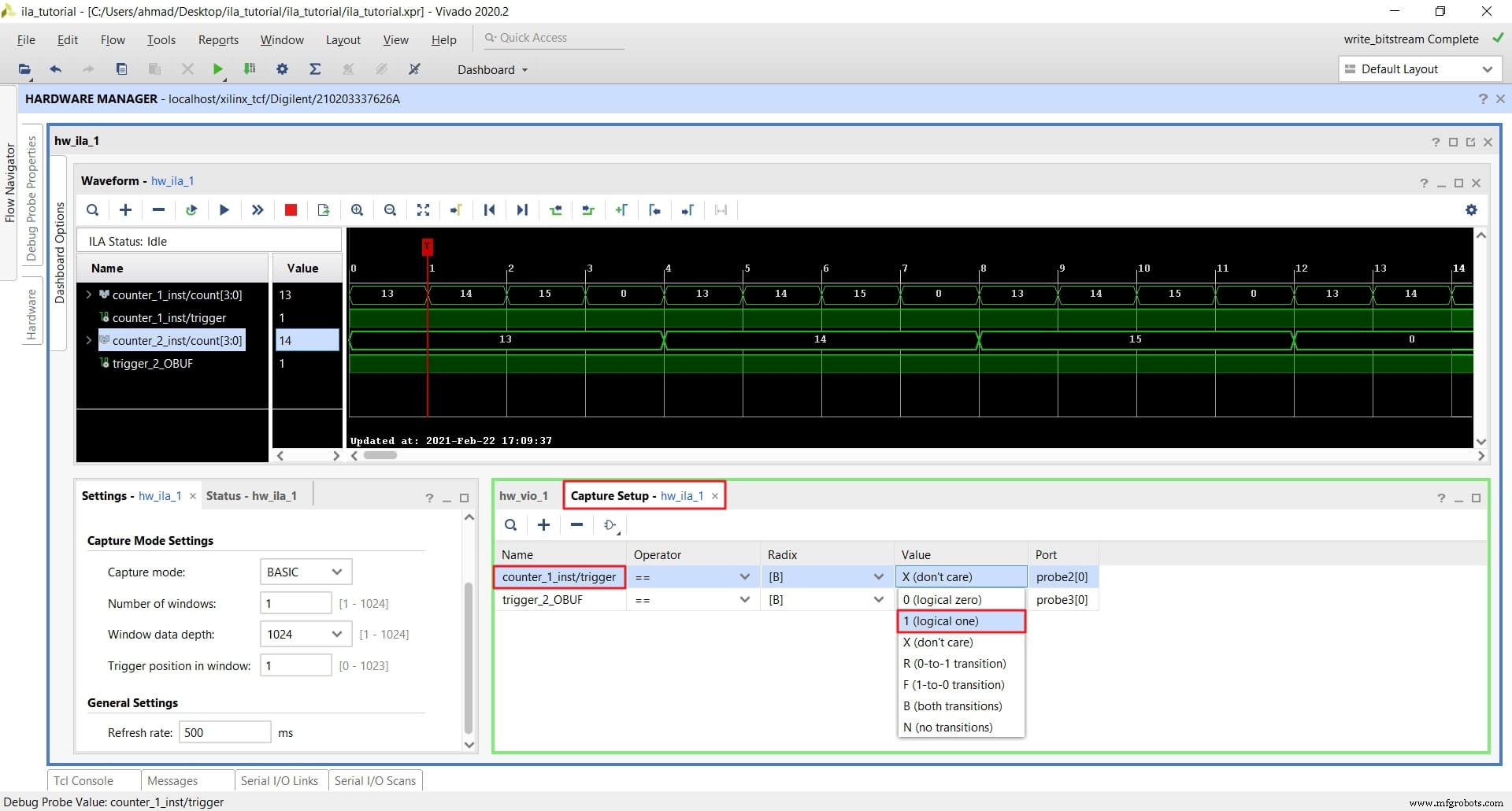

- Configure counter_1_inst/trigger to the condition equal (==) and 1 (logical one) :

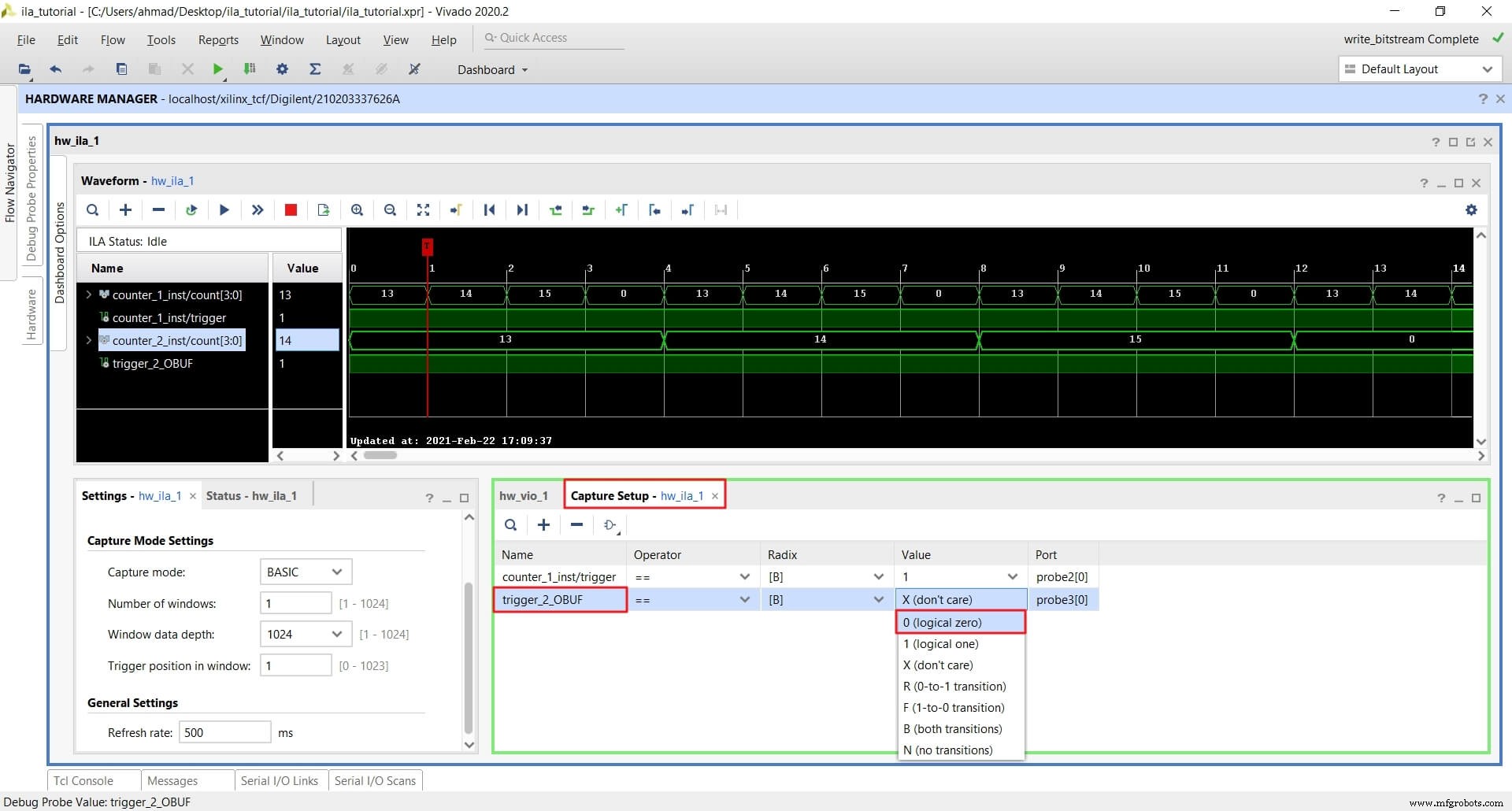

- Configure trigger_2_OBUF to the condition equal (==) and 0 (logical zero) :

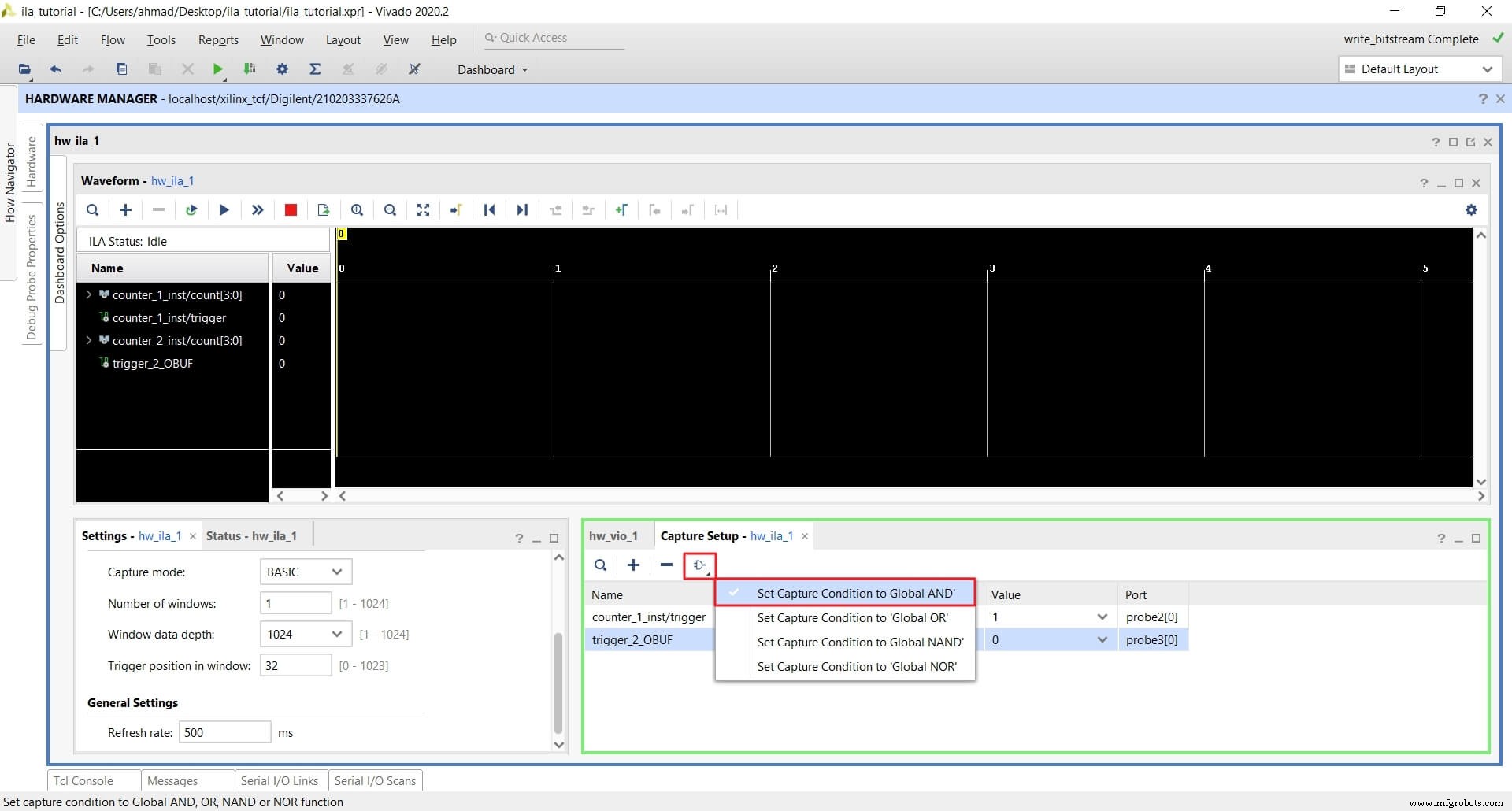

- Change the Capture Condition to Global AND :

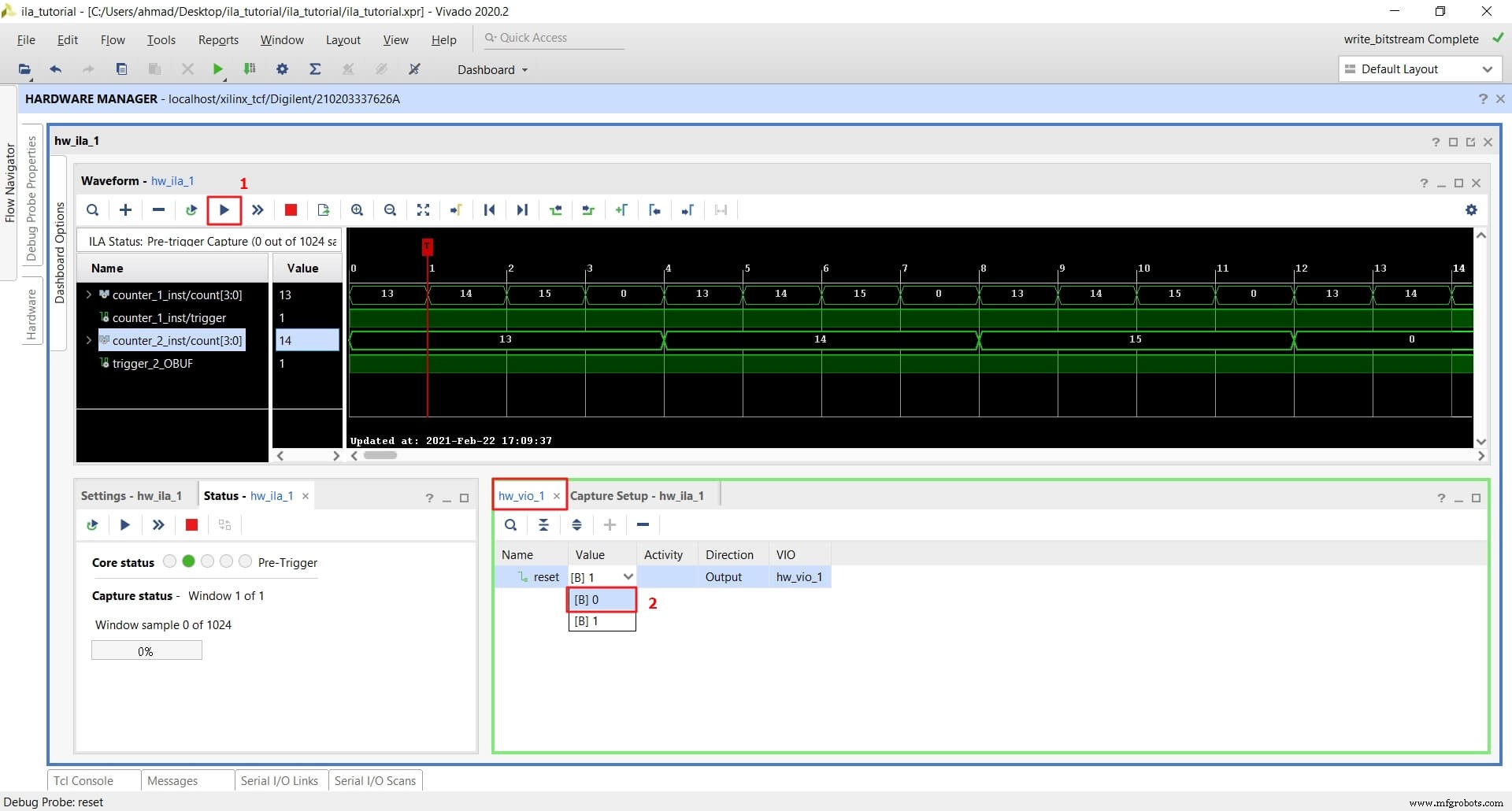

- Click on the Run trigger button and then change reset to 0 from vio_reset :

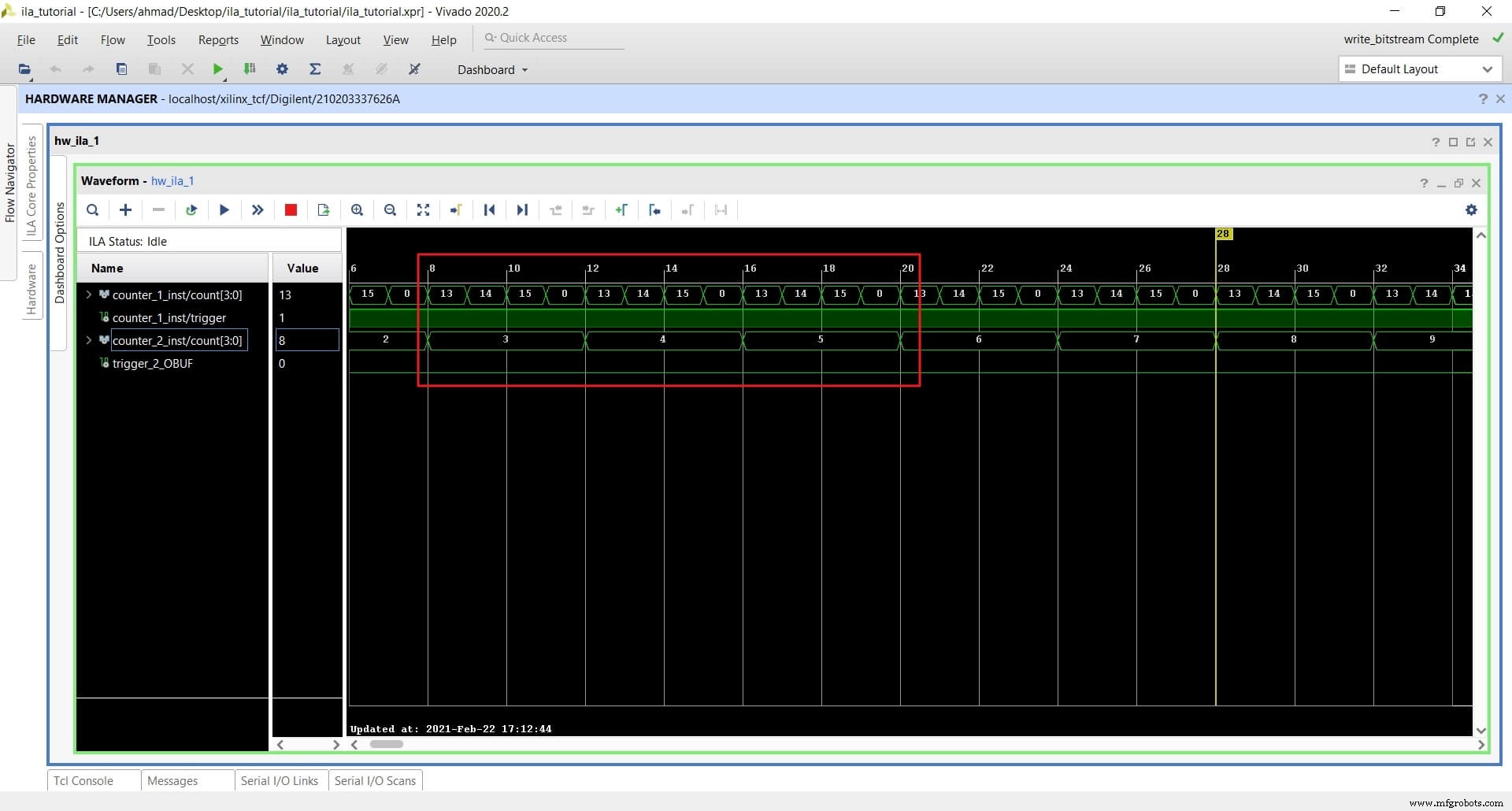

As we can see from the image below, the waveform has only recorded data when counter_1_inst’s count signal is 13, 14, 15, or 0. Any other counts are filtered out because counter_1_inst/trigger is high on these counts only.

Conclusion

In this tutorial, we learned about ILA and VIO and different use-cases for them. ILA and VIO are excellent options for on-chip debugging. They are free, easy to use, flexible, scalable, and simple yet offer advanced features. The use of multiple triggers and Capture mode helps you achieve a complex debugging scheme.

VHDL