Comprendre l'activation du DSP à l'aide du MCU croisé i.MX RT500 de NXP

Découvrez les programmes multi-threads, le développement d'applications utilisant le système d'exploitation en temps réel XOS, le partage de ressources avec des sémaphores et comment la famille i.MX RT500 de NXP des microcontrôleurs aident les ingénieurs à concevoir des appareils intelligents compatibles DSP.

Les appareils grand public intelligents d'aujourd'hui nécessitent des composants capables de traiter de grandes quantités de données pour répondre aux exigences de diverses applications de sécurité et de traitement du signal. Ces composants (y compris les microcontrôleurs) doivent être capables de traiter ces données rapidement et efficacement, nécessitant des processeurs de signaux numériques hautement optimisés.

Cet article présente certaines fonctionnalités du processeur audio Cadence® Tensilica® Fusion F1, un coprocesseur désigné qui aide le processeur principal du MCU i.MX RT500 à effectuer des calculs de traitement du signal.

Concepts fondamentaux des programmes multithreads

À première vue, le matériel de traitement moderne crée l'illusion qu'il exécute plusieurs threads simultanément. En réalité, un seul cœur de processeur s'occupe d'un seul thread à la fois. Lorsque le nombre de threads dépasse le nombre de cœurs de processeur disponibles, un système d'exploitation est nécessaire pour planifier les threads.

Le système d'exploitation doit garder une trace de tous les threads démarrés et de leur état, et il attribue des intervalles de temps CPU à chaque thread afin que diverses applications puissent s'exécuter efficacement et apparemment en parallèle.

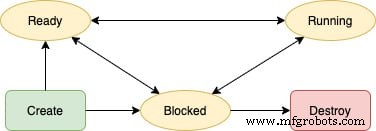

Figure 1. Les différents états d'un fil

Le planificateur du système d'exploitation maintient une file d'attente pour les threads prêts à être exécutés, une file d'attente pour les threads bloquants, et il doit stocker des informations sur les threads en cours d'exécution pour accomplir la répartition équitable du temps CPU :

- Les threads dans la file d'attente des prêts attendent actuellement que le système d'exploitation les planifie sur le processeur. En règle générale, le planificateur du système d'exploitation connaît différents niveaux de priorité, qu'il prend en compte lors du choix du prochain thread à exécuter sur le processeur.

- Les threads bloquants attendent qu'un événement externe se produise, par exemple, une interruption de broche ou une opération de fichier. La planification de ces threads signifierait que le processeur gaspille de la puissance de traitement en attendant la fin d'une opération externe. Une fois l'opération de blocage terminée, le thread d'attente associé revient à la fin de la file d'attente des prêts.

- Les threads en cours d'exécution peuvent effectuer une opération de blocage, ou le système d'exploitation peut planifier un thread différent en fonction de sa stratégie de planification. Dans ce cas, le planificateur déplacera alors le thread en cours d'exécution vers la liste des threads bloqués ou la fin de la file d'attente prête, respectivement.

Les développeurs de système d'exploitation peuvent choisir de mettre en œuvre une ou plusieurs stratégies de planification différentes en fonction des exigences exactes. Outre la planification, la synchronisation et la communication entre les différents threads sont d'autres aspects essentiels des systèmes multithreads.

Conditions et événements dans XOS

Les conditions au sein du XOS RTOS (système d'exploitation en temps réel) permettent aux développeurs de demander à un thread de se bloquer jusqu'à ce qu'une condition spécifiée devienne vraie. Le système évalue chaque condition à l'aide d'une fonction de condition définie par les développeurs d'applications. XOS effectue une évaluation chaque fois qu'un autre thread signale l'objet de condition ou lorsqu'un gestionnaire d'interruption en déclenche un.

Les événements au sein de XOS, en revanche, représentent un groupe de bits que les développeurs peuvent utiliser pour synchroniser différents threads ou threads et gestionnaires d'interruption. XOS permet à plusieurs threads d'attendre des événements et de les signaler simultanément.

Interruptions dans XOS

XOS offre un ensemble complet de fonctionnalités pour gérer les interruptions et les exceptions qui se produisent pendant l'exécution. Les mécanismes d'interruption au sein de XOS offrent aux programmeurs la possibilité d'installer des gestionnaires personnalisés tout en garantissant que la répartition des interruptions fonctionne aussi rapidement que possible dans le système. Le XOS prend également en charge la gestion des interruptions imbriquées, ce qui signifie que le système d'exploitation suspend le gestionnaire d'interruptions actuel si une interruption de priorité plus élevée se produit. Une fois que le système a fini de gérer l'interruption de haute priorité, il reprend automatiquement le traitement des interruptions de basse priorité.

Les threads peuvent également avoir des services liés au temps tels que des retards temporisés et des rappels de minuterie périodiques dans XOS. Le coprocesseur DSP prend en charge jusqu'à trois minuteries internes que les programmeurs peuvent configurer selon les besoins.

Comprendre les sémaphores

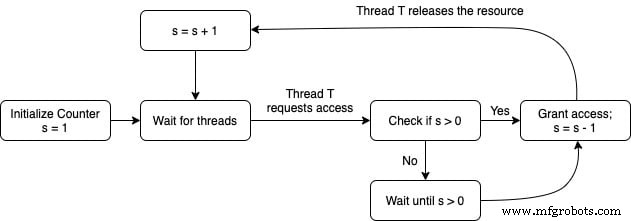

Dans la programmation multithread, les sémaphores fournissent un moyen de contrôler et de coordonner l'accès à une ressource partagée. Les sémaphores aident à éviter les problèmes de section critique dans les systèmes concurrents en synchronisant différents threads. Les sémaphores sont une construction simple qui garde la trace d'un compteur interne avec une valeur de départ prédéterminée que les programmeurs peuvent librement définir dans le code source. Différentes implémentations existent, mais le compteur représente généralement le nombre de threads pouvant encore accéder à une ressource partagée.

A chaque fois qu'un thread souhaite accéder à la ressource partagée, le système vérifie si le compteur associé est supérieur à zéro. Si c'est le cas, le système d'exploitation accorde l'accès à la ressource et diminue le compteur interne du sémaphore. Si un thread ne peut pas accéder à la ressource à un moment donné, le thread passe dans un état de blocage et attend jusqu'à ce qu'il reçoive l'accès à la ressource. Chaque fois qu'un thread libère la ressource, le système d'exploitation augmente le compteur de sémaphores, et un nouveau thread peut entrer dans la section critique.

Figure 2. Un organigramme illustrant le fonctionnement des sémaphores

Une présentation du MCU i.MX RT500 et du DSP

i.MX RT500 est une famille de microcontrôleurs double cœur basée sur un puissant cœur Arm® Cortex®-M33 avec une vitesse d'horloge allant jusqu'à 275 MHz et prenant en charge jusqu'à cinq mégaoctets de SRAM.

Le MCU i.MX RT500 offre des fonctions de protection telles que Arm TrustZone et une unité de protection de la mémoire (MPU) intégrée prenant en charge jusqu'à huit régions. Le coprocesseur crypto CASPER permet à l'accélération matérielle de booster diverses fonctions requises pour les algorithmes cryptographiques asymétriques. Un ensemble de fonctionnalités d'économie d'énergie permet aux concepteurs d'adapter la consommation électrique de l'i.MX RT500 aux exigences de leur application.

Divers accélérateurs matériels dédiés aident le processeur principal à effectuer les calculs DSP. Un DSP audio Cadence® Tensilica® Fusion F1 supplémentaire, un GPU 2D avec accélération graphique vectorielle et diverses interfaces d'affichage rendent l'i.MX RT500 adapté à diverses applications embarquées sécurisées et à faible consommation d'énergie. Les cas d'utilisation typiques incluent les applications IHM, les appareils IoT, les appareils auditifs, les assistants personnels à commande vocale et d'autres appareils grand public similaires.

Un regard sur le DSP audio

L'i.MX RT500 contient divers coprocesseurs spéciaux qui peuvent aider à alléger la charge sur les cœurs du processeur en effectuant des calculs mathématiquement complexes tout en laissant les cœurs de traitement libres d'effectuer d'autres tâches. L'un de ces processeurs dédiés est le DSP fusion, qui comprend un processeur audio Cadence® Tensilica® Fusion F1 et une unité matérielle à virgule flottante.

Ce moteur de traitement audio fonctionne à des fréquences allant jusqu'à 200 MHz et est conçu pour activer des appareils à déclenchement vocal permanents, tels que des assistants virtuels. En outre, le DSP audio combine divers modules pour les tâches typiques de pré-traitement et de post-traitement à l'aide de nombreux codecs audio.

Le DSP et les cœurs du processeur principal peuvent communiquer entre eux via divers moyens. Les développeurs peuvent utiliser l'intégralité de la SRAM lorsqu'ils travaillent avec le DSP de fusion, à moins que la RAM ne soit protégée et que certaines parties soient marquées pour un accès sécurisé uniquement.

Programmer avec le DSP en tête

Les DSP Tensilica prennent en charge divers systèmes d'exploitation en temps réel (RTOS), notamment FreeRTOS™, Zephyr™, Linux® et XOS. Cadence a développé le noyau intégré XOS comme conception de référence en pensant aux processeurs Tensilica.

Les fonctionnalités légères du noyau XOS incluent un planificateur de tâches, une commutation de contexte adaptative, des mécanismes de synchronisation, une gestion des interruptions et des exceptions et une gestion des ressources critiques. Le code source du noyau est principalement écrit en C standard et non spécifique aux processeurs Xtensa et aux DSP.

Répondre aux exigences des appareils intelligents pour les consommateurs

La famille de microcontrôleurs croisés i.MX RT500 possède diverses fonctionnalités conçues pour inspirer les appareils grand public intelligents de demain. Les différents coprocesseurs aident les principaux cœurs de traitement du MCU à effectuer des calculs mathématiquement complexes pour les applications de sécurité et de traitement du signal. L'un de ces coprocesseurs est le DSP audio Cadence® Tensilica® Fusion F1 hautement optimisé, permettant d'activer en permanence des appareils à déclenchement vocal tels que des assistants virtuels. Les programmeurs peuvent utiliser XOS et l'IDE Xplorer pour concevoir des applications pour le processeur Cadence dédié.

La note d'application AN13159 contient plus de détails, une liste des fonctions API prises en charge et des exemples de conditions et d'événements dans XOS, et le site Web de NXP offre plus d'informations sur les capacités et applications i.MX RT500. Il fournit également différents supports de formation tels que des notes d'application, des vidéos et des webinaires à la demande.

Les articles sur l'industrie sont une forme de contenu qui permet aux partenaires de l'industrie de partager des actualités, des messages et des technologies utiles avec les lecteurs d'All About Circuits d'une manière qui ne convient pas au contenu éditorial. Tous les articles de l'industrie sont soumis à des directives éditoriales strictes dans le but d'offrir aux lecteurs des nouvelles utiles, une expertise technique ou des histoires. Les points de vue et opinions exprimés dans les articles de l'industrie sont ceux du partenaire et pas nécessairement ceux d'All About Circuits ou de ses rédacteurs.

Embarqué

- C# en utilisant

- Le périphérique hybride fusionne les architectures DSP et MCU

- Quand un DSP bat un accélérateur matériel

- Décisions, décisions :accélérateur matériel ou DSP ?

- Mesure sans contact du niveau de fluide à l'aide d'une puce de réflectomètre

- Utilisation de balises RFID pour la surveillance de la sécurité à domicile

- Le MCU Bluetooth améliore la sécurité de l'IoT

- Le MCU sans fil présente une architecture double cœur

- Directives pour l'utilisation de la poignée DSP