Signé ou non signé en VHDL

Tous les concepteurs numériques doivent comprendre comment les mathématiques fonctionnent à l'intérieur d'un FPGA ou d'un ASIC. La première étape consiste à comprendre comment fonctionnent les types de signaux signés et non signés. Les types signés et non signés existent dans numeric_std package, qui fait partie de la bibliothèque ieee. Il convient de noter qu'il existe un autre fichier de package fréquemment utilisé pour effectuer des opérations mathématiques :std_logic_arith . Cependant, std_logic_arith n'est pas un fichier de package officiel pris en charge par ieee et il n'est pas recommandé de l'utiliser dans les conceptions numériques.

Un signal défini comme type signé signifie que les outils interprètent ce signal comme étant positif ou négatif. Un signal défini comme type unsigned signifie que le signal ne sera que positif. En interne, le FPGA utilisera le complément à deux représentation. Par exemple, un signal 3 bits peut être interprété selon le tableau ci-dessous :

Êtes-vous encore confus? Vous devriez l'être, ce n'est pas intuitif ! Prenons un exemple qui, espérons-le, clarifiera les choses. Le fichier ci-dessous teste le fonctionnement de Signed Unsigned. Ce qu'il faut comprendre, c'est que le fait que les signaux soient définis ou non comme signés ou non signés ne le fait pas affecter la façon dont les calculs binaires réels sont effectués.

Par exemple :pour deux vecteurs signés 10001 + 00010, la réponse est toujours 10011, MAIS c'est l'interprétation du résultat qui est différent.

Pour le cas non signé, la réponse (10011) représente 19.

Pour le cas signé, la réponse (10011) représente -13.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity signed_unsigned is

port (

i_rst_l : in std_logic;

i_clk : in std_logic;

i_a : in std_logic_vector(4 downto 0);

i_b : in std_logic_vector(4 downto 0)

);

end signed_unsigned;

architecture behave of signed_unsigned is

signal rs_SUM_RESULT : signed(4 downto 0) := (others => '0');

signal ru_SUM_RESULT : unsigned(4 downto 0) := (others => '0');

signal rs_SUB_RESULT : signed(4 downto 0) := (others => '0');

signal ru_SUB_RESULT : unsigned(4 downto 0) := (others => '0');

begin

-- Purpose: Add two numbers. Does both the signed and unsigned

-- addition for demonstration. This process is synthesizable.

p_SUM : process (i_clk, i_rst_l)

begin

if i_rst_l = '0' then -- asynchronous reset (active low)

rs_SUM_RESULT <= (others => '0');

ru_SUM_RESULT <= (others => '0');

elsif rising_edge(i_clk) then

ru_SUM_RESULT <= unsigned(i_a) + unsigned(i_b);

rs_SUM_RESULT <= signed(i_a) + signed(i_b);

end if;

end process p_SUM;

-- Purpose: Subtract two numbers. Does both the signed and unsigned

-- subtraction for demonstration. This process is synthesizable.

p_SUB : process (i_clk, i_rst_l)

begin

if i_rst_l = '0' then -- asynchronous reset (active low)

rs_SUB_RESULT <= (others => '0');

ru_SUB_RESULT <= (others => '0');

elsif rising_edge(i_clk) then

ru_SUB_RESULT <= unsigned(i_a) - unsigned(i_b);

rs_SUB_RESULT <= signed(i_a) - signed(i_b);

end if;

end process p_SUB;

end behave;

Banc de test :

library ieee;

use ieee.std_logic_1164.all;

entity example_signed_unsigned_tb is

end example_signed_unsigned_tb;

architecture behave of example_signed_unsigned_tb is

--Registers

signal r_CLK : std_logic := '0';

signal r_RST_L : std_logic := '0';

signal r_A : natural := 0;

signal r_B : natural := 0;

signal r_A_SLV : std_logic_vector(4 downto 0) := (others => '0');

signal r_B_SLV : std_logic_vector(4 downto 0) := (others => '0');

constant c_CLK_PERIOD : time := 10 ns;

component example_signed_unsigned is

port (

i_rst_l : in std_logic;

i_clk : in std_logic;

i_a : in std_logic_vector(4 downto 0);

i_b : in std_logic_vector(4 downto 0)

);

end component example_signed_unsigned;

begin

i_DUT: example_signed_unsigned

port map (

i_rst_l => r_RST_L,

i_clk => r_CLK,

i_a => r_A_SLV,

i_b => r_B_SLV

);

clk_gen : process is

begin

r_CLK <= '0' after c_CLK_PERIOD/2, '1' after c_CLK_PERIOD;

wait for c_CLK_PERIOD;

end process clk_gen;

process

begin

r_RST_L <= '0';

wait for 20 ns;

r_RST_L <= '1';

wait for 20 ns;

r_A_SLV <= "01001";

r_B_SLV <= "00110";

wait for 20 ns;

r_A_SLV <= "10001";

r_B_SLV <= "00110";

wait for 20 ns;

r_A_SLV <= "10001";

r_B_SLV <= "00001";

wait for 20 ns;

r_A_SLV <= "10001";

r_B_SLV <= "00010";

wait for 20 ns;

r_A_SLV <= "11111";

r_B_SLV <= "00001";

wait for 20 ns;

r_A_SLV <= "00000";

r_B_SLV <= "00001";

wait for 20 ns;

wait;

end process;

end behave;

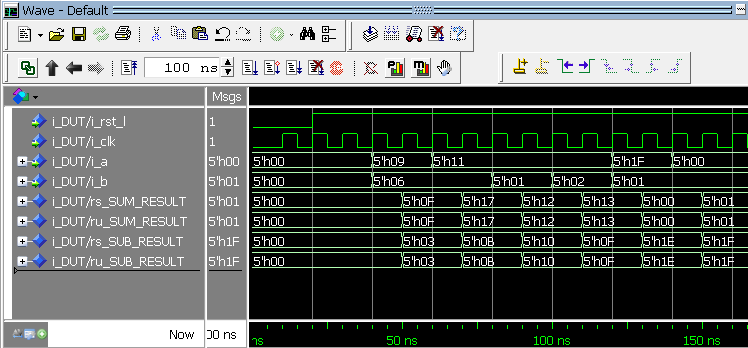

Valeurs de sortie d'onde de simulation Modelsim affichées en HEX

Valeurs de sortie d'onde de simulation Modelsim affichées en HEX

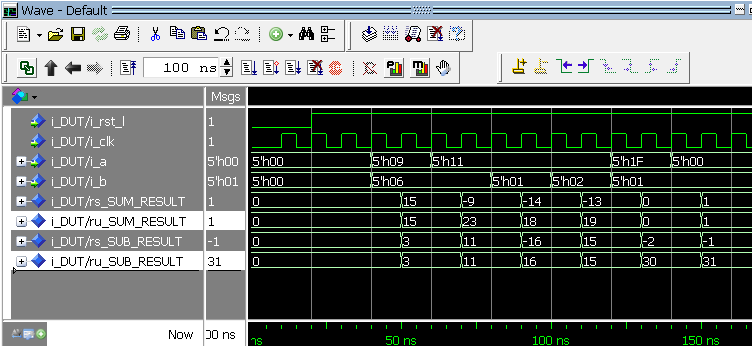

Valeurs de sortie d'onde de simulation Modelsim affichées en DECIMAL

Valeurs de sortie d'onde de simulation Modelsim affichées en DECIMAL Comparez les deux captures d'écran Modelsim ci-dessus. Dans le premier, vous pouvez voir que les résultats des fonctions mathématiques sont exactement les mêmes lorsqu'elles sont représentées en hexadécimal. C'est l'interprétation des résultats qui est différent. Cela peut être vu en regardant la capture d'écran du bas. Lorsque Modelsim affiche les résultats en décimal, il interprète certains d'entre eux comme des nombres négatifs. Lorsque vous utilisez des types signés et non signés, vous devez être très prudent ! J'espère que vous comprenez un peu mieux ce sujet. J'ai l'impression que c'est un domaine avec lequel de nombreux concepteurs numériques ont du mal, donc s'il y a quelque chose que vous ne comprenez pas entièrement, envoyez-moi un e-mail via le lien de contact sur la barre latérale et j'essaierai de le rendre plus clair.

VHDL