Présentation de Verilog

Verilog est un type de langage de description matérielle (HDL). Verilog est l'un des deux langages utilisés par l'éducation et les entreprises pour concevoir des FPGA et des ASIC. Si vous n'êtes pas familier avec le fonctionnement des FPGA et des ASIC, vous devriez lire cette page pour une introduction aux FPGA et aux ASIC. Verilog et VHDL sont les deux HDL les plus utilisés. Comparé aux langages logiciels traditionnels tels que Java ou C, Verilog fonctionne très différemment. Commençons par regarder un exemple simple.

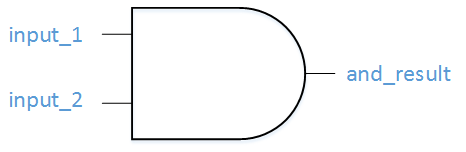

Nous allons d'abord créer un fichier Verilog qui décrit une porte Et. Pour rappel, une simple porte And a deux entrées et une sortie. La sortie est égale à 1 uniquement lorsque les deux entrées sont égales à 1. Vous trouverez ci-dessous une image de la porte ET que nous allons décrire avec Verilog.

Une porte et

Une porte et Allons-y ! Une unité fondamentale de Verilog s'appelle un fil. Pour l'instant, supposons qu'un fil ne peut être qu'un 0 ou un 1. Voici une logique de fil de base :

wire and_temp; assign and_temp = input_1 & input_2;

Nous créons un fil appelé and_temp sur la première ligne de code. Sur la deuxième ligne du code, nous prenons le fil que nous avons créé et nous assignons le fil. Pour l'attribuer, nous utilisons la fonction booléenne AND qui, dans Verilog, est l'esperluette (&). Si vous deviez décrire le code ci-dessus, vous pourriez dire :"Le signal and_temp obtient input_1 AND-ed avec input_2."

Input_1 et Input_2 sont des entrées de ce morceau de code Verilog. Montrons la liste complète des entrées et des sorties. Cela se fait dans le module définition. Module est un mot-clé réservé dans Verilog qui montre la création d'un bloc de code avec des entrées et des sorties définies.

module example_and_gate

(

input_1,

input_2,

and_result);

input input_1;

input input_2;

output and_result;

Ceci est votre module de base. Il définit notre module appelé example_and_gate et 3 signaux, 2 entrées et 1 sortie. Mettons tout ensemble pour finir le dossier. La seule chose qui nous manque est l'affectation de la sortie and_result . Une autre note, // dans Verilog est utilisé pour un commentaire.

///////////////////////////////////////////////////////////////////////////////

// File Downloaded from http://www.nandland.com

///////////////////////////////////////////////////////////////////////////////

module example_and_gate

(

input_1,

input_2,

and_result);

input input_1;

input input_2;

output and_result;

wire and_temp;

assign and_temp = input_1 & input_2;

assign and_result = and_temp;

endmodule // example_and_gate

Toutes nos félicitations! Vous avez créé votre premier fichier Verilog.

Vous semble-t-il que vous avez dû écrire beaucoup de code juste pour créer une porte stupide et ? Tout d'abord, et les portes ne sont pas stupides. Deuxièmement, vous avez raison, les HDL nécessitent beaucoup de code pour effectuer des tâches relativement simples. Vous pouvez être rassuré par le fait que Verilog est au moins moins verbeux que VHDL. Habituez-vous au fait que faire quelque chose qui était très simple dans un logiciel vous prendra beaucoup plus de temps dans un HDL tel que Verilog ou VHDL. Mais demandez simplement à un logiciel d'essayer de générer une image sur un moniteur VGA qui affiche le jeu de la vie de Conway et regardez leur tête tourner d'étonnement ! Au fait, cette vidéo est créée avec un FPGA. Vous pourrez le faire bien assez tôt !

Verilog