Conception embarquée avec FPGA :langages d'implémentation

Note de l'éditeur :alors que des algorithmes avancés continuent d'émerger pour la conception de produits intelligents, les développeurs ont souvent du mal à mettre en œuvre des systèmes embarqués capables de répondre aux demandes de traitement associées de ces algorithmes. Les FPGA peuvent fournir les performances requises, mais la conception avec des FPGA a longtemps été considérée comme limitée aux experts en programmation FPGA. Aujourd'hui, cependant, la disponibilité de FPGA plus puissants et d'environnements de développement plus efficaces a rendu le développement de FPGA largement accessible. Dans cet extrait, chapitre 4 du livre Architecting High-Performance Embedded Systems, l'auteur propose une revue complète des périphériques FPGA, des langages d'implémentation et du processus de développement FPGA, ainsi qu'une procédure détaillée sur la façon de commencer à implémenter des FPGA dans votre propre conception. L'extrait complet est présenté dans la série de fascicules suivante :

Note de l'éditeur :alors que des algorithmes avancés continuent d'émerger pour la conception de produits intelligents, les développeurs ont souvent du mal à mettre en œuvre des systèmes embarqués capables de répondre aux demandes de traitement associées de ces algorithmes. Les FPGA peuvent fournir les performances requises, mais la conception avec des FPGA a longtemps été considérée comme limitée aux experts en programmation FPGA. Aujourd'hui, cependant, la disponibilité de FPGA plus puissants et d'environnements de développement plus efficaces a rendu le développement de FPGA largement accessible. Dans cet extrait, chapitre 4 du livre Architecting High-Performance Embedded Systems, l'auteur propose une revue complète des périphériques FPGA, des langages d'implémentation et du processus de développement FPGA, ainsi qu'une procédure détaillée sur la façon de commencer à implémenter des FPGA dans votre propre conception. L'extrait complet est présenté dans la série de fascicules suivante :

1 :Ressources matérielles

2 :Langages d'implémentation (cet article)

3 :Processus de développement

4 :Construire un projet

5 :Implémentation

Adapté de Architecting High-Performance Embedded Systems, par Jim Ledin.

Langages d'implémentation FPGA

La mise en œuvre d'une conception pour un FPGA revient finalement à utiliser un ou plusieurs langages de type programmation logicielle pour définir les fonctionnalités de l'appareil.

Les langages traditionnels utilisés pour le développement FPGA sont VHDL et Verilog.

Les outils de développement FPGA de la génération actuelle prennent généralement en charge ces deux langages, ainsi que la possibilité de définir des configurations système à l'aide de techniques de schéma fonctionnel. Certaines suites d'outils prennent également en charge la définition des fonctionnalités FPGA à l'aide des langages de programmation traditionnels C et C++.

VHDL

Langage de description du matériel VHSIC (VHDL ), où VHSIC signifie Très Circuit intégré à grande vitesse , a une syntaxe qui rappelle le langage de programmation Ada. VHDL a été développé sous la direction du département américain de la Défense à partir de 1983.

Comme Ada, le VHDL a tendance à être assez verbeux et structuré de manière rigide. En termes de langage de programmation, VHDL est fortement typé. Le langage contient un ensemble prédéfini de types de données de base, principalement booléen, bit, bit_vector, caractère, chaîne, entier, réel, temps et tableau. Tous les autres types de données sont définis en termes de types de base.

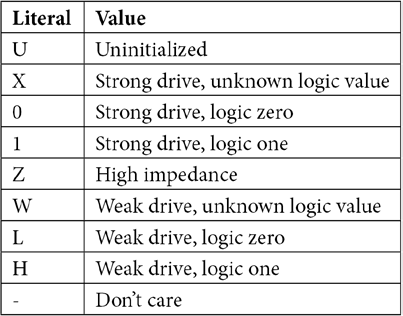

Un ensemble de bibliothèques VHDL a été défini par l'Institute of Electrical and Electronics Engineers (IEEE ) et formalisé en tant que norme IEEE 1164, Multivalue Logic System for Interopérabilité du modèle VHDL . Ces bibliothèques définissent l'ensemble des valeurs logiques à utiliser dans le langage VHDL. Cette bibliothèque comprend un type nommé std_logic, qui représente un signal à 1 bit. Les valeurs logiques dans le type std_logic sont représentées par les caractères littéraux indiqués dans le tableau suivant :

Les valeurs "fortes" 0 et 1 dans la figure précédente représentent des signaux conduits à l'état binaire spécifié. Les signaux "faibles" représentent des signaux conduits sur un bus avec plusieurs pilotes où n'importe quel pilote peut s'affirmer sur le bus, supplantant les autres pilotes. La valeur Z représente une sortie CMOS dans l'état à haute impédance, où plutôt que de conduire le bus à un état 0 ou 1, la sortie est à la place effectivement déconnectée du bus et ne le pilote pas du tout. L'état U représente les valeurs par défaut pour tous les signaux. Lors de la simulation de circuit, tout signal à l'état U sera détecté, ce qui indique probablement qu'une valeur non initialisée est utilisée par inadvertance. L'état X est associé à des fils qui n'ont aucune sortie qui les pilote. L'état - représente les entrées qui ne sont pas utilisées, et donc peu importe dans quel état elles se trouvent.

Les conceptions de circuits VHDL commencent généralement par importer les bibliothèques IEEE 1164 via les instructions suivantes :

bibliothèque IEEE ;

utilisez IEEE.std_logic_1164.all ;

Nous utiliserons VHDL dans notre exemple de projet plus loin dans le chapitre. Ceci n'est pas destiné à représenter une forte préférence pour le VHDL par rapport à Verilog. Les deux langages de définition de matériel sont entièrement capables de représenter pratiquement n'importe quelle conception pouvant être synthétisée pour un FPGA.

Verilog

Le langage de description du matériel de Verilog (HDL ) a été introduit en 1984 et est devenu normalisé comme IEEE 1364 en 2005. En 2009, la norme Verilog a été combinée avec le SystemVerilog norme pour produire la norme IEEE 1800-2009. SystemVerilog contient de nombreuses fonctionnalités pour effectuer la vérification du système, en plus des fonctionnalités de conception matérielle présentes dans Verilog.

Verilog a été conçu pour ressembler au langage de programmation C, y compris une priorité d'opérateur similaire et l'utilisation de certains des mêmes mots-clés de flux de contrôle, y compris if, else, for et while.

Verilog utilise le concept de fil pour représenter les états du signal. Une valeur de signal peut prendre n'importe laquelle des valeurs 0, 1, indifférent (x) ou haute impédance (z) et peut avoir une valeur forte ou faible force du signal.

VHDL et Verilog définissent tous deux des sous-ensembles de langage qui peuvent être utilisés pour concevoir des circuits logiques. Ces sous-ensembles sont appelés synthétisables sous-ensembles linguistiques. Des fonctionnalités de langage supplémentaires au-delà des sous-ensembles synthétisables sont disponibles pour prendre en charge des tâches telles que la simulation de circuit. Nous en verrons un exemple plus loin dans ce chapitre.

Les constructions de langage non synthétisables ont tendance à se comporter davantage comme les langages de programmation de logiciels traditionnels. Par exemple, une boucle for non synthétisable parcourt un bloc de code de manière séquentielle le nombre de fois spécifié, tout comme dans un langage de programmation normal. Une boucle for synthétisable, en revanche, se déroule efficacement pour générer une collection de constructions matérielles répliquées qui s'exécutent en parallèle représentant chaque itération de la boucle.

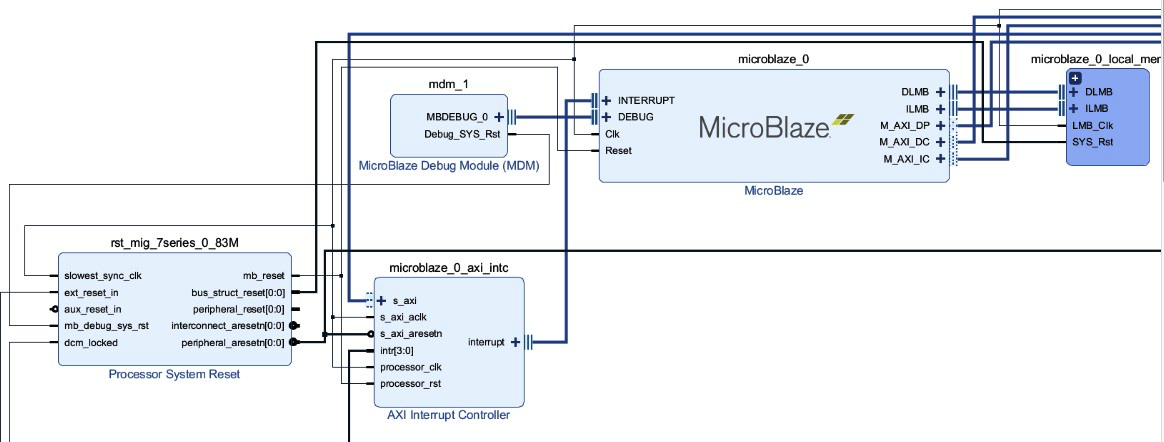

Schémas fonctionnels

À un niveau d'abstraction supérieur aux HDL textuels, les suites d'outils de développement FPGA modernes prennent en charge la configuration rapide de conceptions de systèmes incorporant des composants logiques complexes tels que des microprocesseurs et des périphériques d'E/S sophistiqués utilisant un format de structure de bloc. Figure 4.2 est un exemple d'une partie d'un schéma fonctionnel pour une conception de FPGA Xilinx incorporant un processeur logiciel MicroBlaze :

cliquez pour l'image en taille réelle

Figure 4.2 – Schéma fonctionnel contenant un microprocesseur logiciel MicroBlaze

Le processeur MicroBlaze est un cœur de processeur fourni avec la suite d'outils Xilinx Vivado pour une utilisation dans les conceptions FPGA dans les familles de processeurs, y compris l'Artix-7.

Bien que l'utilisation de schémas fonctionnels offre un moyen visuellement intuitif d'organiser l'instanciation et l'interconnexion d'éléments logiques complexes dans une conception FPGA, il est important de se rappeler que derrière le schéma, l'outil de développement génère du code VHDL ou Verilog pour définir les composants et leurs Connexions. Le schéma fonctionnel est simplement une interface utilisateur pour gérer la configuration de ces composants.

Après avoir développé un diagramme, vous pouvez examiner le code HDL généré, qui sera contenu dans les fichiers associés au projet. Dans le schéma de la Figure 4.2 , un fichier nommé design_1_microblaze_0_0_stub.vhdl est produit à partir du diagramme. Ce fichier commence par le code VHDL suivant :

bibliothèque IEEE ;

utiliser IEEE.STD_LOGIC_1164.ALL ;

la conception de l'entité_1_microblaze_0_0 est

Port (

Clk :dans STD_LOGIC ;

Réinitialiser :dans STD_LOGIC ;

Interruption :dans STD_LOGIC ;

Interrupt_Address :dans STD_LOGIC_VECTOR (0 à 31 );

Interrupt_Ack :out STD_LOGIC_VECTOR (0 à 1 );

Instr_Addr :out STD_LOGIC_VECTOR (0 à 31 );

Instr :dans STD_LOGIC_VECTOR (0 à 31 );

Ce code commence par une référence à la bibliothèque standard IEEE 1164, puis définit une interface avec le processeur MicroBlaze qui expose les signaux que vous attendez d'un microprocesseur, y compris l'horloge système, la réinitialisation, la demande d'interruption et les entrées vectorielles d'interruption ; les sorties d'accusé de réception d'interruption et d'adresse d'instruction ; et un bus pour les instructions récupérées en mémoire.

Ce code utilise les types de données de la bibliothèque IEEE 1164 pour les signaux à un seul bit (STD_LOGIC) et pour les signaux de bus à plusieurs bits (STD_LOGIC_VECTOR).

Le code dans la liste définit l'interface avec le processeur MicroBlaze, mais il ne contient pas la définition HDL du processeur lui-même. Les conceptions HDL complexes pour les composants tels que les microprocesseurs sont considérées comme précieuses Propriété Intellectuelle (IP ) et les entités commerciales qui développent ces conceptions prennent souvent des mesures pour s'assurer qu'elles ne sont pas utilisées sans licence appropriée. Lorsque les fournisseurs distribuent la propriété intellectuelle à l'usage de leurs clients, celle-ci peut être fournie dans un format compilé qui est opaque pour les utilisateurs finaux. Cela permet aux utilisateurs d'incorporer l'IP dans leurs conceptions, mais ils ne peuvent pas examiner le HDL utilisé pour le développer. Ceci est conceptuellement similaire aux développeurs de logiciels qui publient une bibliothèque sous forme compilée mais ne fournissent pas le code source.

C/C++

Un certain nombre de fournisseurs proposent des outils logiciels qui traduisent les langages de programmation traditionnels de haut niveau, souvent C et C++, en code HDL à utiliser dans le développement FPGA. Cette approche peut être intéressante si vous avez un algorithme complexe en C ou C++ que vous souhaitez accélérer dans une implémentation FPGA. Ces outils permettent également aux développeurs de logiciels familiarisés avec C/C++ de commencer immédiatement à implémenter du code pour une utilisation FPGA sans avoir besoin d'apprendre l'un des HDL.

Alors que les outils de développement FPGA pour ces langages de haut niveau sont capables d'optimiser considérablement l'implémentation FPGA résultante de l'algorithme de code C/C++, il y a toujours une certaine déconnexion dans la mesure où le modèle d'exécution C/C++ implique l'exécution séquentielle d'instructions tout en l'environnement FPGA natif se compose de composants matériels parallèles. La conception FPGA résultant du code C/C++ ressemble généralement à une collection de machines à états qui gèrent l'exécution séquentielle des opérations définies dans les instructions du langage de programmation. Selon la disponibilité des opportunités d'exécution parallèle dans le code C/C++, une implémentation FPGA peut fournir une amélioration significative des performances par rapport à l'exécution du même code sur un processeur traditionnel.

Dans les suites d'outils de développement FPGA modernes, toutes les méthodes d'implémentation FPGA décrites dans cette section (VHDL, Verilog, diagrammes et C/C++) peuvent être combinées dans une seule conception, si nécessaire. Pour cette raison, un membre de l'équipe peut préférer travailler en VHDL tandis qu'un autre utilise Verilog. Il peut y avoir des raisons de gestion de projet pour décourager l'utilisation du multi-HDL au sein d'un même projet, mais les langages eux-mêmes fonctionnent ensemble dans une même conception sans problème. L'une des raisons pour lesquelles un chef de projet peut souhaiter éviter l'utilisation de plusieurs HDL est que le maintien futur de l'effort nécessitera la participation de développeurs possédant des compétences dans les deux langues.

De même, il est possible de définir une architecture de haut niveau pour un projet en termes de schéma fonctionnel, puis de mettre en œuvre des fonctionnalités de sous-système détaillées à l'aide du HDL de son choix. Dans la même conception, il est également possible d'intégrer du HDL généré à partir d'un algorithme C/C++. Les architectes et développeurs de systèmes embarqués doivent examiner attentivement les implications et sélectionner la méthode de mise en œuvre appropriée pour chaque partie d'une conception FPGA.

La section suivante présentera les étapes du processus de développement FPGA standard.

Réimprimé avec la permission de Packt Publishing. Copyright © 2021 Édition Packt

Jim Ledin est le PDG de Ledin Engineering, Inc. Jim est un expert en conception, développement et test de logiciels et de matériel embarqués. Il est également accompli dans l'évaluation de la cybersécurité des systèmes embarqués et les tests d'intrusion. Il a un B.S. diplôme en génie aérospatial de l'Iowa State University et un M.S. diplôme en génie électrique et informatique du Georgia Institute of Technology. Jim est un ingénieur électricien professionnel enregistré en Californie, un professionnel certifié de la sécurité des systèmes d'information (CISSP), un hacker éthique certifié (CEH) et un testeur de pénétration certifié (CPT).

Jim Ledin est le PDG de Ledin Engineering, Inc. Jim est un expert en conception, développement et test de logiciels et de matériel embarqués. Il est également accompli dans l'évaluation de la cybersécurité des systèmes embarqués et les tests d'intrusion. Il a un B.S. diplôme en génie aérospatial de l'Iowa State University et un M.S. diplôme en génie électrique et informatique du Georgia Institute of Technology. Jim est un ingénieur électricien professionnel enregistré en Californie, un professionnel certifié de la sécurité des systèmes d'information (CISSP), un hacker éthique certifié (CEH) et un testeur de pénétration certifié (CPT). Contenus associés :

- Conception embarquée avec FPGA :ressources matérielles

- Les outils open source aident à simplifier la programmation FPGA

- Implémentation d'algorithmes à virgule flottante dans les FPGA ou les ASIC

- Les outils logiciels migrent le code GPU vers les FPGA pour les applications d'IA

- Les FPGA remplacent les ASIC dans les ADAS basés sur la vision Subaru Eyesight

- Comment les FPGA Flash simplifient les exigences de sécurité fonctionnelle

- Tirer parti des avantages des FPGA instantanés

- Configuration FPGA utilisant un flash NOR haute vitesse

- Comment la technologie FPGA évolue pour répondre aux nouvelles exigences système de milieu de gamme

Pour plus d'informations sur Embedded, abonnez-vous à la newsletter hebdomadaire d'Embedded.

Embarqué

- Qu'est-ce que la programmation système embarquée et ses langages

- Qu'est-ce que la conception de systèmes embarqués :étapes du processus de conception

- Transformer le Big Data en Smart Data avec l'IA intégrée

- Défis de mise en œuvre du port USB Type-C et solutions de conception

- Les tendances clés du secteur façonnent la conception intégrée

- Clienttron :TPV multifonction avec imprimante intégrée

- Kit de conception mesure la tension artérielle avec capteur optique

- Débuts de FPGA de niveau défense avec accès anticipé

- Tout compris avec additif