Comment créer un processus cadencé en VHDL

La grande majorité des conceptions VHDL utilise la logique cadencée , également appelée logique synchrone ou logique séquentielle . Un processus cadencé est déclenché uniquement par un signal d'horloge maître, pas lorsque l'un des autres signaux d'entrée change.

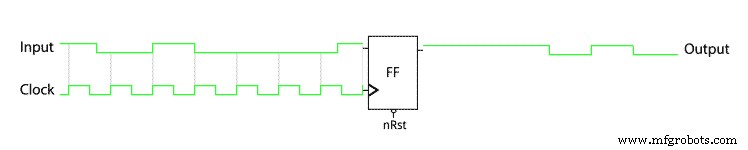

Le bloc de construction de base de la logique cadencée est un composant appelé flip-flop . Il en existe différentes variantes, et dans ce didacticiel, nous allons nous concentrer sur la bascule déclenchée par front positif avec réinitialisation négative :

La bascule est un circuit échantillonneur-bloqueur, ce qui signifie qu'elle copie la valeur de l'entrée vers la sortie lorsque le front montant du signal d'horloge arrive. La sortie est ensuite maintenue stable à la valeur échantillonnée jusqu'au front montant suivant de l'horloge ou jusqu'à ce que le signal de réinitialisation soit pulsé.

Cet article de blog fait partie de la série de didacticiels VHDL de base.

Tous les processus cadencés sont déclenchés simultanément et liront leurs entrées en même temps. En même temps, ils sortiront les résultats de la dernière itération. Le signal d'horloge crée effectivement des pas de temps dans le flux de données. Cela permet au concepteur de créer une logique complexe et profonde. Il ou elle peut décomposer les actions de l'algorithme en événements qui se produisent sur les cycles d'horloge.

Les bascules ou les tableaux de bascules sont parfois appelés registres , c'est la même chose.

La liste de sensibilité pour les processus cadencés ne contient généralement que le signal d'horloge. En effet, un processus cadencé n'est déclenché que par un flanc sur le signal d'horloge, les autres signaux d'entrée ne le réveilleront pas du tout.

Voici un modèle pour créer un processus cadencé avec réinitialisation synchrone :process(Clk) is

begin

if rising_edge(Clk) then

if nRst = '0' then

<reset all output signals here>

else

<main logic here>

end if;

end if;

end process;

Exercice

Dans ce didacticiel vidéo, nous allons apprendre à créer un processus cadencé en VHDL :

Le code final pour la bascule testbench :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T17_ClockedProcessTb is

end entity;

architecture sim of T17_ClockedProcessTb is

constant ClockFrequency : integer := 100e6; -- 100 MHz

constant ClockPeriod : time := 1000 ms / ClockFrequency;

signal Clk : std_logic := '1';

signal nRst : std_logic := '0';

signal Input : std_logic := '0';

signal Output : std_logic;

begin

-- The Device Under Test (DUT)

i_FlipFlop : entity work.T17_FlipFlop(rtl)

port map(

Clk => Clk,

nRst => nRst,

Input => Input,

Output => Output);

-- Process for generating the clock

Clk <= not Clk after ClockPeriod / 2;

-- Testbench sequence

process is

begin

-- Take the DUT out of reset

nRst <= '1';

wait for 20 ns;

Input <= '1';

wait for 22 ns;

Input <= '0';

wait for 6 ns;

Input <= '1';

wait for 20 ns;

-- Reset the DUT

nRst <= '0';

wait;

end process;

end architecture;

Le code final pour le module de la bascule :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T17_FlipFlop is

port(

Clk : in std_logic;

nRst : in std_logic; -- Negative reset

Input : in std_logic;

Output : out std_logic);

end entity;

architecture rtl of T17_FlipFlop is

begin

-- Flip-flop with synchronized reset

process(Clk) is

begin

if rising_edge(Clk) then

if nRst = '0' then

Output <= '0';

else

Output <= Input;

end if;

end if;

end process;

end architecture;

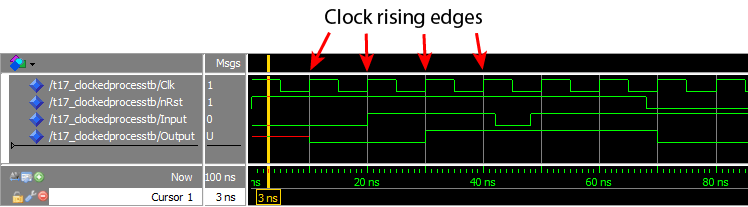

La fenêtre de forme d'onde dans ModelSim après avoir appuyé sur run et zoomé sur la timeline :

Analyse

Nous pouvons voir sur la forme d'onde que le signal de sortie n'est mis à jour qu'à chaque front montant du signal d'horloge. Le signal d'entrée est échantillonné uniquement lorsque le signal d'horloge passe de « 0 » à « 1 ». Le creux négatif du signal d'entrée commençant à environ 45 ns est complètement perdu. Il n'est pas copié sur la sortie car il se situe entre deux fronts montants de l'horloge et est donc ignoré.

Cette animation illustre comment la sortie réagit aux changements de signaux d'entrée et d'horloge :

Les lignes verticales indiquent comment le signal d'entrée est relatif aux fronts montants de l'horloge.

Portez une attention particulière à la seule impulsion positive sur le signal d'entrée à partir de 20 ns. Il est synchrone à l'horloge et dure exactement une période d'horloge. La sortie ne réagit pas instantanément, elle est retardée d'une période d'horloge.

Quand j'apprenais le VHDL, j'ai trouvé cela particulièrement difficile à comprendre. Le front montant de l'horloge est synchrone avec le front montant de l'entrée, alors comment la bascule peut-elle choisir l'une ou l'autre valeur ?

Le simulateur utilise des pas de temps pour modéliser les événements de manière prévisible et les signaux se propagent en un temps zéro. Étant donné que la bascule lit l'entrée exactement au même pas de temps qu'elle met à jour la sortie, elle voit l'ancienne valeur de l'entrée et la copie dans la sortie.

En savoir plus sur les pas de temps VHDL ici :les cycles delta expliqués

Je devrais ajouter à cette réponse que ce n'est pas vraiment Comment ça fonctionne. Dans le monde physique, un signal a besoin de temps pour se propager, on ne sait pas exactement quand il arrive à la bascule. Ces délais de propagation sont estimés automatiquement pour nous par le processus logiciel (place et route) qui convertit le code VHDL en une netlist.

En réalité, l'entrée doit être maintenue stable pendant quelques nanosecondes avant et après le front montant de l'horloge :

Ces périodes de temps critiques sont appelées temps d'installation et de maintien. Heureusement, ce n'est pas quelque chose que vous devez normalement prendre en considération. Lorsque vous travaillez uniquement avec une logique cadencée, ces problèmes sont gérés par le logiciel qui transforme le code VHDL en une netlist.

À emporter

- Les processus cadencés avec réinitialisation synchronisée n'ont que le signal d'horloge sur la liste de sensibilité

- Le

if rising_edge(Clk)garantit que le processus ne se réveille que sur les fronts montants de l'horloge - Dans une conception synchrone, les choses ne se produisent que sur le front d'horloge actif

Répondez au Quiz VHDL de base – partie 3 »

ou

Passez au tutoriel suivant »

VHDL

- Comment créer une liste de chaînes en VHDL

- Comment créer un banc d'essai piloté par Tcl pour un module de verrouillage de code VHDL

- Comment arrêter la simulation dans un testbench VHDL

- Comment créer un contrôleur PWM en VHDL

- Comment générer des nombres aléatoires en VHDL

- Comment créer un tampon circulaire FIFO en VHDL

- Comment créer un banc d'essai d'auto-vérification

- Comment créer une liste chaînée en VHDL

- Comment utiliser une procédure dans un processus en VHDL