Variables - Exemple VHDL

Les variables en VHDL agissent de la même manière que les variables en C. Leur valeur est valide à l'emplacement exact dans le code où la variable est modifiée. Ainsi, si un signal utilise la valeur de la variable avant l'affectation, elle aura l'ancienne valeur de variable. Si un signal utilise la valeur de la variable après l'affectation, il aura la nouvelle valeur de variable.

Règles de variables :

- Les variables ne peuvent être utilisées qu'à l'intérieur des processus

- Toute variable créée dans un processus ne peut pas être utilisée dans un autre processus

- Les variables doivent être définies après le mot-clé process mais avant le mot clé begin

- Les variables sont affectées à l'aide de := symbole d'affectation

- Les variables affectées prennent immédiatement la valeur de l'affectation

La chose la plus importante à comprendre est que les variables prennent immédiatement la valeur de leur affectation. Voici un exemple qui montre une façon utile d'utiliser des variables :stocker des données pour une utilisation temporaire . Il utilise une instruction case et l'opérateur de concaténation esperluette (&).

VAR_CASE : process (i_clk)

variable v_Choices : std_logic_vector(1 downto 0);

begin

v_Choices := i_select_1 & i_select_2; -- concatenation

case v_Choices is

when "00" =>

o_data <= "0001";

when "01" =>

o_data <= "0010";

-- ETC

Dans l'exemple précédent, nous avons concaténé les deux signaux afin qu'ils puissent être utilisés dans l'instruction case. La variable v_Choices était immédiatement utilisable dès qu'elle était assignée. Prenons un autre exemple. L'exemple ci-dessous est plus complet et montre comment les variables prennent immédiatement la valeur de leur affectation. Les signaux r_Var_Copy1 et r_Var_Copy2 semblent être les mêmes, mais r_Var_Copy2 ne peut jamais atteindre 5 avant d'être réinitialisé.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity variable_ex is

port (

i_clk : in std_logic;

o_done : out std_logic

);

end variable_ex;

architecture rtl of variable_ex is

signal r_Done : std_logic := '0';

signal r_Var_Copy1 : natural range 0 to 5 := 0;

signal r_Var_Copy2 : natural range 0 to 5 := 0;

begin

EX_VAR : process (i_clk)

variable v_Count : natural range 0 to 5 := 0;

begin

if rising_edge(i_clk) then

v_Count := v_Count + 1;

r_Var_Copy1 <= v_Count;

if v_Count = 5 then

r_Done <= '1';

v_Count := 0;

else

r_Done <= '0';

end if;

r_Var_Copy2 <= v_Count;

end if;

end process EX_VAR;

o_done <= r_Done;

end rtl;

Afin de simuler notre conception, nous devons créer un banc de test. De plus, les variables peuvent être un peu difficiles à afficher dans la simulation. Si vous utilisez Modelsim, découvrez comment afficher vos variables dans la fenêtre de forme d'onde de Modelsim.

Banc de test :

library ieee;

use ieee.std_logic_1164.all;

entity variable_ex_tb is

end variable_ex_tb;

architecture behave of variable_ex_tb is

component variable_ex

port (

i_clk : in std_logic;

o_done : out std_logic

);

end component variable_ex;

constant c_CLK_PERIOD : time := 10 ns;

signal r_CLK : std_logic := '0';

signal w_DONE : std_logic;

begin

UUT : variable_ex

port map (

i_clk => r_CLK,

o_done => w_DONE

);

r_CLK <= not r_CLK after c_CLK_PERIOD/2;

end behave;

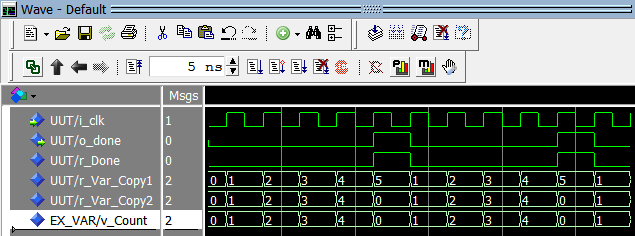

Variables Exemple Testbench Waveform

Variables Exemple Testbench Waveform L'exemple ci-dessus montre comment les variables agissent différemment des signaux. Les signaux r_Var_Copy1 et r_Var_Copy2 semblent être les mêmes, mais r_Var_Copy2 ne peut jamais atteindre 5 avant d'être réinitialisé.

VHDL

- Instruction de procédure - Exemple VHDL

- Enregistrements - Exemple VHDL

- Options d'analyse

- Variables C# et types de données (primitifs)

- Variables, littéraux et constantes C++

- C Variables, constantes et littéraux

- Classe de stockage C

- Chaînes en C :comment déclarer une variable, initialiser, imprimer, exemple

- Java - Types de variables