Tutoriel - Introduction au VHDL

VHDL est un acronyme horrible. Il signifie V HSIC H matériel informatique D description L langue. Un acronyme dans un acronyme, génial ! VHSIC signifie V très H haut S j'ai fait pipi C intégré circuit. Par conséquent, VHDL étendu est V Circuit intégré à très grande vitesse H matériel informatique D description L langue. OUF c'est une bouchée. VHDL est l'un des deux langages utilisés par l'éducation et les entreprises pour concevoir des FPGA et des ASIC. Vous pourriez d'abord bénéficier d'une introduction aux FPGA et aux ASIC si vous n'êtes pas familier avec ces circuits fascinants. VHDL et Verilog sont les deux langages utilisés par les concepteurs numériques pour décrire leurs circuits, et ils sont différents de par leur conception de vos langages logiciels traditionnels tels que C et Java.

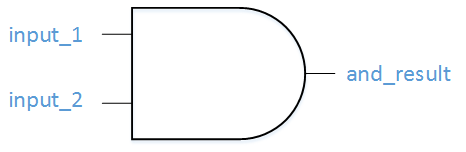

Pour l'exemple ci-dessous, nous allons créer un fichier VHDL qui décrit une porte Et. Pour rappel, une simple porte And a deux entrées et une sortie. La sortie est égale à 1 uniquement lorsque les deux entrées sont égales à 1. Vous trouverez ci-dessous une image de la porte ET que nous allons décrire avec VHDL.

Une porte et

Une porte et Allons-y ! L'unité fondamentale de VHDL est appelée un signal . Pour l'instant, supposons qu'un signal peut être un 0 ou un 1 (il existe en fait d'autres possibilités, mais nous y reviendrons). Voici une logique VHDL de base :

signal and_gate : std_logic; and_gate <= input_1 and input_2;

La première ligne de code définit un signal de type std_logic et il est appelé and_gate. Std_logic est le type le plus couramment utilisé pour définir les signaux, mais il y en a d'autres que vous découvrirez. Ce code va générer une porte ET avec une seule sortie (and_gate) et 2 entrées (input_1 et input_2). Le mot clé "et" est réservé en VHDL. L'opérateur <=est appelé opérateur d'affectation. Lorsque vous analysez verbalement le code ci-dessus, vous pouvez dire à voix haute :"Le signal and_gate GETS input_1 and-ed with input_2".

Maintenant, vous vous demandez peut-être d'où viennent input_1 et input_2. Eh bien, comme leur nom l'indique, ce sont des entrées de ce fichier, vous devez donc en informer les outils. Les entrées et les sorties d'un fichier sont définies dans une entité . Une entité contient un port qui définit toutes les entrées et sorties d'un fichier. Créons une entité simple :

entity example_and is

port (

input_1 : in std_logic;

input_2 : in std_logic;

and_result : out std_logic

);

end example_and;

C'est votre entité de base. Il définit une entité appelée example_and et 3 signaux, 2 entrées et 1 sortie, qui sont tous de type std_logic. Un autre mot-clé VHDL est nécessaire pour que cela soit complet et c'est architecture . Une architecture est utilisée pour décrire la fonctionnalité d'une entité particulière. Pensez-y à un mémoire :l'entité est la table des matières et l'architecture est le contenu. Créons une architecture pour cette entité :

architecture rtl of example_and is signal and_gate : std_logic; begin and_gate <= input_1 and input_2; and_result <= and_gate; end rtl;

Le code ci-dessus définit une architecture appelée rtl de l'entité example_and. Tous les signaux utilisés par l'architecture doivent être définis entre les mots clés "is" et "begin". La logique de l'architecture réelle se situe entre les mots-clés "begin" et "end". Vous avez presque terminé avec ce fichier. Une dernière chose que vous devez indiquer aux outils est la bibliothèque à utiliser. Une bibliothèque définit le comportement de certains mots-clés dans votre fichier. Pour l'instant, tenez pour acquis que vous devez avoir ces 2 lignes en haut de votre fichier :

library ieee; use ieee.std_logic_1164.all;

Toutes nos félicitations! Vous avez créé votre premier fichier VHDL. Vous pouvez voir le fichier complet ici :

library ieee;

use ieee.std_logic_1164.all;

entity example_and is

port (

input_1 : in std_logic;

input_2 : in std_logic;

and_result : out std_logic

);

end example_and;

architecture rtl of example_and is

signal and_gate : std_logic;

begin

and_gate <= input_1 and input_2;

and_result <= and_gate;

end rtl;

Vous semble-t-il que vous avez dû écrire beaucoup de code juste pour créer une porte stupide et ? Tout d'abord, et les portes ne sont pas stupides. Deuxièmement, vous avez raison; Le VHDL est un langage très verbeux. Habituez-vous au fait que faire quelque chose qui était très simple dans un logiciel vous prendra beaucoup plus de temps dans un HDL tel que Verilog ou VHDL. Mais demandez simplement à un logiciel d'essayer de générer une image sur un moniteur VGA qui affiche le jeu de la vie de Conway et regardez leur tête tourner d'étonnement ! Au fait, cette vidéo est créée avec VHDL et un FPGA. Vous pourrez le faire bien assez tôt !

VHDL