Premiers pas avec Verilog Hardware Description Language

Dans cet article, nous étudierons la structure de base d'un module Verilog, examinerons quelques exemples d'utilisation du type de données Verilog « wire » et ses forme vectorielle, et abordez brièvement certaines différences entre VHDL et Verilog.

Dans cet article, nous étudierons la structure de base d'un module Verilog, examinerons quelques exemples d'utilisation du type de données Verilog « wire » et sa forme vectorielle, et aborderons brièvement certaines différences entre VHDL et Verilog.

Verilog et VHDL sont deux langages couramment utilisés pour décrire les circuits numériques. AAC propose une série d'articles techniques traitant des concepts de base du VHDL. Cet article fonctionne comme un point de départ pour notre série concernant Verilog.

Ai-je besoin à la fois de Verilog et de VHDL ?

Avant de commencer notre discussion, abordons une question évidente :avons-nous vraiment besoin de connaître ces deux langues ?

Verilog et VHDL sont tous deux des outils puissants qui peuvent être utilisés pour concevoir un circuit numérique complexe. Bien qu'il existe quelques différences entre ces deux HDL, vous êtes libre de choisir l'un ou l'autre à maîtriser et à utiliser. Cependant, je pense qu'à un moment donné, vous bénéficierez d'au moins une compréhension de base des deux langues. Parfois, en tant que concepteurs, nous avons besoin d'un exemple de segment de code pour nous faire une idée du codage d'un projet. Nous surfons sur le net pendant des heures et trouvons enfin ce dont nous avons besoin, mais cela n'a aucun sens pour nous - c'est écrit dans le HDL qui nous est complètement inconnu. Sans avoir une compréhension de base de la langue, nous ne pourrons peut-être pas comprendre pleinement les techniques.

Verilog Évolution

Verilog a été conçu au début de 1984 par Gateway Design Automation (environ trois ans après le lancement de VHDL par le département américain de la Défense). Avec la prise en charge du DoD, VHDL est devenu une norme IEEE en 1987. Verilog n'est entré en scène qu'en 1995. Aujourd'hui, VHDL et Verilog sont des HDL populaires et les outils de conception FPGA prennent généralement en charge les deux langages.

Le mot « Verilog » est un portemanteau des mots « vérification » et « logique » parce que le langage a d'abord été suggéré comme outil de simulation et de vérification. Commençons par les concepts et la syntaxe de Verilog.

Exemple 1

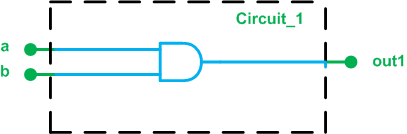

Comme premier exemple, écrivons le code Verilog pour le circuit représenté sur la figure 1.

Figure 1. Circuit_1

Il y a deux entrées et une sortie. Les ports sont tous un peu larges. La fonctionnalité du circuit consiste à ET les deux entrées et à mettre le résultat sur le port out1.

Une description Verilog possible pour le module Circuit_1 est :

Lignes 1 et 8

Ces deux lignes utilisent les mots clés « module » et « endmodule » pour spécifier que les lignes intermédiaires (lignes 2 à 7) décrivent toutes un circuit nommé « Circuit_1 ». Ce nom est arbitraire et permet de se référer ultérieurement à ce circuit.

Lignes 2 à 6

Ces lignes précisent l'interface du « Circuit_1 » avec son environnement environnant. Les ports d'entrée et de sortie sont décrits à l'aide des mots-clés « input » et « output ». Ces mots-clés sont suivis d'un autre mot-clé « wire » puis du nom du port (voir Figure 1). Que précise le mot-clé « fil » ? « Wire » est un type de données Verilog qui représente un fil physique dans la conception. Nous discuterons plus en détail des types de données Verilog dans un futur article, mais pour l'instant, nous savons qu'il y aurait trois fils appelés a, b et out1 dans notre module et puisque ceux-ci sont spécifiés dans la déclaration de port, ils correspondent à l'interface du module.

Ligne 7

Cette ligne utilise l'opérateur ET au niveau du bit, c'est-à-dire &, pour décrire la fonctionnalité du circuit. Le mot-clé « assign » place a&b sur le port de sortie out1. Ce type d'affectation est appelé affectation continue. On l'appelle ainsi parce que l'affectation est toujours active chaque fois qu'un opérande sur le côté droit change, a&b est évalué et affecté à out1. On peut imaginer une affectation continue comme un circuit combinatoire dont la sortie est continuellement mise à jour en fonction de ses entrées. Dans notre exemple, ce circuit combinatoire est une simple porte ET. Il existe également des tâches procédurales dans Verilog HDL qui seront discutées dans de futurs articles.

Maintenant, nous pouvons utiliser un progiciel tel que Xilinx ISE pour vérifier le code ci-dessus. Vous pouvez trouver un didacticiel basé sur Verilog de ce logiciel ici (PDF).

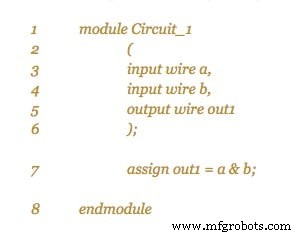

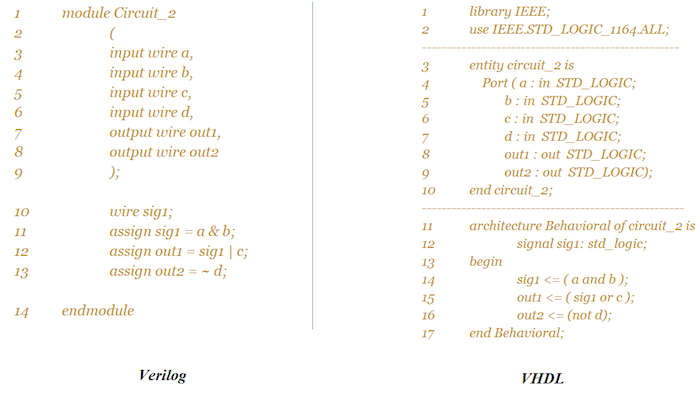

Comparaison de l'exemple 1 avec le code VHDL

La figure 2 ci-dessous montre les descriptions Verilog et VHDL pour le module Circuit_1.

Figure 2. Comparaison des descriptions Verilog et VHDL pour Circuit_1.

Comme vous pouvez le voir, nous devons inclure certaines bibliothèques lors du codage en VHDL. Ces bibliothèques donnent la définition des types de données et des opérateurs. Compte tenu de l'ajout de ces bibliothèques et du format général du VHDL, nous observons que le code VHDL est plus verbeux. Cependant, cette verbosité n'est pas sans avantages. Par exemple, la fonction de gestion de bibliothèque de VHDL peut être utile lors de la modélisation de systèmes de niveau supérieur. Dans les prochains articles, nous discuterons occasionnellement des avantages et des inconvénients de ces deux HDL.

Verilog a un système à quatre valeurs

Il existe quatre valeurs de base utilisées dans la plupart des types de données Verilog. Les fils définis dans le listing 1 peuvent prendre l'une des valeurs suivantes :

- 0 :pour un niveau logique bas ou une fausse condition

- 1 :pour une condition logique haute ou vraie

- z :pour l'état haute impédance (peut être utilisé pour décrire la sortie d'un tampon à trois états)

- x :pour une valeur indifférente ou inconnue (lorsqu'une entrée n'est pas initialisée ou qu'au moins deux sorties en conflit sont connectées ensemble).

Le type de données VHDL std_logic peut prendre neuf valeurs différentes, mais ses valeurs couramment utilisées sont « 0 », « 1 », « Z » et « - » (« - » indique une indifférente).

Exemple 2

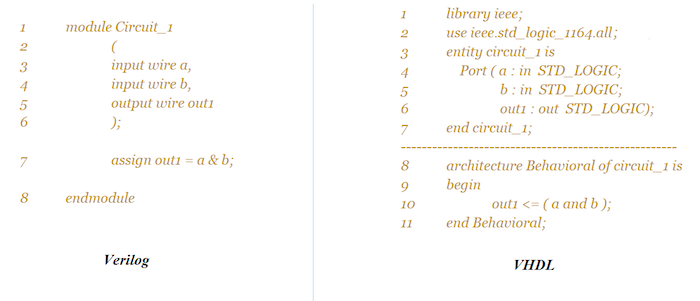

Comme autre exemple, écrivons le code Verilog pour le circuit (que nous appellerons Circuit_2) illustré à la figure 3.

Figure 3. Circuit_2

Le code Verilog suivant décrit ce circuit :

Les éléments utilisés dans le code ci-dessus sont similaires à ceux de l'exemple 1, sauf qu'un signal interne est défini à la ligne 10 du code. Le mot-clé « wire » permet de spécifier le type de données de cette connexion. Comme indiqué ci-dessus, le type de données « fil » se traduirait par un fil physique dans la conception.

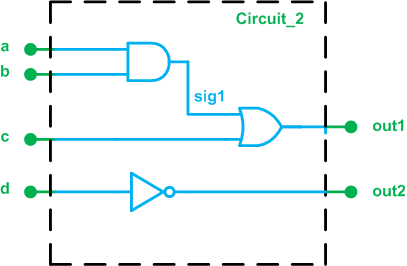

Le code ci-dessus utilise également de nouveaux opérateurs au niveau du bit Verilog :~ pour NOT et | pour opération OU. Un autre opérateur au niveau du bit utile est ^ pour l'opération XOR. La figure 4 montre à la fois les descriptions Verilog et VHDL pour le module Circuit_2. De telles comparaisons peuvent vous aider à voir les différences et les similitudes entre ces deux langues.

Figure 4. Comparaison des descriptions Verilog et VHDL pour Circuit_2.

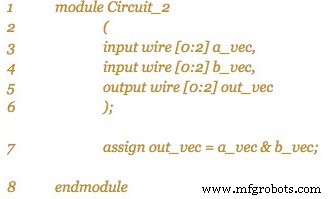

Exemple 3

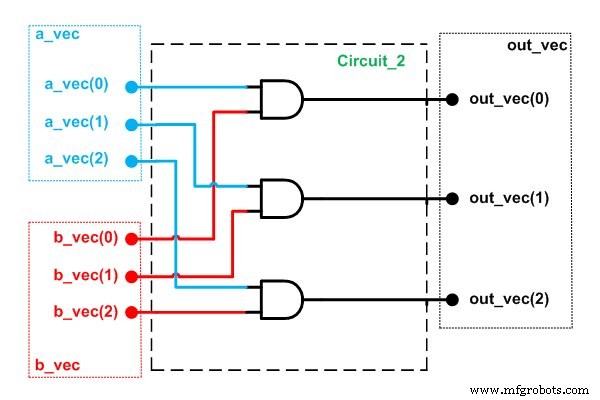

Pour notre troisième et dernier exemple, nous allons donner le code Verilog pour le schéma illustré à la figure 5.

Figure 5. Schéma par exemple 3.

Comme vous pouvez le voir, il existe une certaine relation entre les ports d'entrée bleus et les ports rouges :les entrées correspondantes sont combinées avec l'opérateur AND. Le résultat est affecté à un port de sortie. Dans de tels cas, nous pouvons regrouper les signaux et les traiter comme un vecteur. Cela rend le code compact et lisible.

En utilisant le concept de vecteur dans Verilog, nous pouvons facilement étendre le code du listing 1 pour décrire le circuit ci-dessus (voir le code du listing 3 ci-dessous).

Notez que la plage d'index des vecteurs peut être soit ascendante ([0:2] comme utilisé ci-dessus) soit descendante ([2:0]). Bien que le format ascendant soit utilisé ci-dessus, il est généralement moins sujet aux erreurs d'utiliser la forme descendante. Cela est dû au fait que le style descendant correspond à notre perception selon laquelle la position la plus à gauche d'un nombre binaire a l'indice le plus élevé. Notez que les vecteurs sont également utilisés en VHDL.

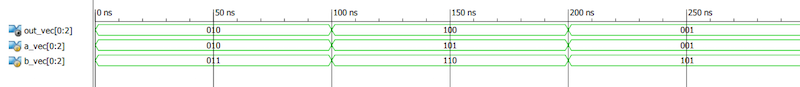

La figure 6 ci-dessous montre une simulation ISE du code dans la liste 3.

Figure 6. Simulation ISE du code de l'exemple 3.

Dans cet article, nous avons expliqué que c'était une bonne idée d'apprendre à la fois VHDL et Verilog, nous avons étudié la structure de base d'un module Verilog et nous nous sommes familiarisés avec le type de données Verilog « wire » et sa forme vectorielle. Nous avons également brièvement évoqué certaines différences entre VHDL et Verilog. Le prochain article de notre série Verilog traitera de la conception de circuits combinatoires dans Verilog.

Embarqué

- Conteneurs Code Ready :Premiers pas avec les outils d'automatisation des processus dans le cloud

- Initiation à l'impression 3D céramique

- Premiers pas avec TJBot

- Premiers pas avec le RAK 831 Lora Gateway et RPi3

- Premiers pas avec la passerelle LoRa RAK831 et RPi3

- Comment démarrer avec l'inférence IA en périphérie

- Premiers pas avec le groupe Eagle :ce que vous devez savoir

- Démarrer avec My.Cat.com

- Node-RED et démarrage avec Docker